يوم جيد عزيزي القارئ! طُلب مني أن أكتب عن UHCI - حسنًا ، أنا أكتب.

قد تجد هذه المقالة مفيدة إذا لم تكن لديك ، على سبيل المثال ، مهارات كتابة كافية لبرامج التشغيل وقراءة وثائق أحد الأجهزة. مثال بسيط: تريد كتابة نظام التشغيل الخاص بك لجهاز كمبيوتر صغير ، بحيث لا تقوم بعض أنظمة تشغيل Windows أو توزيعات Linux الأخرى بتنزيل الحديد ، وأنت تستخدم كل طاقتها حصريًا لأغراضك الخاصة.

ما هو UHCI؟

أعتقد أنه ، حتى لا ترش مرة أخرى حول موضوع ماذا ولماذا ، فقط اترك رابطًا لمقالتي السابقة حول EHCI.

كزة هناUHCI - تعمل واجهة وحدة تحكم المضيف العالمي كجهاز PCI ، ولكن بخلاف EHCI تستخدم المنافذ بدلاً من MMIO (Memory-Mapped-IO).

المصطلحات الواجب استخدامها فيما بعد

- برنامج تشغيل USB (USBD) - برنامج تشغيل USB نفسه

- HC (وحدة تحكم المضيف) - وحدة تحكم مضيف ، أو UHCI فقط

- برنامج تشغيل وحدة تحكم المضيف (HCD) - برنامج يقوم بتوصيل الأجهزة و USBD

- جهاز USB - جهاز USB نفسه

أنواع نقل البيانات

متزامن - الإرسال المتزامن ، الذي له تردد معين لنقل البيانات. يمكن استخدامه ، على سبيل المثال ، لميكروفونات USB ، إلخ.

المقاطعة - عمليات نقل البيانات الصغيرة والعفوية من الجهاز. يدعم نوع إرسال المقاطعة الأجهزة التي تتطلب فترة خدمة يمكن التنبؤ بها ولكنها لا توفر بالضرورة دفق بيانات يمكن التنبؤ به. يشيع استخدامه للأجهزة مثل لوحات المفاتيح وأجهزة التأشير التي قد لا توفر بيانات لفترات زمنية طويلة ، ولكنها تتطلب استجابة سريعة عندما يكون لديهم بيانات لإرسالها.

التحكم - نوع إرسال المعلومات حول حالة الجهاز وحالته وتكوينه. يتم استخدام نوع نقل التحكم لتوفير قناة تحكم من Host إلى أجهزة USB. تتكون إرسالات التحكم دائمًا من مرحلة الإعداد و صفر أو أكثر من مراحل البيانات متبوعة بمرحلة الحالة. من الضروري معالجة نقل التحكم إلى نقطة نهاية معينة في وضع FIFO. إذا تم تمرير التحكم إلى نفس نقطة النهاية ، فقد يؤدي التشذير إلى سلوك غير متوقع.

كتلة - نوع من نقل صفائف البيانات. تستخدم ، على سبيل المثال ، في أجهزة MassStorage.

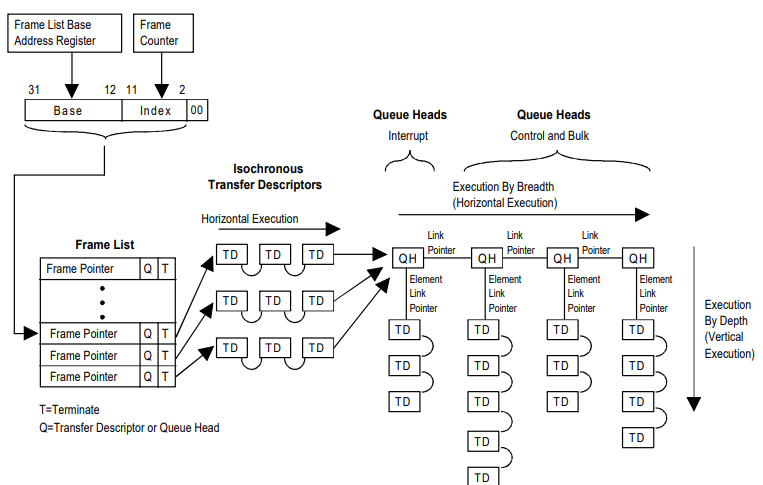

هذه هي الطريقة التي يبدو بها توزيع الوقت بمقدار 1 مللي ثانية - معالجة إطار واحد.

توزيع الوقت

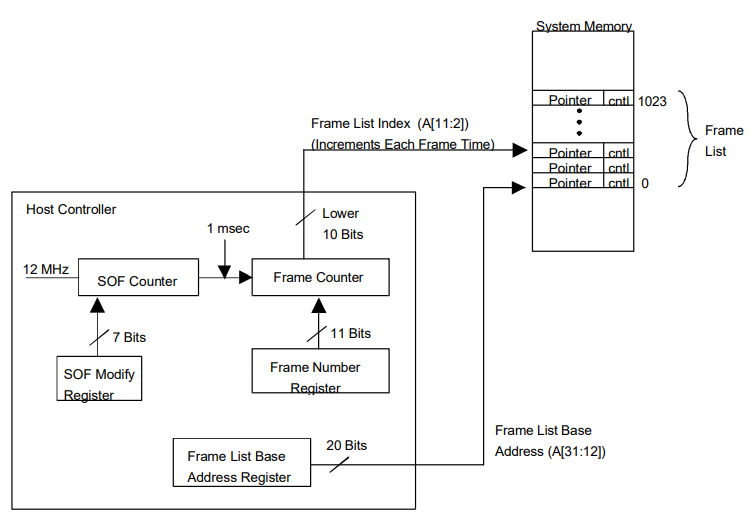

تدعم وحدة التحكم المضيفة تسليم البيانات في الوقت الفعلي عن طريق إنشاء حزمة Start Of Frame (SOF) كل 1 مللي ثانية. يتم إنشاء حزمة SOF عند انتهاء صلاحية عداد SOF في وحدة تحكم المضيف (الشكل 3). يقوم جهاز التحكم المضيف بتهيئة عداد SOF لمدة إطار 1 مللي ثانية. يمكن إجراء تغييرات بسيطة على هذه القيمة (وبالتالي الفترة الزمنية للإطار) من خلال برمجة سجل تغيير SOF. تسمح لك هذه الميزة بإجراء تغييرات طفيفة على الفترة الزمنية للإطار ، إذا لزم الأمر ، للحفاظ على التزامن في الوقت الحقيقي عبر نظام USB بالكامل.

تتضمن وحدة التحكم المضيفة رقم الإطار في كل حزمة SOF. يحدد رقم الإطار هذا بشكل فريد فترة الإطار في الوقت الفعلي. تحدث نهاية حالة الإطار (EOF) في نهاية الفترة الزمنية البالغة 1 مللي ثانية عندما يبدأ جهاز التحكم المضيف وقت الإطار التالي ، مما يؤدي إلى إنشاء حزمة SOF أخرى برقم الإطار المقابل. خلال فترة الإطار ، يتم إرسال البيانات كحزم معلومات. يتم فرض الفترة الزمنية للإطار بشكل صارم بواسطة وحدة تحكم المضيف ، ولا يمكن أن تتجاوز حزم البيانات في الإطار الحالي EOF (راجع الفصل 11 في مواصفات USB). تدعم وحدة التحكم المضيفة مزامنة إرسال البيانات بين الإطارات في الوقت الفعلي ، وربط رقم الإطار لإجراء إدخال محدد في قائمة الإطارات. يقوم عداد إطار وحدة تحكم المضيف بإنشاء رقم إطار (قيمة 11 بت) وإدراجه في كل حزمة SOF. يتم برمجة العداد من خلال السجلات وكل فترة إطار تزداد. يستخدم جهاز التحكم المضيف 10 بتات أقل من رقم الإطار كفهرس في قائمة الإطارات مع 1024 إطارًا ، والتي يتم تخزينها في ذاكرة النظام. وبالتالي ، نظرًا لأن عداد الإطار يتحكم في تحديد إدخال من قائمة الإطارات ، فإن وحدة تحكم المضيف تقوم بمعالجة كل إدخال في القائمة في فترة إطار معينة. يتم توسيع وحدة تحكم المضيف إلى الإدخال التالي في قائمة الإطارات لكل إطار جديد. وهذا يضمن تنفيذ عمليات الإرسال المتزامنة في إطار معين.

الشكل 3:

هيكل UHCI

كل شيء تمامًا كما هو الحال مع EHCI. طلبات مثال لـ HC:

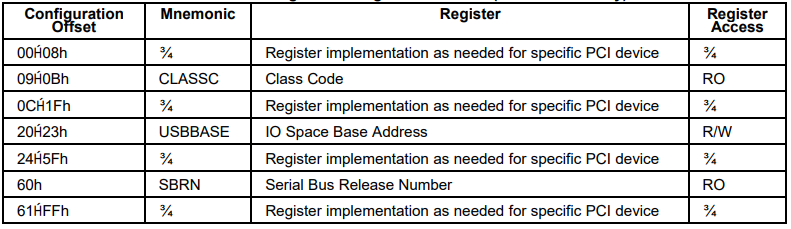

تكوين والوصول إلى UHCI

وهكذا ، كما قلت سابقًا ، تعمل UHCI من خلال المنافذ ، لذا من PCI نحتاج إلى معرفة قاعدة تسجيلات UHCI.

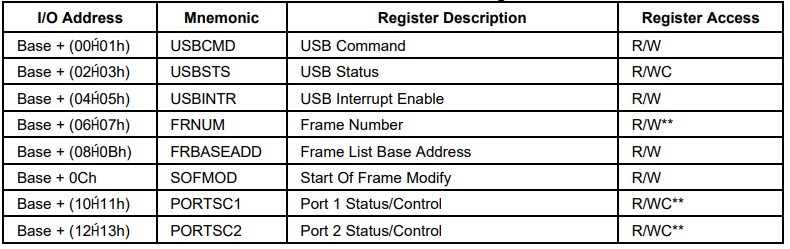

عند الإزاحة 0x20 هناك 4 بايت - قاعدة IO. فيما يتعلق بقاعدة الإدخال / الإخراج ، يمكننا استخدام السجلات التالية:

سجلات UHCI

- USBCMD هو سجل للتحكم في HC. البتات:

- Bit 6 هو علامة على أنه تم تكوين الجهاز وتهيئته بنجاح.

- بت 1 - إعادة تعيين HC. تعيين لإعادة HC.

- بت 0 - تشغيل / إيقاف. يعرض حالة HC. 1 - يعمل ، 0 - لا.

- USBSTS - تسجيل الحالة. البتات:

- بت 5 - توقف HC. حدث خطأ ، أو أكملت وحدة التحكم بنجاح إعادة تعيين HC.

- بت 4 - خطأ في عملية تحكم المضيف. يتم تعيين البت إلى 1 عند حدوث خطأ فادح ولا يمكن HC متابعة قائمة الانتظار و TD.

- بت 3 - خطأ في النظام المضيف. خطأ PCI.

- بت 1 - مقاطعة الخطأ. يشير إلى حدوث خطأ وتولد HC مقاطعة.

- بت 0 - المقاطعة. يشير إلى أن HC أدى إلى مقاطعة.

- USBINTR - تسجيل إعدادات المقاطعة. البتات:

- بت 2 - IOC - المقاطعة عند اكتمالها - تنشئ مقاطعة في نهاية المعاملة.

- FRNUM - رقم الإطار الحالي (خذ & 0x3FF للقيمة الصحيحة).

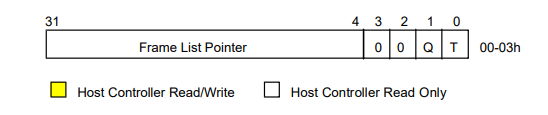

- FLBASEADD - العنوان الأساسي لقائمة الإطارات - عنوان قائمة الإطارات.

- PORTSC - حالة الميناء والتحكم فيه - سجل الحالة ومراقبة المنفذ. البتات:

- بت 9 - إعادة تعيين المنفذ - 1 - منفذ لإعادة التعيين.

- بت 8 - يشير إلى أن جهاز منخفض السرعة متصل بالمنفذ

- بت 3 - يشير إلى أن المنفذ في حالة تغير

- Bit 2 - يشير إلى ما إذا كان المنفذ ممكّنًا

- Bit 1 - يشير إلى أن حالة الجهاز متصلة بالمنفذ

- بت 0 - يشير إلى أن الجهاز متصل بالمنفذ.

الهياكل

مؤشر قائمة الإطارات

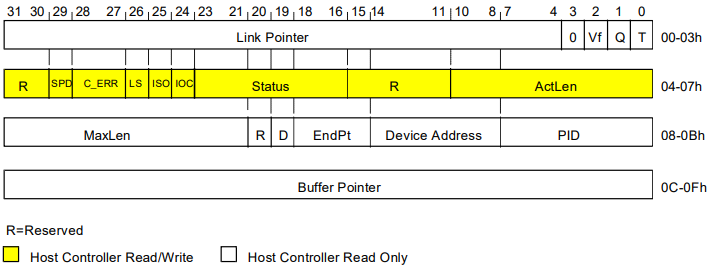

نقل واصف

TD التحكم وحالة

. البتات:

- بت 28-27 - عداد الخطأ ، على غرار EHCI.

- بت 26-1 = جهاز منخفض السرعة ، 0 = جهاز كامل السرعة.

- بت 25-1 = TD متزامن

- بت 24 - اللجنة الأولمبية الدولية

- بت 23-16 - الحالة:

- بت 23 - يشير إلى أنه TD نشط

- بت 22 - متوقف

- بت 21 - خطأ مخزن البيانات

- بت 20 - تم اكتشاف بابل

- بت 19 - NAK

- البتات 10–0: عدد وحدات البايت المرسلة بواسطة وحدة تحكم المضيف.

رمز TD

- بت 31:21 - ماكس باكيت لين ، على غرار EHCI

- بت 19 - تبديل البيانات ، على غرار EHCI

- بت 18:15 - رقم نقطة النهاية

- بت 18:14 - عنوان الجهاز

- بت 7: 0 - PID. In = 0x69 ، Out = 0xE1 ، الإعداد = 0x2D

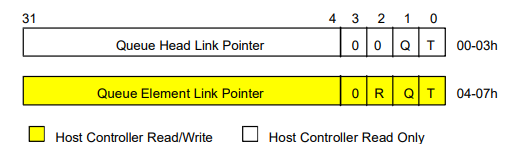

رأس الطابور

كود

تهيئة وتكوين HC:

PciBar bar; PciGetBar(&bar, id, 4); if (~bar.flags & PCI_BAR_IO) {

طلبات نقطة النهاية والتحكم: