تلقيت أمس رسالة من طالب في الصف العاشر من سيبيريا يريد أن يصبح مطورًا للمعالجات الدقيقة. لقد حصلت بالفعل على بعض النتائج في هذا المجال - لقد أضافت تعليمة الضرب إلى أبسط معالج schoolMIPS ، قامت بتوليفها من أجل Intel FPGA MAX10 FPGA ، وحددت الحد الأقصى للتردد وزيادة إنتاجية البرامج البسيطة. فعلت كل هذا في البداية في قرية بورميستروفو ، منطقة نوفوسيبيرسك ، ثم في مؤتمر في تومسك.

الآن انتقلت داشا كريفوروتشكو (اسم هذا الصف العاشر) إلى مدرسة داخلية في موسكو وسألني عما يجب أن تصممه. أعتقد أنه في هذه المرحلة من حياتها المهنية ، ينبغي عليها تصميم مسرع أجهزة للشبكات العصبية استنادًا إلى مجموعة انقباضية لتكاثر المصفوفات. استخدم لغة وصف أجهزة Verilog و Intel FPGA FPGA ، ولكن ليس MAX10 الرخيص ، ولكن شيئًا أكثر تكلفة لاستيعاب مجموعة كبيرة من الانقباضات.

بعد ذلك ، قارن بين أداء حل الأجهزة والبرنامج الذي يعمل على معالج schoolMIPS ، وكذلك مع برنامج Python الذي يعمل على كمبيوتر سطح المكتب. كحالة اختبار ، استخدم التعرف على الأرقام من مصفوفة صغيرة.

في الواقع ، تم تطوير جميع أجزاء هذا التمرين بالفعل من قبل أشخاص مختلفين ، ولكن النقطة الأساسية هي وضع هذا في تمرين واحد موثق ، ويمكن بعد ذلك استخدامه كأساس للدورة التدريبية عبر الإنترنت والمسابقات العملية:

1) eNano ، القسم التعليمي في RUSNANO ، الذي نظم في الماضي حلقات تشارلز دانشيك حول تصميم الإلكترونيات الحديثة (RTL-to-GDSII route) للطلاب ويعمل حاليًا على دورة عبر الإنترنت من هذا النوع (تصميم الأجهزة على مستوى عمليات نقل السجلات والشبكات العصبية) بالطبع لايت للطلاب المتقدمين. أنا هنا تشارلز وأنا في مكتبهما:

2) قد تكون قاعدة الألعاب الأولمبية مهتمة

بأولمبياد NTI ، والتي أثرت بها هذه المسألة قبل أسبوعين في موسكو. على سبيل المثال ، يمكن للمشاركين في الألعاب الأولمبية إضافة جهاز لوظائف التنشيط المختلفة. إليكم زملاء من أولمبياد NTI:

لذلك إذا طورت داشا هذا ، يمكنها نظريًا تقديم معجلها الموصوف جيدًا في كل من RUSNANO وفي أولمبياد NTI. أعتقد أنه سيكون مفيدًا لإدارة مدرستها - يمكن عرضها على التلفزيون أو حتى إرسالها إلى مسابقة Intel FPGA. إليكم

بعض الروس من سانت بطرسبرغ في نهائي مسابقة Intel FPGA في سانتا كلارا ، كاليفورنيا :

الآن دعنا نتحدث عن الجانب الفني للمشروع. تم وصف فكرة التسريع الشامل الانقباضي في مقال ترجمه المحرر هابرا فياتشيسلاف جولوفانوف

SLY_G لماذا تعتبر الـ TPUs مناسبة جدًا للتعلم العميق؟هذا هو الشكل البياني لشبكة تدفق البيانات العصبية مثل التعرف السهل:

عنصر حسابي بدائي يؤدي الضرب والإضافات:

هيكل شديد الانحناء لهذه العناصر ، هذه المجموعة الانقباضية لضرب المصفوفة هي:

يوجد على الإنترنت مجموعة من الشفرات على Verilog و VHDL مع تطبيق مصفوفة الانقباضي ، على سبيل المثال ، يوجد الكود

أسفل منشور المدونة هذا :

module top(clk,reset,a1,a2,a3,b1,b2,b3,c1,c2,c3,c4,c5,c6,c7,c8,c9); parameter data_size=8; input wire clk,reset; input wire [data_size-1:0] a1,a2,a3,b1,b2,b3; output wire [2*data_size:0] c1,c2,c3,c4,c5,c6,c7,c8,c9; wire [data_size-1:0] a12,a23,a45,a56,a78,a89,b14,b25,b36,b47,b58,b69; pe pe1 (.clk(clk), .reset(reset), .in_a(a1), .in_b(b1), .out_a(a12), .out_b(b14), .out_c(c1)); pe pe2 (.clk(clk), .reset(reset), .in_a(a12), .in_b(b2), .out_a(a23), .out_b(b25), .out_c(c2)); pe pe3 (.clk(clk), .reset(reset), .in_a(a23), .in_b(b3), .out_a(), .out_b(b36), .out_c(c3)); pe pe4 (.clk(clk), .reset(reset), .in_a(a2), .in_b(b14), .out_a(a45), .out_b(b47), .out_c(c4)); pe pe5 (.clk(clk), .reset(reset), .in_a(a45), .in_b(b25), .out_a(a56), .out_b(b58), .out_c(c5)); pe pe6 (.clk(clk), .reset(reset), .in_a(a56), .in_b(b36), .out_a(), .out_b(b69), .out_c(c6)); pe pe7 (.clk(clk), .reset(reset), .in_a(a3), .in_b(b47), .out_a(a78), .out_b(), .out_c(c7)); pe pe8 (.clk(clk), .reset(reset), .in_a(a78), .in_b(b58), .out_a(a89), .out_b(), .out_c(c8)); pe pe9 (.clk(clk), .reset(reset), .in_a(a89), .in_b(b69), .out_a(), .out_b(), .out_c(c9)); endmodule module pe(clk,reset,in_a,in_b,out_a,out_b,out_c); parameter data_size=8; input wire reset,clk; input wire [data_size-1:0] in_a,in_b; output reg [2*data_size:0] out_c; output reg [data_size-1:0] out_a,out_b; always @(posedge clk)begin if(reset) begin out_a<=0; out_b<=0; out_c<=0; end else begin out_c<=out_c+in_a*in_b; out_a<=in_a; out_b<=in_b; end end endmodule

وألاحظ أن هذا الرمز ليس مُحسَّنًا وعمومًا أخرق (وحتى مكتوب بشكل غير مهني - يستخدم المصدر في المنشور تعيينات كتلة في @ (posedge clk) - لقد أصلحته). يمكن داشا على سبيل المثال استخدام Verilog إنشاء بنيات لرمز أكثر أناقة.

بالإضافة إلى إدراكين متطرفين للشبكة العصبية (على المعالج والصفيف الانقباضي) ، يمكن لـ Dasha النظر في خيارات أخرى أسرع من المعالج ، ولكن ليس بنفس الشرسة مثل عمليات الضرب مثل الصفيف الانقباضي. صحيح ، هذا على الأرجح ليس لتلاميذ المدارس ، بل للطلاب.

أحد الخيارات هو جهاز تنفيذي به عدد كبير من كتل الوظائف التي تعمل بالتوازي ، كما هو الحال في معالج خارج الترتيب:

خيار آخر هو ما يسمى المصفوفة الخشنة القابلة لإعادة التشكيل - وهي مصفوفة من العناصر شبه المعالج ، ولكل منها برنامج صغير. تتشابه عناصر المعالج هذه بشكل مثالي مع خلايا FPGA / FPGA ، ولكنها لا تعمل مع إشارات فردية ، ولكن مع مجموعات بت / أرقام على الحافلات والسجلات - راجع

التقرير المباشر من ولادة لاعب رئيسي في الأجهزة AI ، والذي يسرع TensorFlow ويتنافس مع NVidia " .

الآن الرسالة الأصلية من داشا:

يوم جيد يا يوري.

في عام 2017 ، درست في مدرستك في LSHUP في ورشة العمل الخاصة بك وفي أكتوبر 2017 شاركت في مؤتمر في تومسك في أكتوبر من نفس العام مع العمل المكرس لتضمين وحدة الضرب في معالج SchooolMIPS.

أود مواصلة هذا العمل الآن. في الوقت الحالي ، تمكنت من الحصول على إذن في المدرسة لاتخاذ هذا الموضوع كدورات دراسية صغيرة. هل لديك الفرصة لمساعدتي في استمرار هذا العمل؟

ملاحظة: بما أن العمل يتم في تنسيق محدد ، فإن كتابة مقدمة ومراجعة الأدبيات للموضوع مطلوبة. يرجى تقديم المشورة للمصادر التي يمكنك من خلالها أخذ معلومات حول تاريخ تطور هذا الموضوع ، والفلسفات المعمارية ، وما إلى ذلك ، إذا كان لديك مثل هذه الموارد في الاعتبار.

بالإضافة إلى ذلك ، في اللحظة التي أعيش فيها في موسكو في مدرسة داخلية ، قد يكون التفاعل أسهل.

التحيات

داريا كريفوروتشكو.

قامت داشا بتدريس Verilog والتصميم على مستوى السجل بمساعدة مني وكتاب

" الدائرة

الرقمية وهندسة الكمبيوتر" من تأليف ديفيد هاريس وسارة هاريس . ومع ذلك ، إذا كنت تلميذة / تلميذة وترغب في فهم المفاهيم الأساسية على مستوى بسيط جدًا ، إذن فقد أصدرت دار النشر DMK-Press

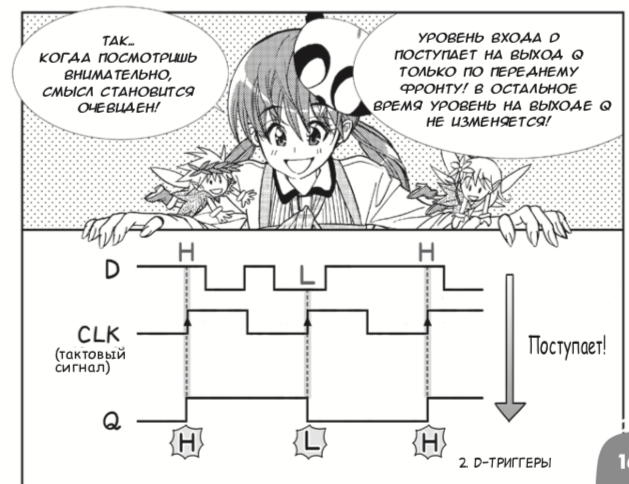

ترجمة روسية للمانجا اليابانية لعام 2013 حول الدوائر الرقمية التي أنشأتها أمانو هيديرو وميغورو كوجي. على الرغم من الشكل التافه للعرض التقديمي ، يقدم الكتاب بشكل صحيح العناصر المنطقية ومشغلات D ،

ثم يربط هذا بـ FPGAs :

إليكم ما تبدو عليه

المدرسة الصيفية للمبرمجين الشباب في منطقة نوفوسيبيرسك ، حيث تعلمت داشا Verilog ، FPGAs ، وهي منهجية لتطوير نقل السجل (مستوى نقل السجل - RTL):

وها هو خطاب داشا في مؤتمر تومسك مع طالب آخر في الصف العاشر ، أرسيني تشيجوداييف:

بعد حديث داشا معي ومع ستانيسلاف تشيلنيو

سبارف ، المبتكر الرئيسي لمجموعة المعالجات التعليمية schoolMIPS لتنفيذها على FPGAs:

مشروع schoolMIPS هو مع وثائق في

https://github.com/MIPSfpga/schoolMIPS . في أبسط تشكيلة من هذا المعالج الأساسي للتدريب ، لا يوجد سوى 300 خط في فيريلوج ، بينما يوجد في القطاع الصناعي المضمن للطبقة الوسطى حوالي 300 ألف خط. ومع ذلك ، تمكنت داشا من الشعور بما يبدو عليه عمل المصممين في الصناعة ، والذين قاموا بتغيير وحدة فك الترميز والجهاز المنفذ بنفس الطريقة عند إضافة تعليمات جديدة إلى المعالج:

في الختام ، نقدم صوراً لعميد جامعة سامارا إيليا كودريافتسيف ، المهتمة بإنشاء مدرسة صيفية وأولمبياد مع معالجات FPGA للمتقدمين في المستقبل:

وصورة لموظفي Zelenograd MIET الذين يخططون بالفعل لمثل هذه المدرسة الصيفية العام المقبل:

كل المواد من RUSNANO ، والمواد المحتملة للأولمبياد NTI ، وكذلك الإنجازات التي تحققت على مدى العامين الماضيين في تنفيذ FPGAs والهندسة المعمارية الدقيقة في برنامج HSE MIEM ، جامعة موسكو الحكومية وكازان

إنوبوليس ، يجب أن تسير بشكل جيد في مكان وآخر.