في التعليقات على مقالتي

حول التحكم في RGB LEDs باستخدام كتلة متحكم UDB من Cypress ، اقترح أنه سيكون من الجيد أن نخبرك في بداية المقال باختصار عن UDB. كما أشرت بالفعل في المقال ، لا يمكنني الكتابة عن UDB لفترة وجيزة ، لكن يمكنك ببساطة نقل وثائق الشركة إليها لتعريف القارئ المحلي باستخدام هذه الأداة القوية لتنفيذ وظائف البرامج الثابتة.

ولكن أولاً ، دعونا نلقي نظرة على ما يدور حوله PSoC. PSoC هي عائلة من شرائح Cypress لتنفيذ الأنظمة على الرقاقة. تمتلك العائلات المختلفة مجموعة أساسية مختلفة من المعالجات (بالنسبة إلى PSoC 3 ، فهي MCS-51 ، أما بالنسبة لـ PSoC 4 ، فهي Cortex M0 ، أما بالنسبة لـ PSoC 5LP ، فهي Cortex M3 ، أما بالنسبة إلى PSoC 6 فتحتوي على اثنين في آن واحد: Cortex M0 + و Cortex M4) ومجموعة من المنطق القابل للبرمجة. علاوة على ذلك ، فإن هذا المنطق ليس رقميًا محضًا ؛ فهناك أشياء تناظرية هناك. بالإضافة إلى مجموعة من ADCs مختلفة ، وهناك أيضا مفاتيح التناظرية. يمكنك حتى ربط الساقين برمجياً من خلال دوائر تناظرية ، ومع ذلك ، سيتم قياس مقاومة الدائرة بالكيلوغرام. توجد مضخمات تشغيلية داخل PSoC يمكن تبديلها برمجيًا ، مما يعني أنه يمكنك إنشاء كتل تناظرية مختلفة عليها.

بالمناسبة ، يمكن تشغيل PSoCs بواسطة أي جهد من 2.7 إلى 5.5 فولت. أي أنك لست بحاجة إلى التفكير في أي نوع من عوامل التثبيت سواء باستخدام طاقة البطارية أو طاقة USB.

لكنني كتبت عن الأشياء التناظرية بحتة لكلمة حمراء. الآن سوف نركز على الأشياء الرقمية. تحتوي معظم وحدات التحكم الحديثة على وحدات طرفية قوية توفر مجموعة كبيرة من الوظائف. ولكن في الممارسة العملية ، في كل تطوير برامج محدد ، لا يتم استخدام هذه الكتل بالكامل ، ولكن جزئيًا فقط. وفي PSoC ، بدلاً من مجموعة جيدة ، يتم تنفيذ منطق البرنامج ، على غرار منطق FPGAs الكلاسيكي. وفقًا لذلك ، من الممكن تنفيذ تلك الكتل المطلوبة بالضبط عليها ، من خلال تضمينها في تلك الأوضاع المطلوبة. ولا ينبغي إنفاق الموارد على أوضاع غير مستخدمة ، مما يمنحها بعيداً لتنفيذ نوع من الأشياء الخاصة.

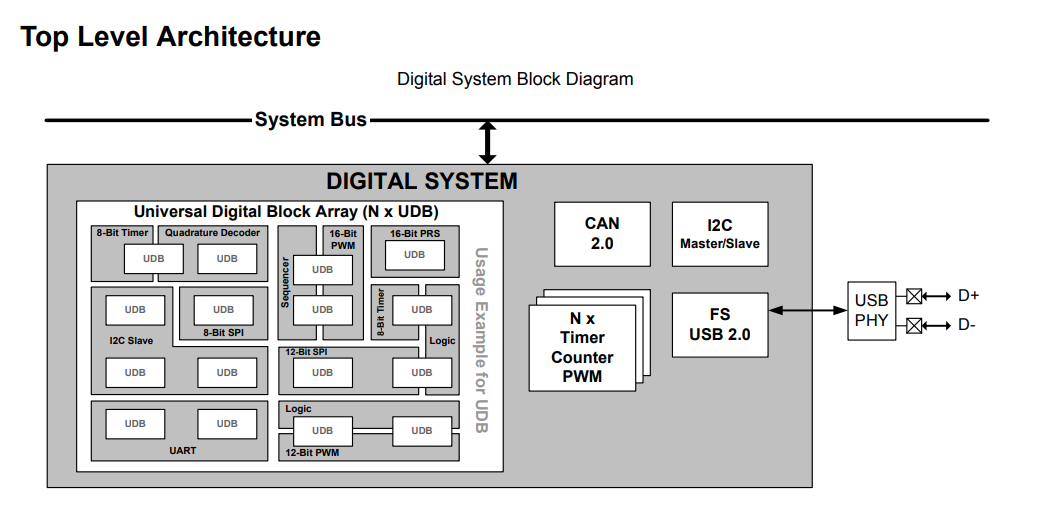

وهنا يحدث بعض سوء الفهم في كثير من الأحيان. اعتاد العديد من المطورين على حقيقة وجود نوعين من الدوائر المتكاملة المنطقية القابلة للبرمجة (FPGAs): CPLD و FPGA. لذلك ، يعتقد الكثير ممن سمعوا عن PSoC ، أن هناك نوعًا من صندوق CPLD يمكن برمجته في Veriolg. في الواقع ، نعم ولا. يوجد بالفعل عدد معين من PLDs (بدون "C" ، فقط PLDs) ، ويمكنك بالفعل برمجة هذه البرامج على Verilog. ولكن في الحقيقة ، تعد PLDs جزءًا من كتل UDB. وهو UDB هو العنصر الرئيسي في المنطق القابل للبرمجة الذي يتم تنفيذه في PSoC. هذه الكتلة أصلية للغاية وتوفر ببساطة أوسع الفرص للمطور. النظر في الشكل من وثائق الملكية التي تشرح جوهر استخدام كتل UDB.

بما أنني درست كل شيء باستخدام عائلة PSoC 5LP كمثال ، فسأقوم بترجمة الوثائق إليها. ولكن قبل أن تبدأ ، سأقول بضع كلمات حول سعر وحدات التحكم هذه. إذا ذهبت إلى Ali Express ونظرت إلى اللوح الخاص بهم ، فستشعر بالحزن. بصراحة ، بالمقارنة مع STM32-DISCOVERY ، ما زالوا لا يمثلون شيئًا ، ولكن بالمقارنة مع النماذج الأولية STM32F103C8T6 ، فهي غالية الثمن بعض الشيء. أولاً وقبل كل شيء ، يرجع ذلك إلى حقيقة أن نماذج الشركات لا تحتوي دائمًا على وحدة تحكم واحدة ، ولكن يوجد بها وحدتا تحكم من هذا القبيل. يتم تنفيذ وظائف JTAG على PSoC 5LP ، حتى لو كانت وحدة التحكم الهدف و PSoC 4 (عادة ما لا يكون لدى الأخير منفذ USB).

ولكن بتقسيم السعر على اثنين ، ما زلنا نعلم أنه أعلى من سعر STM32F103 ، وهو مشابه في جوهر المعالج. ومع ذلك ، إذا أضفنا حتى أبسط CPLD إلى نفس STM32 من الخارج ، فإن السعر الإجمالي سيصدر لصالح PSoC. وسنضيف الأرجل المفقودة إلى اتصال هاتين الحالتين (تحتوي PSoC على جميع الوصلات من الداخل). وكذلك سعر السنتيمتر المربع من اللوح. لذلك اتضح أنه إذا كنت بحاجة إلى العمل فقط مع جوهر المعالج ، فإن PSoC ليس ضروريًا حقًا. إذا كنت بحاجة إلى جلب بعض الوظائف إلى البرامج الثابتة أو مستوى الأجهزة ، فأنت بحاجة إلى PSoC. على ذلك ، سوف يخرج النظام أرخص وأسهل.

في الواقع ، لدي فكرة الهوس في محاولة لتقديم دعم الأجهزة لنواة RTOS MAX. للقيام بذلك ، درست منهجية تطوير تطبيقات Bare Metal لـ Altera V SoC (للأسف ، اتضح أن ميزة الهيكل موجودة بحيث يمكن تباطؤ نظام التشغيل ، لكن لا يمكنك تسريعها - الطلبات الفردية على الأجهزة تأتي مع زمن انتقال مجنون). لهذا ، بدأت أتقن PSoC. لم أكن قد وصلت إلى رفع تردد التشغيل kernel (توجد أفكار عامة فقط) ، لكني أعجبت حقًا فكرة برمجة UDB. بالطبع ، أنا مهتم الآن بالوصول بهذه الفكرة إلى الحد الأقصى لعدد المبرمجين المحليين. لذلك ، ننتقل إلى ترجمة الجزء المقابل من وثائق ملكية Cypress على UDB. يتم الحفاظ على ترقيم الفصول والأشكال وفقًا للوثيقة الأصلية.

المحتوى العام للدورة "UDB. ما هذا؟ "

الجزء 1. مقدمة. Pld. (المادة الحالية)

الجزء 2. Datapath.الجزء 3. Datapath FIFO.الجزء 4. Datapath ALU.الجزء 5. Datapath. أشياء صغيرة مفيدة.الجزء 6. وحدة الإدارة والحالة.الجزء 7. توقيت وإعادة ضبط وحدة التحكمالجزء 8. معالجة UDBUDB. ما هذا؟ الجزء 1

21. كتل الرقمية العالمية

في هذا الفصل ، سننظر في كيفية تمكين الكتل الرقمية العالمية (UDBs) في تطوير الوظائف الطرفية الرقمية القابلة للبرمجة. تحقق بنية UDB توازنًا بين دقة التكوين والتنفيذ الفعال. تتكون UDBs من مزيج من المنطق غير المُبدّل المماثل لمصفوفة المنطق القابلة للبرمجة (PLM ، الإنجليزية PLD) ، والمنظم المهيكل (آلات التشغيل ، المشار إليها فيما يلي باسم Datapath) ونظام تتبع مرن.

21.1 الميزات

- لتحقيق المرونة المثلى ، يحتوي كل UDB على المكونات التالية:

• Datapath من 8 بتات استنادًا إلى ALU (وحدة الحساب والمنطق ، ALU) مع مستودع تعليمي مكون من 8 كلمات وعدة سجلات وسجلات FIFO مؤقتة ؛

• PLDs ، يحتوي كل منها على 12 إدخالًا ، و 8 مصطلحات توصيلية (شروط المنتج ، PT) وأربعة مخرجات macrocell ؛

• سجلات الإدارة والوضع ؛

• عقارب الساعة وإعادة وحدات. - يحتوي PSoC 5LP على صفيف يصل إلى 24 UDB في الحجم.

- تتبع مرن بين عناصر صفيف UDB.

- يمكن تقسيم عناصر UDB أو ربطها لإنشاء وظائف أكبر.

- التنفيذ المرن لعدد من الوظائف الرقمية ، بما في ذلك أجهزة ضبط الوقت ، والعدادات ، ومعدلات عرض النبض (بما في ذلك PWM مع مولد النطاق الترددي) ، UART ، I2C bus ، SPI bus و CRC / التحقق.

21.2 مخطط كتلة

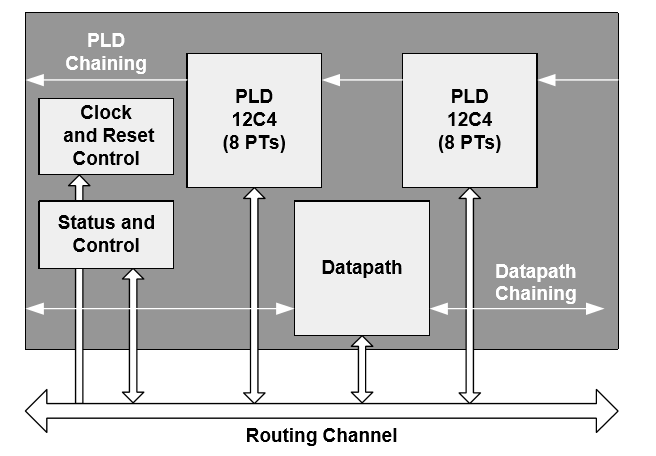

يوضح الشكل 21-1 UDB كإنشاء يحتوي على كتلتين منطقيتين أساسيتين ، PLD و Datapath ووظائف التحكم والحالة والساعة وإعادة الضبط.

الشكل 21-1. مخطط كتلة من UDB.

الشكل 21-1. مخطط كتلة من UDB.21.3 كيف تعمل؟

المكونات الرئيسية لبنك UDB هي:

- PLD (2). يتم تغذية البيانات من موارد التتبع إلى مدخلات هذه الكتل. إنها تقوم بتنفيذ المنطق التوافقي والتقاط البيانات ، والذي يسمح لك بتطبيق آلات الحالة المحدودة ، والتحكم في عمليات كتلة Datapath ، وتكوين شروط الإدخال ومخرجات التحكم.

- Datapath. تحتوي هذه الكتلة على ALU القابلة للبرمجة ديناميكيًا ، وأربعة سجلات ، ومخزنان مؤقتان لـ FIFO ، ومقارنات ، وإنشاء شرط.

- الإدارة والحالة (الحالة والتحكم). توفر هذه الوحدات آلية للتفاعل بين البرامج المصغرة للمعالج المركزي (CPU) والتزامن مع عمليات UDB. تعمل سجلات التحكم على العناصر الداخلية ، وقراءة سجلات الحالة حالة العناصر الخارجية.

- الساعة وإعادة ضبط التحكم توفر هذه الوحدات اختيار توقيت وتمكين ، وكذلك إعادة تعيين الاختيار داخل UDB.

- إشارات السلسلة. تشتمل PLD و Datapath على إشارات تسمح لك بتسلسل الكتل المجاورة في سلسلة لإنشاء وظائف أعلى بت.

- تتبع القناة يتم توصيل UDBs بقناة التتبع من خلال مصفوفات التبديل القابلة للبرمجة للاتصال بين الكتل داخل UDB نفسها وللتواصل مع UDBs الأخرى في الصفيف.

- واجهة ناقل النظام (واجهة ناقل النظام). يتم عرض جميع السجلات وذاكرة الوصول العشوائي في كل UDB على مساحة عنوان النظام ، ويمكن الحصول على الوصول إليها باستخدام المعالج المركزي أو من خلال الوصول المباشر إلى الذاكرة (الوصول المباشر للذاكرة الإنجليزية ، DMA) في شكل 8 بت و 16 بت البيانات.

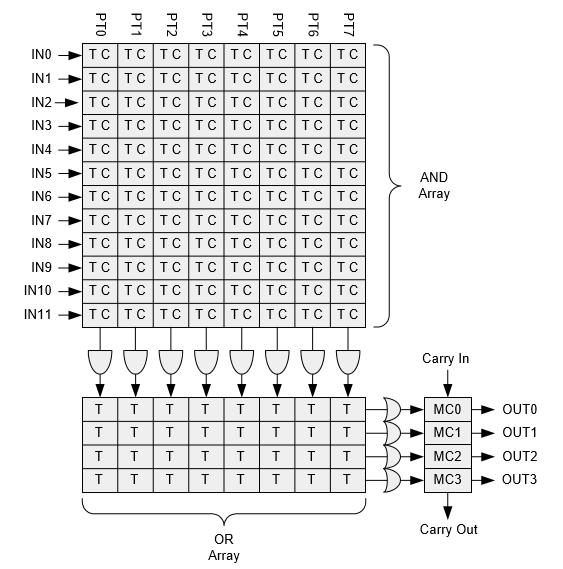

21.3.1. Pld

يحتوي كل UDB على PLDs 12C4. يمكن استخدام كتل PLD الموضحة في الشكل 21-1 لتنفيذ أجهزة الحالة ومعالجة بيانات الإدخال / الإخراج وإنشاء منطق الجدول (جدول بحث المهندس ، LUT). بالإضافة إلى ذلك ، يمكن تهيئة PLD لأداء وظائف حسابية ، وتعيين تسلسل Datapath ، وإنشاء الحالة. يمكن تصنيع المنطق العام وإسقاطه على كتل PLD. يقدم هذا القسم نظرة عامة على بنية PLD.

PLD لديه 12 المدخلات التي تنقل المعلومات إلى 8 مصطلحات ملتحمة في صفيف AND. في كل مصطلح مترابط ، يمكنك اختيار إدخال مباشر (صحيح ، T) أو معكوس (مكمل ، C). يذهب إخراج المصطلحات الملحقة إلى إدخال صفيف OR. يشير الحرف "C" في 12C4 إلى أن شروط OR ثابتة لجميع المدخلات ، ويمكن لكل إدخال OR الحصول على وصول برمجي إلى أي مصطلح ملتحمي. يوفر هذا الهيكل أقصى مرونة ويضمن إمكانية نقل جميع المدخلات والمخرجات.

الشكل 21-2. هيكل PLD 12C4.

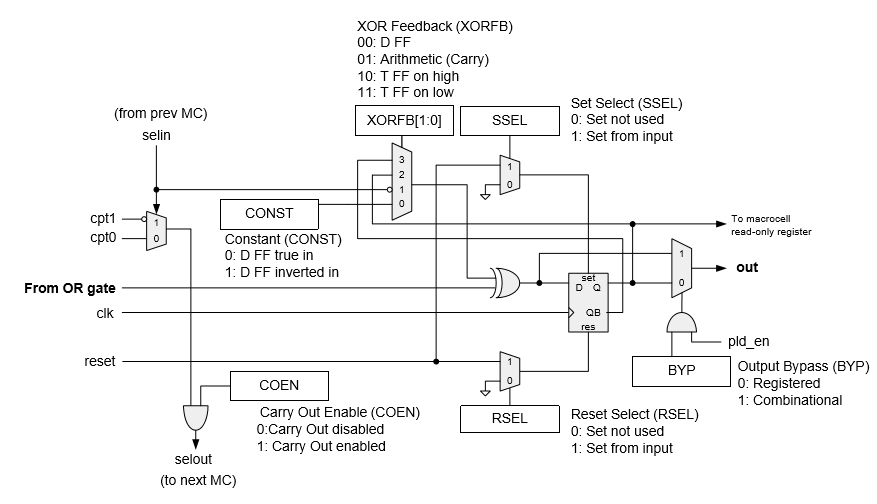

الشكل 21-2. هيكل PLD 12C4.21.3.1.1 ماكرو PLD

يوضح الشكل 21-3 معمارية الخلايا الكبيرة. الإخراج يتحكم في مجموعة التتبع ويمكن إغلاقها أو رامان. للإغلاق ، يتم استخدام المشغل D مع الإدخال المباشر أو العكسي أو المشغل T بمستوى دخل مرتفع أو منخفض. يمكن ضبط مشغل الخرج أو إعادة ضبطه أثناء التهيئة أو بشكل غير متزامن أثناء التشغيل العادي ، عن طريق إشارة خارجية من قناة التتبع.

الشكل 21-3. العمارة الكليةللقراءة فقط PLD ماكرو خلية التسجيل

الشكل 21-3. العمارة الكليةللقراءة فقط PLD ماكرو خلية التسجيلبالإضافة إلى التحكم في صفيف التتبع ، يتم إسقاط مخرجات macrocell لكلا PLD على مساحة العنوان في شكل سجل للقراءة فقط 8 بت ، والذي يمكن الوصول إليه باستخدام وحدة المعالجة المركزية أو DMA.

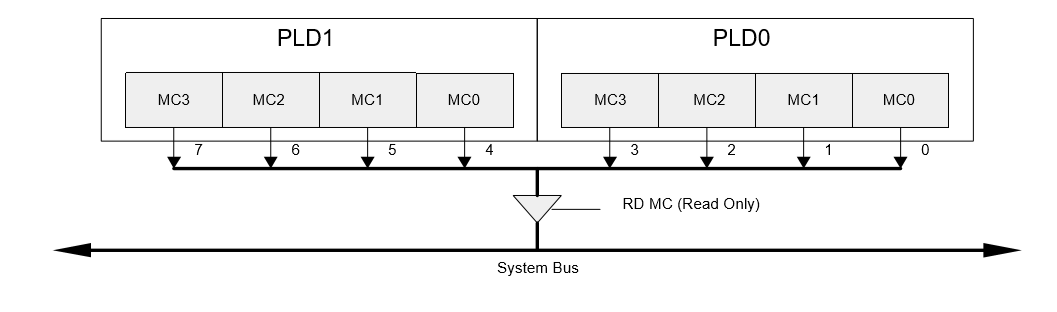

الشكل 21-4. سجل macrocell PLD للقراءة فقط.

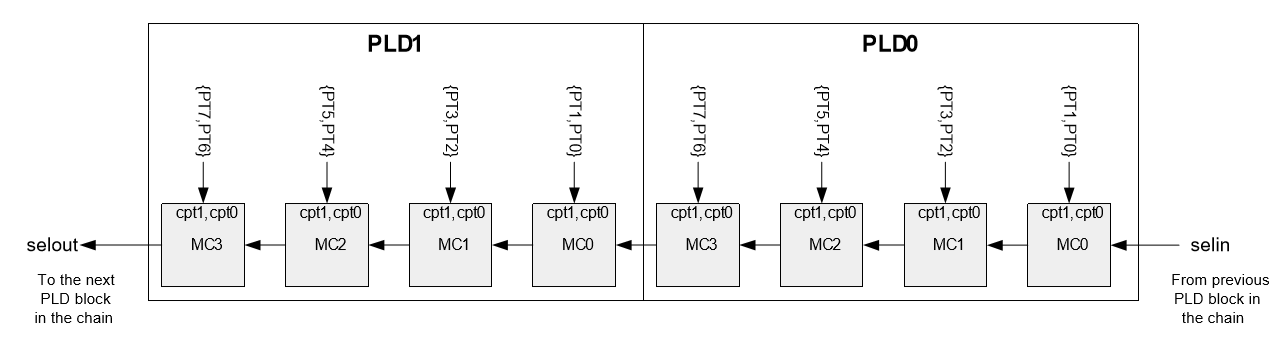

الشكل 21-4. سجل macrocell PLD للقراءة فقط.21.3.1.2 سلسلة الواصلة PLD

يتم ربط PLDs معا في عنونة UDB. كما هو مبين في الشكل 21-5 ، يتم توجيه مدخلات سلسلة حمل selin من UDB السابق إلى الدائرة ، من خلال كل خلية ماكرو في كلا PLD ، ثم يتم توجيهها إلى UDB التالي كإخراج سلسلة حمل selout. لدعم الموضع الفعال لوظائف الحساب ، يتم إنشاء مصطلحات ملتحمة خاصة (PT) ، والتي تستخدم في الخلايا الكبيرة مع سلسلة الواصلة.

الشكل 21-5. PLD سلسلة الواصلة ومدخلات مصطلح الملتحمة الخاصة.

الشكل 21-5. PLD سلسلة الواصلة ومدخلات مصطلح الملتحمة الخاصة.21.3.1.3 تكوين PLD

يظهر كل PLD قبل وحدة المعالجة المركزية أو DMA في شكل ذاكرة الوصول العشوائي مع وصول 16 بت. يحتوي الصفيف AND على 12 × 8 × 2 بت أو 24 بايت للبرمجة ، ويحتوي الصفيف OR على 4 × 8 بت أو 4 بايت للبرمجة. بالإضافة إلى ذلك ، تحتوي كل خلية ماكرو على بايت واحد للتكوين ، يبلغ إجماليه 32 بايت لكل PLD. نظرًا لأن كل UDB يحتوي على 2 PLD ، فإن التكوين الكلي لكل UDB هو 64 بايت.

في المرة القادمة سوف ننظر في التشغيل الآلي (Datapaths).