نستمر في ترجمة وثائق ملكية Cypress إلى كتل UDB. علاوة على ذلك ، كل شيء يتزامن بشكل جيد للغاية. لمتابعة

المقال العملي حول UDB ، ستحتاج إلى استخدام FIFO ، وفي الجزء النظري وصلنا إلى وصفهم. لذلك ، نبدأ في دراستها بالتفصيل.

المحتوى العام للدورة "UDB. ما هذا؟ "

الجزء 1. مقدمة. Pld.الجزء 2. Datapath.الجزء 3. Datapath FIFO. (المادة الحالية)

الجزء 4. Datapath ALU.الجزء 5. Datapath. أشياء صغيرة مفيدة.الجزء 6. وحدة الإدارة والحالة.الجزء 7. توقيت وإعادة ضبط وحدة التحكمالجزء 8. معالجة UDB21.3.2.2 Datapath FIFO

صيغ وتكوينات FIFO

يحتوي كل مخزن مؤقت FIFO على العديد من أوضاع التشغيل والتكوينات المتاحة:

الجدول 21-2. صيغ FIFO وتكوينات.

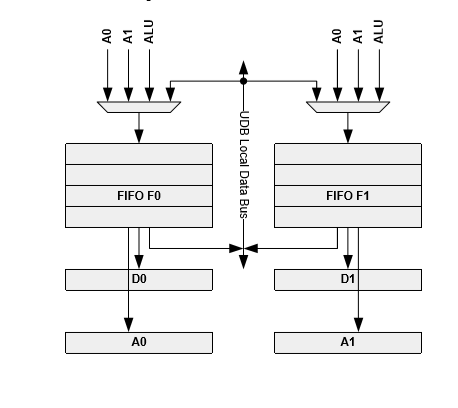

يوضح الشكل 21-7 خيارات التكوين الممكنة لزوج FIFO ، اعتمادًا على أوضاع الإدخال / الإخراج المحددة لكل منها. إذا كان FIFO في وضع الإدخال والآخر في وضع الإخراج ، فسنحصل على تكوين RX / TX. مثال نموذجي حيث هناك حاجة إلى مثل هذا التكوين هو وحدة تحكم ناقل SPI. يوفر تكوين

الالتقاط المزدوج (يتم تكوين كل من FIFOs للإخراج) التقاط مستقل لزوج A0 و A1 أو تسجيلين مستقلين لسجلات A0 أو A1. أخيرًا ، في وضع "

المخزن المؤقت المزدوج" (كلاهما عند الإدخال) ، يمكن استخدام إما زوج تسجيل أو سجلين مستقلين للتحميل أو المقارنة.

الشكل 21-7. تكوينات FIFO.

يوضح الشكل 21-8 بالتفصيل مصادر ومستقبلات FIFO.

الشكل 21-8. مصادر FIFO وأجهزة الاستقبال.

عندما يعمل FIFO في وضع المخزن المؤقت للإدخال ، يكون المصدر هو ناقل النظام ، والمستقبلات هي سجلات Dx و Ax. عند العمل في وضع المخزن المؤقت للإخراج ، تكون المصادر هي سجلات Ax و ALU ، والمستقبل هو ناقل النظام. يتم تحديد اختيار المضاعف بشكل ثابت في سجل تكوين UDB CFG15 ، كما هو موضح في الجدول الخاص بـ F0_INSEL [1: 0] أو F1_INSEL [1: 0]:

الجدول 21-3. مجموعة من مُضاعفات FIFO في سجل تكوين UDB.

وضع FIFO

ينشئ كل FIFO إشارات الحالة ، "الناقل" و "الكتلة" ، والتي يتم إرسالها إلى موارد التتبع UDB من خلال مُضاعِف خرج Datapath. يمكن استخدام حالة الناقل لمقاطعة أو طلب قراءة / كتابة DMA إلى FIFO. تهدف حالة "الكتلة" بشكل أساسي إلى تمرير حالة FIFO إلى كيانات UDB الداخلية. يعتمد الغرض من بتات الحالة على الاتجاه المكوّن (Fx_INSEL [1: 0]) وعلى بتات مستوى FIFO. يتم تعيين بتات مستوى FIFO (Fx_LVL) في سجل التحكم المساعد في مساحة سجل العمل. تظهر خيارات الحالة في الجدول التالي:

الجدول 21-4. خيارات حالة FIFO.

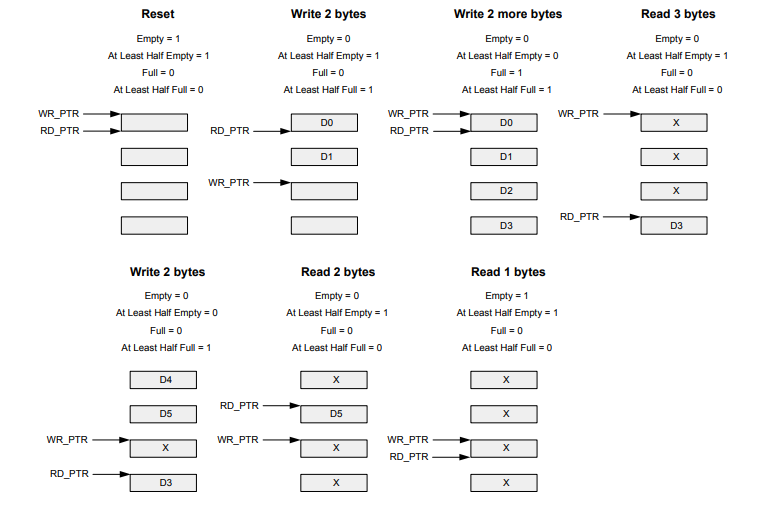

FIFO العمل التوضيح

يوضح الشكل 21-9 تسلسلًا نموذجيًا للقراءة والكتابة ، وكذلك توليد الحالات المرتبطة بهذه العمليات. في الشكل ، تحدث القراءة والكتابة في أوقات مختلفة ، ولكن يمكن تنفيذها في وقت واحد.

الشكل 21-9 عملية استقبال FIFO.

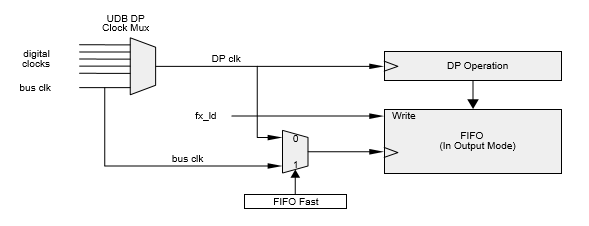

وضع FIFO السريع (FIFO FAST)

عندما يكون FIFO في وضع المخزن المؤقت للإخراج ، عادةً ما تستخدم عملية تمهيد FIFO تردد ساعة Datapath المحدد لساعة إشارة الكتابة. كما هو مبين في الشكل 21-10 ، عند اختيار وضع FIFO Fast (FIFO FAST) ، يمكنك تحديد تردد الحافلة لهذه العملية المحددة. عند استخدامها بالاقتران مع وضع

المستوى / الحافة = الحافة ، تقلل هذه العملية من تأخير النقل من البطارية إلى FIFO من فترة ساعة Datapath إلى فترة ساعة الناقل ، حيث يمكن أن يكون تردد الحافلة أعلى بكثير. هذا يسمح لوحدة المعالجة المركزية أو DMA بقراءة نتيجة FIFO المستلمة بأقل تأخير.

كما هو مبين في الشكل 21-10 ، يتم تنفيذ عملية التمهيد السريع بغض النظر عن ساعة Datapath الحالية ، ومع ذلك ، فإن استخدام سرعة ساعة الناقل يمكن أن يزيد من استهلاك الطاقة.

الشكل 21-10. استقبال FIFO التكوين السريع.

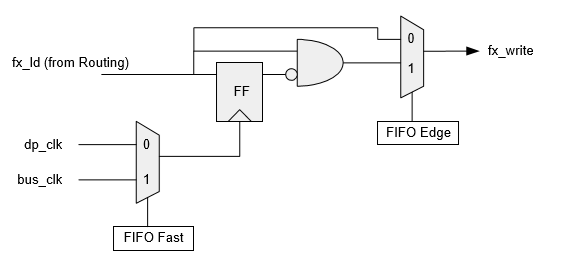

وضع تسجيل الحافة / المستوى FIFO (التفاضلية / المستوى)

هناك وضعان للتسجيل في FIFO من Datapath. في الوضع الأول ، يتم نقل البيانات بشكل متزامن من البطاريات إلى FIFO. عادةً ما يتم إنشاء إشارة التحكم لهذا السجل (FX_LD) بواسطة جهاز دولة أو عن طريق حالة متزامنة مع توقيت Datapath. سيتم تنفيذ الكتابة إلى FIFO في أي دورة تكون فيها إشارة التحكم في حمل الإدخال هي "1". في الوضع الثاني ، يتم استخدام FIFO لالتقاط قيم البطارية استجابة للحافة الإيجابية لإشارة FX_LD. في هذا الوضع ، يكون تنسيق إشارة الإشارة تعسفيًا (ومع ذلك ، يجب أن تكون فترتها مساوية لدورة ساعة Datapath واحدة على الأقل). مثال على هذا الوضع هو التقاط قيمة البطارية باستخدام مدخلات القدم الخارجية كمحفز. يتمثل أحد قيود هذا الوضع في أن معلمة الإدخال يجب أن تعود إلى القيمة "0" على الأقل في دورة واحدة قبل اكتشاف فرق إيجابي آخر.

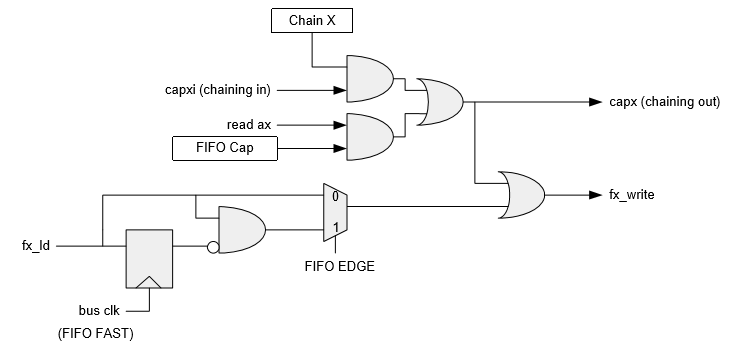

يوضح الشكل 21-11 تنفيذ وضع الكشف التفاضلي عند إدخال FX_LD. يتم التحكم في وضع كلا FIFOs في UDB بواسطة الشيء نفسه ، مع تبديل هذا الخيار. لاحظ أن الكشف التفاضلي مسجل على تردد يساوي تردد FIFO المحدد.

الشكل 21-11. الكشف التفاضلي لأجهزة استقبال تسجيل FIFO الداخلية.

وضع التقاط البرامج FIFO

يتمثل أحد المتطلبات الشائعة والمهمة في تمكين وحدة المعالجة المركزية و DMA من قراءة محتويات البطارية بشكل موثوق أثناء التشغيل العادي. يتم ذلك باستخدام التقاط البرنامج وتمكينه باستخدام بت تهيئة FIFO Cap. ينطبق هذا البت على FIFOs في UDB ، لكنه يعمل فقط عندما يكون FIFO في وضع المخزن المؤقت للإخراج. عند استخدام برنامج التقاط ، يجب قراءة F0 من A0 و F1 من A1.

كما هو مبين في الشكل 21-12 ، تبدأ قراءة البطارية في الكتابة إلى FIFO من البطارية. يتم ربط الإشارة في سلسلة بحيث قراءة البايت محددة في نفس الوقت يلتقط قيم البطارية لجميع UDBs في السلسلة. يسمح هذا للمعالج ذي 8 بت بقراءة 16 بت أو أكثر بنجاح في نفس الوقت. يجب تجاهل البيانات التي يتم إرجاعها عند قراءة البطارية ، ويمكن قراءة القيمة الملتقطة على الفور من FIFO.

يتم إرسال إشارة FX_LD المتعقبة ، التي تنشئ حمل FIFO ، إلى المصطلح OR مع إشارة التقاط البرنامج. عند استخدام التقاط الأجهزة والبرامج في نفس الوقت ، يمكن أن تكون النتيجة غير متوقعة. كقاعدة عامة ، يجب أن تكون هذه الوظائف حصرية بشكل متبادل ، ومع ذلك ، يمكن استخدام التقاط البرامج والأجهزة في وقت واحد وفقًا للشروط التالية:

- تم ضبط وضع الساعة لالتقاط FIFO على FIFO FAST.

- تم ضبط وضع تسجيل FIFO على FIFO EDGE.

وفقًا للشروط الموضحة أعلاه ، تعمل عمليات التقاط الأجهزة والبرامج بنفس الطريقة ، وخلال أي دورة لساعة الحافلة ، يمكن لأي من هذه الإشارات أن تؤدي إلى التقاط.

يوصى أيضًا بمسح FIFO المستهدف في رمز البرنامج (سجل ACTL) قبل بدء التقاط البرنامج. بفضل هذا ، سيتم تعيين مؤشرات القراءة والكتابة FIFO إلى حالة معروفة.

الشكل 21-12. تكوين لقطة البرنامج.

ملاحظة المترجم:

لفترة طويلة لم أستطع فهم معنى هذا القسم. بعد ذلك لفترة طويلة كنت متأكداً من أن القسم كتب لـ PSoC3 ، والذي لا يمكن الوصول إلى جوهره المكون من ثمانية بتات أكثر من بايت. ولكن عند إنشاء الجزء الثامن من الترجمة ، اتضح أنه حتى في PSoC5LP ، لجميع المعالجات ARM 32 بت ، يمكن الوصول إلى سجلات UDB العاملة في وضع من 8 بت أو ستة عشر بت. اذا حكمنا من خلال الوثيقة ، لا أكثر. هذا هو المكان الذي تأتي فيه الوظيفة الموصوفة في متناول يدي.

بت تحكم FIFO

يحتوي سجل التحكم الإضافي ، والذي يمكن استخدامه للتحكم في FIFO أثناء التشغيل العادي ، على 4 بتات.

يتم استخدام بتات FIFO0 CLR و FIFO1 CLR لإعادة تعيين أو مسح FIFOs. عندما يتم تعيين القيمة "1" لأحد هذه البتات ، تتم إعادة تعيين FIFO المقترنة. يجب استعادة البت إلى قيمته الأصلية ('0') ليواصل FIFO العمل. إذا بقيت قيمة البتة مساوية لقيمة واحدة ، فسيتم تعطيل FIFO المطابق وستعمل كمخزن مؤقت أحادي البايت بدون حالة. يمكن كتابة البيانات إلى FIFO ، البيانات قابلة للقراءة على الفور ويمكن الكتابة عليها في أي وقت. لا يزال من الممكن تعيين اتجاه البيانات مع بتات تكوين FX INSEL [1: 0].

تحدد بتات FIFO0 LVL و FIFO1 LVL المستوى الذي سيصطدم به FIFO بتنسيق الحالة

"الناقل" (عندما يقرأ الحافلة أو يكتب إلى FIFO). أي أن حالة

"الناقل" تعتمد على الاتجاه المحدد ، كما هو موضح في الجدول أدناه.

الجدول 21-5. بت مستوى التحكم FIFO

FIFO عملية غير متزامن

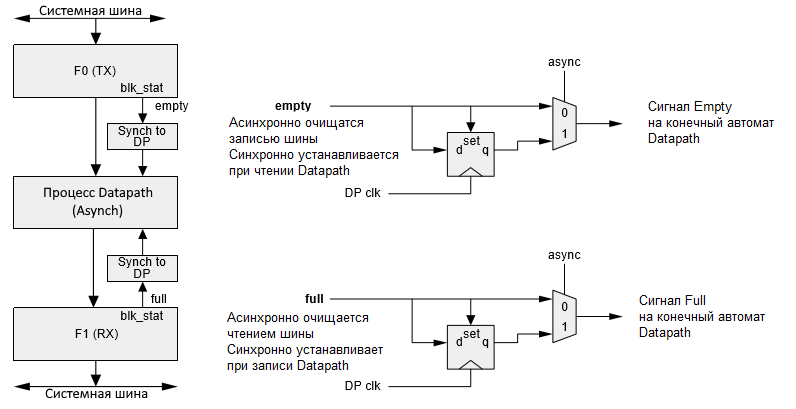

يوضح الشكل 21-13 مبدأ تشغيل FIFO غير المتزامن. على سبيل المثال ، تخيل أن F0 يعمل في وضع مخزن الإدخال المؤقت ، و F1 في وضع المخزن المؤقت للإخراج ، وهو تكوين نموذجي لسجلات TX و RX.

الشكل 21-13. عملية FIFO غير المتزامنة.

على الجانب TX ، يستخدم جهاز حالة Datapath علامة "

إفراغ" لتحديد ما إذا كان هناك أي بايت متاح للاستلام. يتم تعيين القيمة

الفارغة بشكل متزامن مع جهاز حالة Datapath ، ويتم مسحها بشكل غير متزامن بسبب الكتابة من الناقل. بعد التنظيف ، تتم مزامنة الحالة مرة أخرى مع جهاز حالة Datapath.

على الجانب RX ، يستخدم جهاز الحالة RX

كامل لتحديد ما إذا كان هناك مساحة حرة للكتابة إلى FIFO. يتم تعيين القيمة

الكاملة بشكل متزامن مع جهاز حالة Datapath ، ويتم مسحها بشكل غير متزامن بسبب القراءة بواسطة الناقل. بعد التنظيف ، تتم مزامنة الحالة مرة أخرى مع جهاز حالة Datapath.

يتم استخدام بت واحد FIFO ASYNCH لتمكين طريقة التزامن هذه ، بعد التنشيط يتم تطبيق هذه الطريقة على كلا FIFOs.

ينطبق فقط على حالة

الحظر ، حيث يُفترض أن حالة

الناقل تتم مزامنتها بشكل طبيعي من خلال عملية المقاطعة.

الجدول 21-6.

حظر خيارات تزامن حالة FIFO.

تفيض FIFO أثناء العملية

للتنفيذ الآمن لعمليات القراءة والكتابة الداخلية (Datapath) والخارجية (CPU أو DMA) ، يجب استخدام إشارات حالة FIFO. لا توجد حماية مضمنة ضد إفراغ وظروف تجاوز السعة. إذا كان FIFO ممتلئًا وتم تنفيذ عمليات الكتابة اللاحقة (تجاوز السعة) ، فإن البيانات الجديدة تحل محل بداية FIFO (البيانات التي يتم إخراجها حاليًا هي التالية في قائمة انتظار القراءة). إذا كانت FIFO فارغة وتم تنفيذ القراءات اللاحقة (إفراغ أو نفاد) ، فإن قيمة القراءة غير محددة. تظل مؤشرات FIFO دقيقة بغض النظر عن التدفق الفائض.

الانقلاب على مدار الساعة FIFO

يحتوي كل FIFO على عنصر تحكم Fx CK INV ، وهو المسؤول عن قطبية الساعة FIFO فيما يتعلق باستقطاب الساعة Datapath. بشكل افتراضي ، يعمل FIFO بنفس قطبية تسجيل Datapath. عندما تكون هذه البتة 1 ، تعمل FIFO باستقطاب عكسي بالنسبة إلى Datapath. يوفر هذا دعم بروتوكول لتبادل البيانات على كلتا الجبهتين ، مثل SPI.

التحكم الديناميكي FIFO

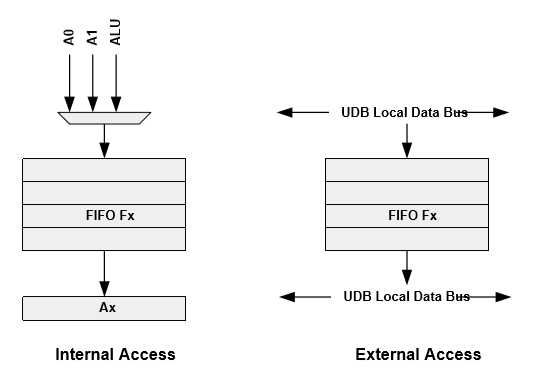

عادة ، يتم تكوين FIFO بشكل ثابت إما في وضع المخزن المؤقت الإدخال أو في وضع المخزن المؤقت الإخراج. بدلاً من ذلك ، يمكن تكوين كل FIFO للعمل في وضع يتم فيه التحكم في الاتجاه ديناميكيًا (تحت تأثير الإشارات الخارجية). بت تكوين واحد لكل FIFO (Fx DYN) مسؤول عن تنشيط هذا الوضع. يوضح الشكل 21-14 التكوينات المتاحة في الوضع الديناميكي FIFO.

الشكل 21-14. وضع FIFO الحيوي.

في وضع الوصول الداخلي ، يستطيع Datapath القراءة والكتابة إلى FIFO. في هذا التكوين ، من أجل تحديد مصدر عمليات الكتابة في FIFO ، يجب تعيين بتات Fx INSEL على 1. Fx INSEL = 0 (مصدر ناقل CPU) في هذا الوضع غير صحيح ، يمكن أن يستغرق فقط القيم 1 أو 2 أو 3 (A0 أو A1 أو ALU ) تجدر الإشارة إلى أن القراءة لديها وصول فقط إلى البطارية المناسبة ، واتجاه سجلات البيانات في هذا الوضع غير متوفر.

في وضع الوصول الخارجي ، يمكن لوحدة المعالجة المركزية أو DMA إما القراءة أو الكتابة إلى FIFO.

التبديل بشكل حيوي بين الوصول الخارجي والداخلي عن طريق إعادة توجيه الإشارات من Datapath. لهذا ، يتم استخدام إشارات الإدخال Datapath d0_load و d1_load. تجدر الإشارة إلى أنه في وضع التحكم الديناميكي ، لا يتوفر d0_load و d1_load للاستخدام العادي عند تحميل تسجيلات D0 / D1 من F0 / F1. يمكن تشغيل إشارات Dx_load بواسطة أي إشارة تتبع ، بما في ذلك الثوابت.

خذ بعين الاعتبار مثالًا ، بدءًا من الوصول الخارجي (dx_load == 1) ، يمكن لوحدة المعالجة المركزية أو DMA كتابة بايت واحد أو أكثر من البيانات إلى FIFO. ثم ، عند التبديل إلى الوصول الداخلي (dx_load == 0) ، يمكن Datapath إجراء عمليات على البيانات. بعد ذلك ، عند التبديل إلى الوصول الخارجي ، يمكن لوحدة المعالجة المركزية أو DMA قراءة نتيجة العمليات الحسابية.

نظرًا لأن Fx INSEL يجب أن تكون دائمًا 01 أو 10 أو 11 (A0 أو A1 أو ALU) ، والذي يتوافق مع "وضع المخزن المؤقت للإخراج" أثناء التشغيل العادي ، فإن إشارات حالة FIFO لها التعريفات التالية (اعتمادًا على معلمة Fx LVL):

الجدول 21-7. وضع FIFO.

نظرًا لأن كلا Datapath ووحدة المعالجة المركزية يمكنهما الكتابة والقراءة من FIFOs ، لم تعد هذه الإشارات تعتبر حالات كتلة وحافلة. يتم استخدام إشارة blk_stat لحالة الكتابة وإشارة bus_stat لحالة القراءة

21.3.2.3 وضع FIFO

توجد أربع إشارات حالة FIFO ، إشارتان لكل FIFO: fifo0_bus_stat ، fifo0_blk_stat ، fifo1_bus_stat و fifo1_blk_stat. يعتمد معنى هذه الإشارات على اتجاه FIFO معين ، والذي يتم تحديده بواسطة التكوين الثابت. يتم وصف حالة FIFO بالتفصيل في القسم

21.3.2.2 Datapath FIFO .

في الجزء التالي ، سننتقل إلى تحليل وحدة المنطق الحسابي (ALU).