في العام الماضي ، مرت مجموعة من المقالات في الصحافة الروسية والأوكرانية بموجة من المقالات حول الأحزاب في وادي السيليكون ، مع بعض جو هوليوود ، ولكن دون تحديد أسماء معينة ، وصور فوتوغرافية ودون وصف تطوير الأجهزة وتقنيات كتابة البرامج المرتبطة بهذه الأسماء. هذا المقال مختلف! كما سيضم المليارديرات والعباقرة والفتيات ، ولكن مع الصور والشرائح والرسوم البيانية وشظايا رمز البرنامج. لذلك:

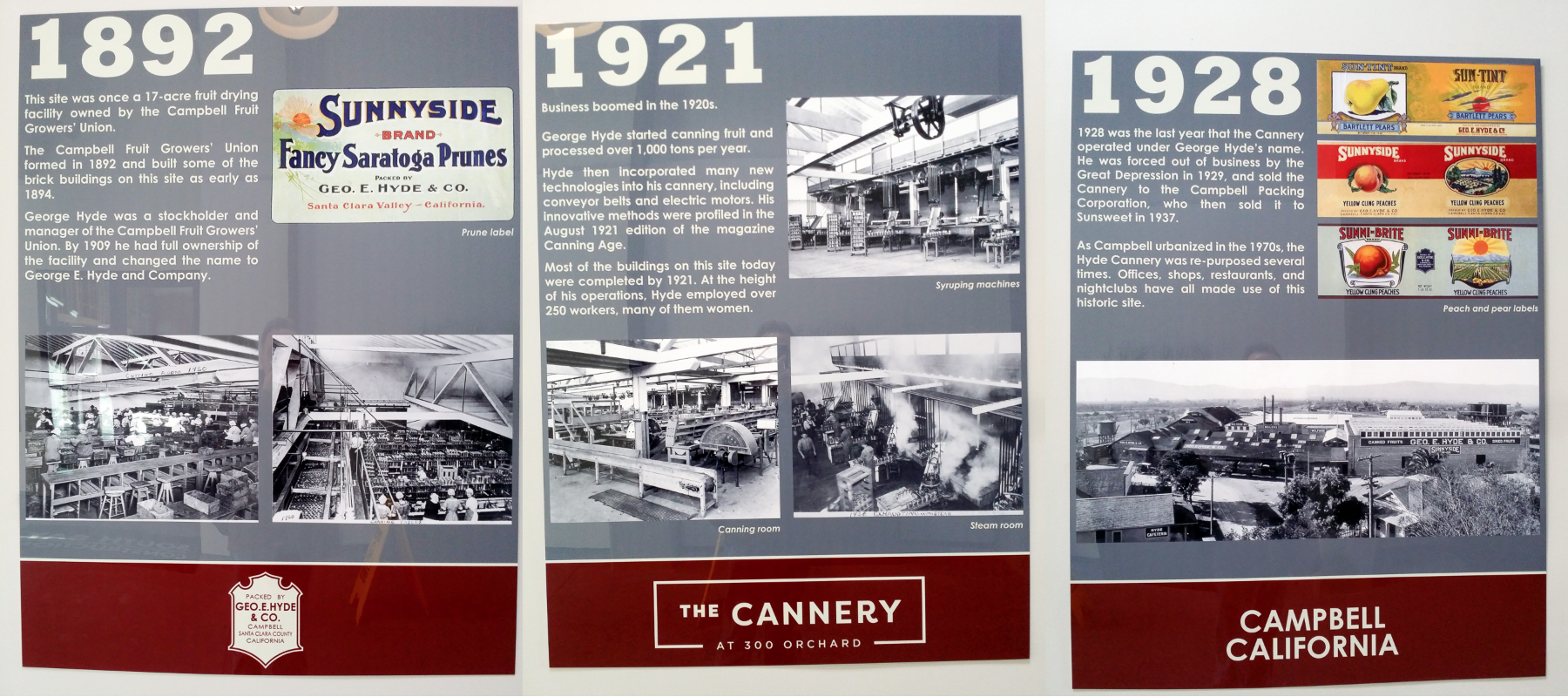

في اليوم الآخر ، قام عمدة كامبل ، يحمل الاسم الروسي بول ريسنيكوف ، بقص الشريط عند افتتاح مكتب بدء التشغيل الجديد لشركة Wave Computing ، والذي يعمل مع شركة Broadcom على تطوير شريحة من 7 نانومتر لتسريع حساب الشبكات العصبية. يقع المكتب في مبنى مصنع الفواكه والتعليب التاريخي في أواخر القرن التاسع عشر وأوائل القرن العشرين ، عندما كان وادي السيليكون أكبر بستان في العالم. على الرغم من ذلك ، كان المكتب يعمل في مجال الابتكار ، حيث تم تقديم أول محرك كهربائي في صناعة المشمش البرقوق للناقلات ، والذي يعمل فيه حوالي 200 موظف ، معظمهم من النساء.

في الحفلة التي تلت قطع الشريط ، تم تسليط الضوء على العديد من الأشخاص المشهورين في الصناعة ، بما في ذلك رفيق Kernigan-Richie في الأسلحة ومؤلف كتاب المترجم C الأكثر شهرة في أواخر السبعينيات - أوائل الثمانينيات ، ستيفن جونسون ، أحد مؤلفي رقم النقطة العائمة جيروم كونين ، المخترع مفاهيم الحافلات المحلية وأول شركة مطورة لمجموعة شرائح الكمبيوتر AT Diosdado Banatao والمطورين السابقين لمعالجات Sun و DEC و Cyrix و Intel و AMD و Silicon Graphics و Qualcomm و Xilinx و Cypress والمحللين الصناعيين وهي فتاة ذات شعر أحمر وغيرهم من سكان كاليفورنيا mpany من هذا النوع.

في نهاية المنشور ، سنتحدث عن الكتب التي يجب قراءتها وتمارين القيام بها من أجل الانضمام إلى هذا المجتمع.

لنبدأ مع Jerome Kunen ، وهو مبتكر في حساب النقطة العائمة ومدير Apple منذ نظام Macintosh الأول.

أطروحات المرشحين ليست شائعة بحيث تؤثر على الحوسبة على مليارات الأجهزة. هذا ما أصبحت عليه Jerome Kunen Diser (مساهمات في معيار مقترح لحساب النقطة العائمة الثنائية) ، وقد تم تضمين نتائجها في أرقام الفاصلة العائمة IEEE Standard 754. بعد تخرجه من كلية الدراسات العليا في بيركلي في عام 1982 ، ذهب جيروم للعمل في شركة آبل ، حيث قدم مكتبة الفاصلة العائمة في أول ماكنتوش.

بعد 10 سنوات من الإدارة في شركة Apple ، تشاورت Kunen مع Hewlett-Packard و Microsoft ، وفي عام 2000 قامت بتحسين حساب 128 بت لإصدار 64 بت x86 الجديد من AMD. حول جيروم انتباهه مؤخرًا إلى البحث عن معايير الفاصلة العائمة للشبكات العصبية ، وخاصة النزاعات حول Unum و Posit. Unum هو المعيار الجديد المقترح ، الذي روج له العالم من Caltech John Gustafson ، مؤلف كتاب "نهاية الخطأ" ، "نهاية الخطأ". Posit هو إصدار من Unum يمكن تنفيذه بشكل أكثر كفاءة (*) من Unum في الأجهزة.

(*) أكثر كفاءة في الجمع بين المعلمات: تردد الساعة ، عدد الدورات لكل عملية ، إنتاجية الناقل ، المنطقة النسبية على الشريحة واستهلاك الطاقة النسبي.

صور من المقالات (وليس من جيروم)

مما يجعل الرياضيات العائمة نقطة كفاءة عالية لأجهزة AI و

التغلب على النقطة العائمة في لعبتها: Posit Arithmetic لـ John L. Gustafson و Isaac Yonemoto :

ولكن في الحفل ستيفن / ستيف جونسون هو الشخص الذي أصبحت لغة برمجة لغة C له شعبية في الترجمة. أول مترجم جيم كتبه دينيس ريتشي ، ولكن كان مترجم ريتشي مرتبط بإحكام ببنية PDP-11. كتب ستيف جونسون ، استنادًا إلى أعمال آلان سنايدر ، في منتصف السبعينيات من القرن العشرين "المترجم المحمول سي" (PCC) ، الذي كان من السهل إعادة صنعه لإنشاء شفرة لمختلف البنى. في الوقت نفسه ، عملت مترجم جونسون بسرعة وكان الأمثل. كيف حقق هذا؟

عند إدخال PCC ، استخدم Steve Johnson المحلل اللغوي LALR (1) الذي تم إنشاؤه بواسطة YACC (مترجم مترجم آخر) ، كما قام بتأليفه ستيف جونسون. بعد ذلك ، تم تقليل مهمة الترجمة إلى معالجة الأشجار في الوظائف العودية وإنشاء تعليمة برمجية من جدول القالب. بعض هذه الوظائف العودية كانت مستقلة عن الآلة ، والجزء الآخر كتبه أشخاص نقلوا PCC إلى جهاز آخر. يتكون جدول القالب من إدخالات قاعدة من النوع "إذا كان سجل من النوع A وسجليين من النوع B مجانيان ، فقم بإعادة إنشاء الشجرة في عقدة من النوع C وإنشاء رمز باستخدام سلسلة D". كان الجدول يعتمد الجهاز.

نظرًا للجمع بين الأناقة والمرونة والكفاءة ، تم نقل برنامج التحويل البرمجي PCC إلى أكثر من 200 بنية - من PDP و VAX و IBM / 370 و x86 إلى BESM-6 و Orbit 20-700 السوفيتي (كمبيوتر متصل على متن الطائرة في الإصدارات الأولى من MiG-29). وفقًا لدنيس ريتشي ، كان كل مترجم سي تقريبًا في أوائل الثمانينات يعتمد على PCC. من عالم BSD Unix ، تم استبدال PCC كمترجم GNU GCC القياسي فقط في عام 1994.

بالإضافة إلى PCC و Yacc ، يعد Steve Johnson أيضًا مؤلف برنامج التحقق من برنامج Lint الأصلي (انظر ، على سبيل المثال ،

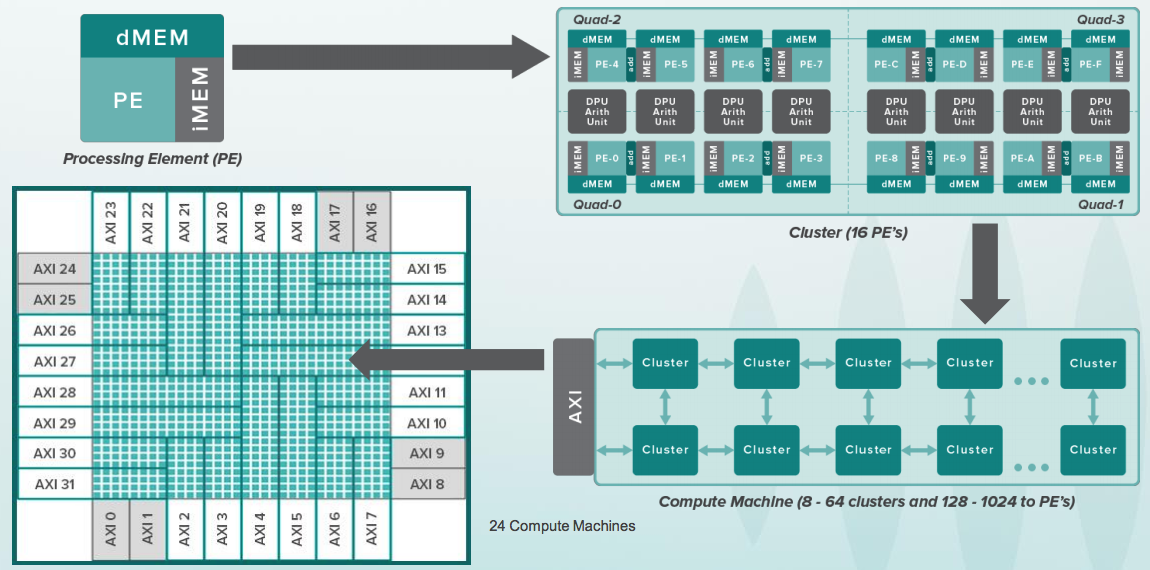

مقالة 1978 ). أصبحت أسماء برامج Yacc و Lint أسماء مشتركة. في 2000s ، أعاد ستيف كتابة الواجهة الأمامية لـ MATLAB وكتب MLint. الآن ، أصبح ستيف جون مشغولاً بمهمة موازاة الخوارزميات لحساب الشبكات العصبية على أجهزة مثل CGRA (الهندسة القاسية لإعادة التكوين) ، مع عشرات الآلاف من العناصر الشبيهة بالمعالجات التي امتدت عبر التنسورات عبر شبكة من عشرات الآلاف من المحولات داخل شريحة ضخمة تضم مليارات الترانزستورات:

ولكن مع كوب من النبيذ ، الملياردير ديوسدادو باناتاو ، مؤسس Chips & Technologies ، S3 Graphics والمستثمر في مارفيل. إذا قمت ببرمجة كمبيوتر IBM في 1985-1988 ، عندما ظهرت لأول مرة في اتحاد الجمهوريات الاشتراكية السوفياتية ، فربما تعلم أنه في معظم أوراق AT مع رسومات EGA و VGA ، كانت هناك شرائح من Chips & Technologies ، والتي صدرت في وقت واحد مع IBM. تم تصميم شرائح C&T المبكرة بواسطة Banatao ، الذي تعلم أنه مهندس إلكترونيات في جامعة ستانفورد ، وقبل أن يعمل ستانفورد كمهندس في شركة Boeing. في عام 1987 ، استحوذت Intel على Chips & Technologies.

على اليسار في الصورة أدناه جون بورغون ، رئيس MIPS Technologies منذ ذروته في 2000s ، عندما كانت شرائح MIPS النوى داخل معظم مشغلات أقراص الفيديو الرقمية والكاميرات الرقمية وأجهزة التلفزيون ، مع شرائح من Zoran ، Sigma Design ، Realtek و Broadcom وغيرها من الشركات. قبل ذلك ، كان جون رئيسًا لـ MIPS Silicon Graphics منذ عام 1996 ، عندما كانت معالجات MIPS داخل محطات عمل Silicon Graphics التي استخدمتها هوليوود لتصوير أول أفلام واقعية ثلاثية الأبعاد Jurassic Park. قبل شركة Silicon Graphics ، كان جون أحد نواب رئيس AMD منذ عام 1976.

كان آرت سويفت ، نائبًا رئيسًا للتسويق في MIPS في عام 2000 ، وقبل ذلك في الثمانينيات عمل مهندسًا في شركة فيرتشايلد لأشباه الموصلات (نعم ، ذلك) ، ثم نائب رئيس قسم التسويق في شركة Sun و DEC و Cirrus Logic و رئيس Transmet. في الآونة الأخيرة ، كان Art نائبًا لرئيس لجنة التسويق RISC-V وكان على دراية بـ Syntacore و CloudBear في روسيا في هذا المنصب. والآن أصبح رئيس Wave's MIPS IP:

الشرائح من

العرض التقديمي حول تاريخ MIPS تتعلق بالفترة التي كان يسيطر فيها جون بورغون على MIPS ، في الصورة أعلاه إلى اليسار:

أصدرت شركة Transmet ، التي كان رئيسها Art Swift لبعض الوقت ، في الصورة أعلاه على اليمين ، معالج Crusoe في أواخر التسعينيات ، والتي يمكن أن تتبع تعليمات x86 ووصلت إلى السوق في أجهزة الكمبيوتر المحمولة الفرعية Toshiba Libretto L و NEC و Sharp ، عميل رفيع من كومباك. تم تعيين ميزتهم التنافسية على Intel و AMD للتحكم في استهلاك الطاقة المنخفض.

يعد التنفيذ والتحقق المباشر لمجموعة x86 الكاملة إجراءً مكلفًا للغاية ، لذا فإن Transmeta ذهب في الاتجاه الآخر ، والذي يشبه مسار شركة MTsST الروسية بمعالج Elbrus (الخط الذي بدأ بـ Elbrus 2000 ويتم تقديمه الآن باسم Elbrus 8C). استندت Transmeta و Elbrus على معالج بسيط من الناحية الهيكلية بهندسة VLIW الدقيقة ، وعمل مستوى مضاهاة x86 فوقه باستخدام التكنولوجيا التي أطلق عليها Transmeta رمز التكويد.

إن فكرة VLIW (كلمة التعليمات الطويلة جدًا) بسيطة جدًا - يتم إعلان العديد من إرشادات المعالج صراحة على أنها تعليمة فائقة واحدة ويتم تنفيذها بالتوازي. على عكس المعالجات الفائقة ، خاصةً Intel التي تبدأ بـ PentiumPro (1996) ، حيث يختار المعالج العديد من الإرشادات من الذاكرة ، ثم يقرر ما يجب تنفيذه بشكل متوازٍ وما بالتسلسل ، بناءً على تحليل تلقائي للتبعيات بين الإرشادات.

يعد المعالج الفائق المعقد أكثر تعقيدًا من VLIW ، لأنه يتعين على المستوى الفائق إنفاق منطق على الحفاظ على وهم مبرمج بتنفيذ جميع التعليمات المحددة واحدة تلو الأخرى ، رغم أنه في الواقع يمكن أن يوجد العشرات منها داخل المعالج ، في مراحل مختلفة من التنفيذ. في حالة VLIW ، يقع عبء الحفاظ على مثل هذا الوهم على المترجم من لغة عالية المستوى. في النهاية ، تتعطل دائرة VLIW عندما يتعين على المعالج العمل مع ذاكرة تخزين مؤقت متعددة المستويات ، والتي لها تأخيرات غير متوقعة تجعل من الصعب على المحول البرمجي جدولة تعليمات الساعة. ولكن بالنسبة للحسابات الرياضية (على سبيل المثال ، وضع Elbrus على الرادار وحساب حركة الهدف) هذا هو الشيء ، خاصةً في ظروف النقص في الكوادر الهندسية المؤهلة (يحتاج المزيد من الناس إلى التحقق من المستوى الفائق).

شكل توضيحي لفكرة VLIW ومعالج Crusoe وجهاز الكمبيوتر المحمول Toshiba Libretto L1 الفرعي:

وهنا في وسط الصورة أدناه ديريك ماير ، ديريك ماير ، الرئيس التنفيذي الحالي لشركة Wave Computing. قبل Wave ، شغل ديريك منصب الرئيس التنفيذي لشركة ARC ، وهو مطور لقلب معالجات ARC المستخدمة في شرائح الصوت. تم

ترخيص هذه النوى

في ذلك الوقت

، بما في ذلك من قِبل الشركة الروسية NIIMA Progress ، التي قامت بعد ذلك بترخيص النوى MIPS

وعرضت رقائق تستند إليها في معرض في كازان إنوبوليس . سافر ديريك ماير مرارًا وتكرارًا إلى روسيا ، إلى سان بطرسبرغ ، حيث يوجد فريق التطوير التابع لشركة Virage Logic. في عام 2009 ، استحوذت ARC على Virage Logic ، وفي عام 2010 ، استحوذت شركة Synopsys ، الشركة الرائدة عالمياً في مجال تصميم الرقاقات ، على ARC.

على اليمين في الصورة - عمل

سيرجي فاكولينكو ، الذي كان واقفًا في مطلع مسيرته في أصول Runet ، في Demos التعاونية ومعهد Kurchatov ، الذي أوصل الإنترنت إلى الاتحاد السوفيتي. يكتب سيرجي الآن نموذجًا دقيقًا للدورة لعنصر المعالج Wave لحساب الشبكات العصبية ، وكان قد كتب في وقت سابق نماذج دقيقة للتعليمات عن نوى MIPS التي تم استخدامها للتحقق من نوى معالج MIPS I6400 Samurai و I7200 Shaolin وغيرها.

هنا هو Vadim Antonov و Sergey Vakulenko في عام 1990 ، مع أول جهاز كمبيوتر في اتحاد الجمهوريات الاشتراكية السوفياتية متصل بالإنترنت:

وهنا لاري هوديبول على اليمين (هودبول مكتوبة باللغة الروسية؟). بدأ لاري حياته المهنية في شركة Digital Equipment Corporation (DEC) كمصمم لمعالج MicroVAX. ثم عمل لاري في شركة صغيرة Cyrix ، والتي تحدت إنتل في أواخر الثمانينيات من القرن الماضي وجعلت معالجات FPU متوافقة مع Intel 80387 وكانت أسرع بنسبة 50 ٪. ثم صمم لاري رقائق MIPS في Silicon Graphics. عندما انفصلت MIPS Technologies عن Silicon Graphics ، أطلقت Larry و Ryan Quinter معاً أول منتج مستقل لـ MIPS ، MIPS 4K ، الذي أصبح العمود الفقري للخط الذي سيطر على الإلكترونيات المنزلية في الألفية الثانية (مشغلات DVD والكاميرات وأجهزة التلفزيون الرقمية). ثم طار MIPS 5K إلى الفضاء - تم استخدامه من قبل وكالة الفضاء اليابانية JAXA. ثم قاد لاري ، بصفته VP Hardware Engineering ، عملية تطوير الخطوط التالية ، وهو يعمل الآن على بنيات تسريع Wave الجديدة.

يتم التحكم في سفينة الفضاء اليابانية ، التي تحمل اسم Hayabusa-2 (Sapsan-2) ، والتي

هبطت على سطح كويكب ريوجو العام الماضي ، بواسطة معالج HR5000 على أساس المعالج MIPS 5Kf ، والذي تم ترخيصه لفترة طويلة من قبل MIPS Technologies.

فيما يلي خط أنابيب تسلسلي بسيط لمجموعة المعالجات MIPS 5Kf ذات 64 بت من

ورقة البيانات الخاصة بها :

الحق في الصورة - دارين جونز ، دارين جونز. وكان مدير هندسة الأجهزة في MIPS ، الذي قاد تطوير النوى المعقدة ، مع تعدد الأجهزة ، و superscalars مع التنفيذ الاستثنائي للتعليمات. ثم ذهب دارين إلى Xilinx ، حيث شارك في رقائق Xilinx Zynq ، والتي تقف عليها مجموعة من المعالجات FPGAs و ARM. دارين هو الآن نائب رئيس قسم الهندسة في Wave.

في MIPS ، كان دارين قائد مجموعة ذهب أعضاؤها فيما بعد إلى Apple و Samsung. أخبرتني المصممة مونيكا ، التي ذهبت إلى شركة سامسونج ، ذات مرة عبارة "تذكرتها جيدًا:" تصميم RTL: بعض المبادئ البسيطة والباقي تغش "(تطوير المعدات على مستوى عمليات نقل السجلات: بعض المبادئ البسيطة ، كل شيء آخر هو muhlezh") من الأمثلة المعتادة على muhlezh ذاكرة التخزين المؤقت (قام البرنامج بكتابة البيانات وقراءتها ، ولكن لن يتم تذكرها إلا في وقت لاحق) ، ولكن هذه مجرد حالة خاصة جدًا لما تمكنت Monica من فعله.

تعدد مؤشرات الأجهزة و superscalar غير عادية طريقتان مختلفتان لتحسين أداء المعالج. يتيح لك تعدد مؤشرات الأجهزة زيادة الإنتاجية دون استهلاك الكثير من الطاقة ، ولكن مع البرمجة غير التافهة. يتيح لك superscalar تشغيل برامج ذات سلاسل مفردة تقريبًا ضعف السرعة ، ولكنه أيضًا ينفق ضعف عدد الواط. ولكن من دون حيل في البرمجة.

أخيرًا ، تم شرح تعدد مؤشرات الأجهزة بشكل جيد في ويكيبيديا الروسية ، وهنا

تعدد مؤشراته

المؤقتة (يتم تطبيقه في MIPS interAptiv و MIPS I7200 Shaolin) ، ولكن

تعدد مؤشرات الترابط المتزامن (تم إجراؤه في معالجات DEC Alpha في التسعينات ، ثم في SPARC ، MIPS I6400 Samurai / I6500 Daimyo).

تعدد مؤشرات الترابط المؤقتة يستغل حقيقة أن معالج بخط أنابيب تسلسلي تقليدي يكون خاملاً / في انتظار نصف وقت التنفيذ. ماذا ينتظر؟ البيانات التي تمر عبر ذاكرة التخزين المؤقت. وينتظر وقتًا طويلاً - أثناء انتظار تفويت ذاكرة التخزين المؤقت ، يمكن للمعالج تنفيذ العشرات أو حتى مائة أو إرشادات حسابية بسيطة مثل الإضافة.

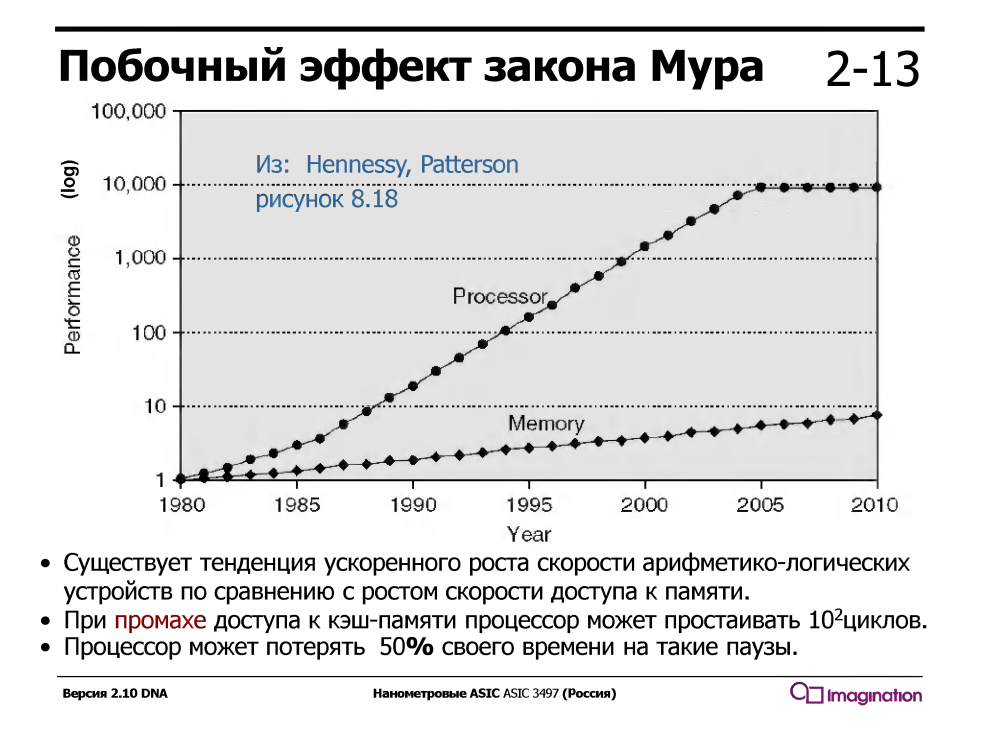

لم يكن هذا هو الحال دائمًا - في الستينيات ، كانت الأجهزة الحسابية أبطأ بكثير من الذاكرة. ولكن منذ عام 1980 تقريبًا ، نمت سرعة نوى المعالجات أسرع بكثير من سرعة الذاكرة ، وحتى ظهور ذاكرة التخزين المؤقت متعدد المستويات في المعالجات لم يحل المشكلة جزئيًا.

تدعم المعالجات ذات مؤشرات الترابط المؤقتة عدة مجموعات من السجلات ، واحدة لكل مؤشر ترابط ، وعندما ينتظر مؤشر الترابط الحالي بيانات من الذاكرة أثناء ذاكرة التخزين المؤقت ، يتحول المعالج إلى مؤشر ترابط آخر. يحدث هذا على الفور ، في دورة ، دون انقطاع والآلاف من دورات معالج المقاطعة ، والتي يتم تنشيطها أثناء تعدد البرامج (وليس الأجهزة).

إليكم فكرة الخيوط المتعددة

على الشرائح من ورش عمل تشارلز دانشيك ، الأستاذ في جامعة كاليفورنيا سانتا كروز ، امتداد وادي السيليكون. لماذا باللغة الروسية؟ لأن Charles Danchek ألقى محاضرات في MISiS في موسكو ، ثم في St. Petersburg ITMO و Kiev KPI:

ومن المثير للاهتمام ، يمكن برمجة الأجهزة متعددة الخيوط ببساطة في C. إليك ما يبدو عليه:

#include "mips/m32c0.h" #include "mips/mt.h" #include "mips/mips34k.h"

هنا على جانب الحفلة يوجد جهاز Wave لمراكز البيانات. لا يعمل بشكل كامل حتى الآن ، على الرغم من أن الرقائق متاحة لبعض العملاء كجزء من برنامج بيتا:

ماذا يفعل هذا الجهاز؟ هل تعرف كيفية البرنامج في بيثون؟ هنا في Python ، يمكنك البناء باستخدام مكتبة TensorFlow باستدعاء ما يسمى Data Flow Graph (DFG). الشبكات العصبية هي أساسا مثل هذه الرسوم البيانية المتخصصة مع عمليات على المصفوفات. في مجموعة برامج Wave ، والتي يتولى قيادة جزء منها ستيف جونسون ، يوجد مترجم مع مجموعة فرعية من تمثيل Google TensorFlow في ملفات التكوين الخاصة بشرائح هذا الجهاز. بعد التكوين ، يمكن أن تفعل حساب هذه الرسوم البيانية بسرعة كبيرة. تم تصميم الجهاز لمراكز البيانات ، ولكن يمكن تطبيق نفس المبدأ على الرقائق الصغيرة ، حتى داخل الأجهزة المحمولة ، على سبيل المثال للتعرف على الوجوه:

Chijioke Anyanwu (يسار) - لعدة سنوات ، كان الوصي على نظام اختبار المعالجات MIPS بأكمله. Baldwyn Chieh (في الوسط) هو مصمم الجيل الجديد من العناصر الشبيهة بالمعالج في Wave. اعتاد بالدوين أن يكون مصممًا كبيرًا في كوالكوم. فيما يلي

الشرائح الخاصة بجهاز Wave من مؤتمر HotChips :

يجب أن يكون لمنظمة العفو الدولية ، كل ابتكار رقمي نانومتر لكل شركة في سيليكون فالي ، فتاة خاصة بها ذات شعر لامع. هنا هذه الفتاة في الموجة. اسمها هو أثينا ، وهي أخصائية اجتماعية في التعليم ، وتشارك في مكتب المكتب:

وإليك كيف يبدو المكتب من الخارج وتاريخه الذي يمتد لأكثر من قرن من الزمان عندما كان مصنع تعليب مبتكرًا:

والسؤال المطروح الآن هو: كيف نفهم العمارة والبنية الدقيقة والدوائر الرقمية ومبادئ تصميم رقائق الذكاء الاصطناعي والمشاركة في مثل هذه الأطراف؟ أسهل طريقة هي دراسة كتاب "الدائرة الرقمية وهندسة الكمبيوتر" لديفيد هاريس وسارة هاريس ، والذهاب إلى Wave Computing للمتدربين الصيفي (من المخطط استئجار 15 متدربًا للصيف). آمل أن يتم ذلك أيضًا في الشركات الإلكترونية الصغيرة الروسية التي تعمل في تطورات مماثلة - ELVIS ، و Milander ، و Baikal Electronics ، و IVA Technologies ، والعديد من الشركات الأخرى. في كييف ، يمكن القيام بذلك نظريًا في شركة Melexis ، التي تتعاون مع KPI.

في اليوم الآخر ، تم إصدار نسخة جديدة تم تصحيحها أخيرًا من الكتاب المدرسي Harris & Harris ، والتي يجب أن تكون مجانية هنا

www.mips.com/downloads/digital-design-and-computer-architecture-russian-edition-second-edition-ver3 ، لكن هذا الرابط لا يصلح لي ، وعندما يعمل ، سأكتب منشورًا منفصلًا عنه. مع الأسئلة التي طرحت أثناء المقابلات في Apple و Intel و AMD ، وعلى أي صفحات من هذا الكتاب المدرسي (والمصادر الأخرى) ، يمكنك رؤية الإجابات.