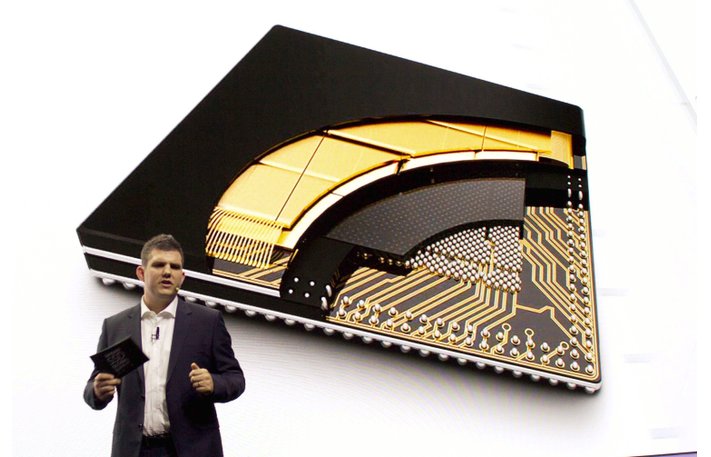

إنتل فوفروس 3D

إنتل فوفروس 3Dنظرًا لأن قانون مور لم يعد مطبقًا ، يتعين على مصممي الرقائق البحث عن طرق أخرى لتحسين الأداء. تقنية واحدة مناسبة لذلك تسمى تكديس الرقاقات ثلاثية الأبعاد. هذا هو بنية مكدس ثلاثية الأبعاد من رقائق ، في تطوير Intel التي هي الرائدة. قبل شهرين ، قدمت Intel بنية

Foveros ثلاثية الأبعاد : هيكل ثلاثي الأبعاد ، يتضمن تقنية معالجة تبلغ 10 نانومتر ، وشريحة إدخال / إخراج ووصلة TSV (عبر Silicon Via) في وسط الشريحة ، وشريحة ذاكرة أعلى الشريحة بالكامل.

في مؤتمر الحوسبة عالية الأداء Rice Oil and Gas HPC ،

أكدت AMD أنها تعمل على نسختها الخاصة من بنية الشريحة ثلاثية الأبعاد.

وقال فورست نورود ، نائب الرئيس الأول والمدير العام ، إن الشركة تطور العديد من التقنيات لزيادة العوائد وتجاوز المشاكل المرتبطة بإنهاء قانون مور والعواقب المترتبة على وقف نمو كثافة الترانزستور وتردد الساعة. هذه عواقب لا يمكن تجنبها عندما يقترب المصنعون من الحد الذي يكون فيه حجم الترانزستور بضع ذرات فقط (حجم ذرة السليكون 0.2 نانومتر). إن نمو قوة الكمبيوتر في السنوات الأخيرة لم يكن ناتجًا عن زيادة في سرعة الحوسبة ، بل عن زيادة في التوازي.

مثل الشركات الأخرى ، واجهت AMD قيودًا على مساحة الرقاقة التي تبلغ حوالي 700 ملم مربع ، وهي مضطرة لتطوير بنية ثلاثية الأبعاد. تتبع الشركة بالفعل هذا النهج ، حيث تضع ذاكرة HBM2 بجانب الركيزة GPU ، أي أنها في نفس الحالة مثل المعالج. ولكن في المستقبل ، تخطط الشركة للانتقال إلى التراص ثلاثي الأبعاد الأكثر تقدماً.

قال Norrod إن AMD تعمل على وضع SRAM و DRAM مباشرة على رأس مكونات الحوسبة (مثل المعالجات ووحدات معالجة الرسومات) لتوفير المزيد من النطاق الترددي والأداء.

سامسونج بولاريس

سامسونج بولاريسيختلف هذا النهج عن التطبيقات المعتادة للحزم (PoP) ، والتي تضع ببساطة حالتين منتهية فوق بعضها البعض ، كما أظهر Norrod باستخدام شريحة Samsung Polaris كمثال. في هذا المثال ، يتم توصيل حاوية DRAM من خلال صفين إضافيين لموصلات BGA التي تحيط بالشريحة الأساسية. تقوم موصلات BGA هذه بنقل البيانات بين شريحتين. كما هو الحال مع أي تصميم قياسي ، يكون المنطق في أسفل الرصة نظرًا للحاجة إلى مزيد من الموصلات ، لكن البلورين غير متصلين مباشرة. وبالتالي ، يوفر نهج PoP أقصى كثافة ، ولكن هذا ليس هو الخيار الأسرع.

في حالة التراص ثلاثي الأبعاد الحقيقي ، توجد شريحتان (في هذه الحالة ، الذاكرة والمعالج) أحدهما فوق الآخر ويتم توصيلهما بواسطة اتصالات TSV رأسية تربطهما مباشرة. تقوم اتصالات TSV بنقل البيانات بين البلورات بأعلى سرعة ممكنة وعادةً ما تكون موجودة في وسط الشريحة ، كما رأينا مع Intel Foveros 3D. يعمل هذا الاقتران المباشر على تحسين الأداء وتقليل استهلاك الطاقة (تتطلب كل حركة البيانات طاقة ، لكن الاتصالات المباشرة تعمل على تحسين العملية). التراص ثلاثي الأبعاد يزيد أيضًا من الكثافة.

لم يدخل Norrod في تفاصيل المشاريع قيد التطوير ، ولكن هذا قد يكون تحولًا جذريًا في تصميم معالج AMD.

قد تتحول تقنية Intel Foveros 3D الجديدة إلى لحظة حاسمة بالنسبة لهذه الصناعة ، لذلك ليس من المستغرب أن نسمع أن AMD تتحرك في هذا الاتجاه ، حسبما

كتب تومز هاردوير .

حتى الآن ، لا توجد تفاصيل تقنية حول تقنية التراص ثلاثي الأبعاد من AMD ، بخلاف ما قاله Forrest Norrod في عرض تقديمي بعنوان قانون العمل فيما بعد مور ، راجع الفيديو أدناه.

ما هي البدائل الأخرى المتاحة للعودة إلى منحنى النمو الأسي الذي تنبأ به جوردون مور؟ لا توجد إجابة واحدة على هذا السؤال. تقوم صناعة أشباه الموصلات بتجربة المواد التي يمكن استخدامها بدلاً من السيليكون. يمكن أن تعمل بعض مواد أشباه الموصلات من النوع الثالث إلى الخامس

عند انخفاض الفولتية وعلى ترددات أعلى من السيليكون ، لكنها لا تجعل الذرات أصغر أو أبطأ من الضوء. القيود المادية لا تزال سارية.

يبقى السؤال كيف ستبرد رقائق ثلاثية الأبعاد في المستقبل. كيف تبرد هذه الرقاقة بفعالية عندما توزع الطاقة من خلالها؟ لن تتمكن الدائرة الكهربائية الصغيرة من نقل الطاقة إلى جميع الدوائر في وقت واحد دون ارتفاع درجة الحرارة. ربما يتعين عليها الاحتفاظ ببعض الأجزاء مفصولة معظم الوقت وتوفير الطاقة لكل جزء فقط أثناء الاستخدام.