في اليوم الآخر ،

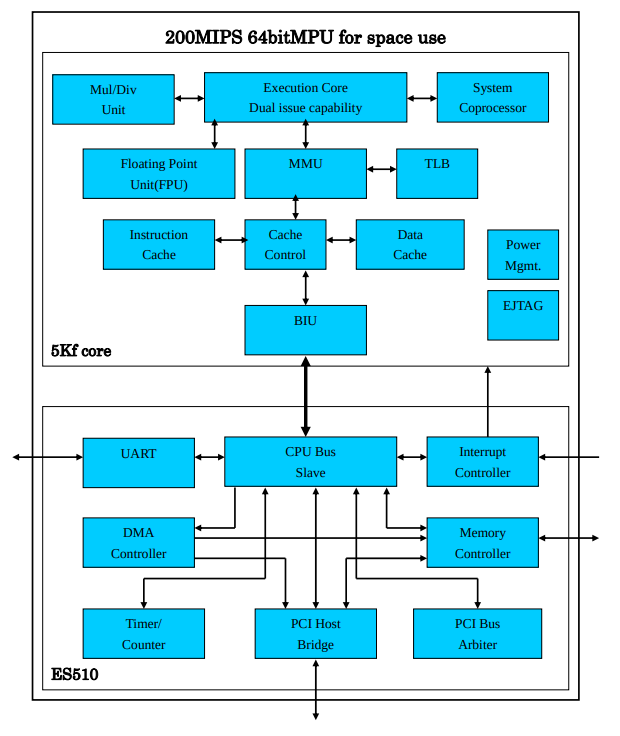

أسقطت محطة يابانية أوتوماتيكية Hayabusa-2 قنبلة على الكويكب ريوجو . يتم التحكم في المركبة الفضائية بواسطة نظام مستقر للإشعاع يعتمد على رقاقة HR5000 (JAXA2010 / 101) مع معالج MIPS 5Kf 64 بت. يدير الكمبيوتر الموجود على متن الطائرة نظام التشغيل uITRON في الوقت الحقيقي ، وهو أحد عائلة RTOS القياسية لـ TRON ، والذي ظهر في اليابان في الثمانينيات

ويستحق وظيفة منفصلة .

في هذه المذكرة ، سوف أصف بإيجاز ما هو مدرج في HR5000 SoC وفي معالجها الأساسي ، وسأعرض صوراً لاثنين من المطورين الرئيسيين لخطوط MIPS 4K و 5 K ، وسأوضح أيضًا كيف يمكنك اللعب في المنزل على FPGA مع "سليل الأخ الأصغر" لهذا الكمبيوتر - نواة MIPS microAptiv UP ذات 32 بت ، والتي يستند رمزها في لغة وصف أجهزة Verilog إلى MIPS 4KEc.

قامت وكالة الفضاء اليابانية JAXA بترخيص مجموعة المعالجات MIPS 5Kf من MIPS Technologies ، وهي شركة أمريكية. حدث هذا مرة أخرى في 2000s. المجموعة التي طورت هذا النواة موجودة في تكوينات مختلفة منذ 40 عامًا:

- أولاً ، في الفترة 1978-1984 ، كان مشروع MIPS في ستانفورد ، بقيادة جون هينيسي. على نجاح هذا المشروع ، أصبح هينيسي مؤلف الكتاب الأكثر شهرة في هندسة الكمبيوتر وفي مرحلة ما - رئيس جامعة ستانفورد.

- في عام 1984 ، أصبحت MIPS شركة تجارية - MIPS Computer Systems. في نفس العام ، تم تسويق ARM أيضًا. في عام 1991 ، أصدرت MIPS أول معالج صغري 64 بت في العالم - MIPS R4000.

- بعد ذلك ، تم استيعاب MIPS بواسطة Silicon Graphics وفي التسعينيات تم استخدامه داخل محطات الرسوم حيث تم إنتاج الأفلام الأولى ذات الرسومات الواقعية في هوليوود (الحديقة الجوراسية).

- في 2000 ، انفصلت المجموعة إلى MIPS Technologies ، وبصورة خاصة ، صممت معالجًا لـ JAXA. يقع المقر الرئيسي لشركة MIPS في كاليفورنيا ؛ حيث يوجد بعض مطوري MIPS 5Kf في MIPS Europe في كوبنهاغن.

- في عام 2012 ، تم شراء MIPS Technologies من قبل شركة Imagination Technologies البريطانية ، التي أصبحت مشهورة كمطور GPU داخل Apple iPhone المبكر.

- في عام 2017 ، قامت Apple بتخيل الخيال ، وبعد بعض الاضطرابات ، تم دمج التكنولوجيا وجزء من مجموعة MIPS في Wave Computing ، وهي شركة ناشئة تعمل على تطوير شريحة لتسريع الشبكات العصبية.

- رقاقة Wave Computing عبارة عن مجموعة من معالجات MIPS I6500 64 بت ومضاعف مصفوفة استنادًا إلى صفيف انقباضي لا يحتوي على Google TPU ، ومعالج معالج بيانات يستند إلى جهاز به بنية معاد تشكيلها ذات بنية خشنة - CGRA ). تقوم المعالجات الكلاسيكية في نظام I6500 بتحميل مضاعف المصفوفة ومعالج دفق البيانات ، ويوفر مضاعف المصفوفة الكثافة الحسابية ، ويقع معالج دفق بيانات المهمة في الوسط بين المعالجات الكلاسيكية ومضاعف المصفوفة - إنه أكثر مرونة من المضاعف وأكثر إنتاجية من وحدة المعالجة المركزية الكلاسيكية.

لذلك التقطت صورة مع أحد المطورين الرئيسيين لخط MIPS 4K و 5 K - لاري هوديبول ، لاري هوديبول (على اليمين في قميص أحمر). بدأ لاري حياته المهنية في شركة Digital Equipment Corporation (DEC) كمصمم لمعالج MicroVAX. ثم عمل لاري في شركة صغيرة Cyrix ، والتي تحدت إنتل في أواخر الثمانينيات من القرن الماضي وجعلت معالجات FPU متوافقة مع Intel 80387 وكانت أسرع بنسبة 50 ٪. ثم صمم لاري رقائق MIPS في Silicon Graphics. عندما انفصلت MIPS Technologies عن Silicon Graphics ، أطلق Larry و Ryan Quinter معاً أول منتج مستقل لـ MIPS ، MIPS 4K ، الذي أصبح العمود الفقري للخط الذي سيطر على الإلكترونيات المنزلية في الألفية الثانية (مشغلات DVD والكاميرات وأجهزة التلفزيون الرقمية). ثم طار MIPS 5K إلى الفضاء - تم استخدامه من قبل وكالة الفضاء اليابانية JAXA. ثم قاد لاري ، بصفته VP Hardware Engineering ، تطوير الخطوط التالية ، وهو يعمل الآن على بنيات تسريع Wave الجديدة:

عاد الآن إلى المعالج في Hayabusa-2 (في Hayabusa-1 كان مختلفًا). فيما يلي

ورقة بيانات لمجموعة المعالجات MIPS64 5Kf وصفحة تحتوي على بيانات النظام على شريحة HR5000 . لاحظ بعض النقاط المثيرة للاهتمام.

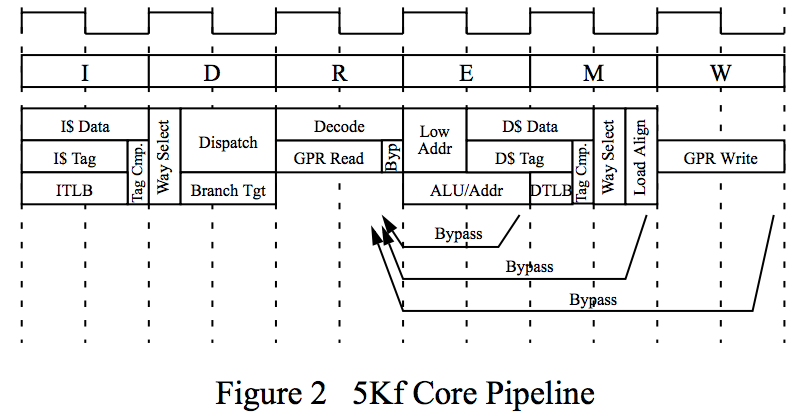

بادئ ذي بدء ، MIPS 5Kf هو معالج ذو خطوط أنابيب. إذا لم تكن على دراية بكيفية عمل ذلك ، فإن أسهل طريقة للتعرف على بعضهم البعض هي دراسة الفصل السابع من كتاب "الدارة الرقمية وهندسة الكمبيوتر" بقلم ديفيد إم هاريس وسارة ل. هاريس ، أحدث نسخة منها يمكن تنزيلها بالروسية

هنا أو

هنا ) . يختلف ناقل الحركة في MIPS 5Kf عن ناقل MIPS الكلاسيكي من Harris & Harris. يمكن لأولئك الذين قرأوا X&X إلقاء نظرة على الاختلافات وتخمين السبب:

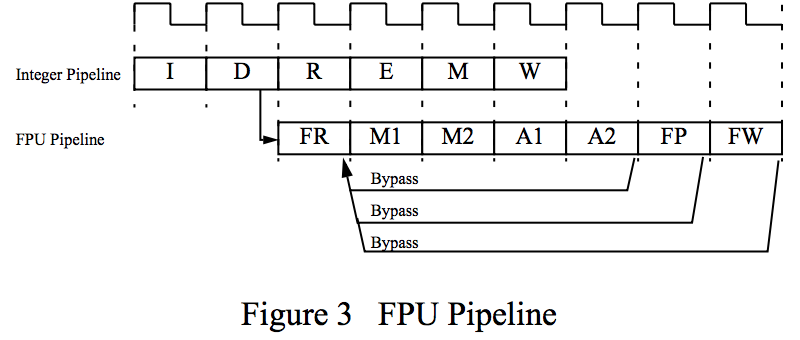

بالطبع ، لا تحتوي MIPS 5Kf على خمس مراحل خطوط أنابيب ، ولكن ست مراحل مع مرحلة إرسال إضافية. هناك حاجة إلى هذه المرحلة لجعل MIPS 5Kf يحدها حدود. لا يمكنها إجراء عمليات واحدة تلو الأخرى في خط الأنابيب ، ولكن يمكنها أيضًا إجراء عملية الفاصلة العائمة في وقت واحد مع تشغيل عدد صحيح أو مع عملية ذاكرة (التحميل أو الحفظ). تقوم شركة Stage Dispatch بإطلاق معالج مساعد للنقاط العائمة يحتوي على خط أنابيب من سبع مراحل:

وهنا على اليمين في الصورة دارين جونز ، دارين جونز ، مطور FPU في MIPS 5Kf. الحرف "f" في "5Kf" يعني بالضبط أنه يحتوي على نقطة عائمة:

هنا في هذه اللوحة ، يمكنك معرفة عدد الدورات التي تتطلب عمليات مختلفة في وحدة FPU وعدد مرات تكرارها (يمكن تكرارها) في خط الأنابيب. على سبيل المثال ، يتطلب الضرب الدقيق الواحد أربع دورات ، ولكن يمكنك بدء عملية ضرب جديدة في خط الأنابيب في كل دورة. لذلك يمكن FPU معالجة أربعة مضاعفات دقة واحدة في وقت واحد في كل مرحلة المعالجة. لكن الضرب المزدوج الدقة يتطلب خمس دورات ، ويمكنك البدء به فقط مع توقف مؤقت في الدورة. تتطلب العملية المعقدة لأخذ الجذر التربيعي للدقة المزدوجة ما يصل إلى 32 دورة ، ويمكنك البدء في أخذ الجذر التربيعي الجديد بعد 29 دورة فقط. هذه هي الطريقة التي يتم بها تحسين حساب إحداثيات السفينة وصيغ الحركة في الفضاء الخارجي:

يستخدم Hayabusa-2 التكوين MIPS 5Kf مع تعليمات منفصلة سعة 32 كيلوبايت وتخزين البيانات. في الوقت نفسه ، لا يتضح من

الوصف المختصر لـ HR5000 ما إذا كان يستخدم ذاكرة تخزين مؤقت بأربع قنوات مكونة من 8 كيلو بايت - أو ذاكرة تخزين مؤقت ثنائية القناة تبلغ 16 كيلو بايت. يمكنك قراءة كيفية عمل هذه ذاكرات التخزين في كل من X&X وفي

عرضي التقديمي القديم حول ذاكرات التخزين المؤقت ، وكذلك في كتاب مفيد

راجع MIPS Run Linux 2nd Edition by Dominic Sweetman:

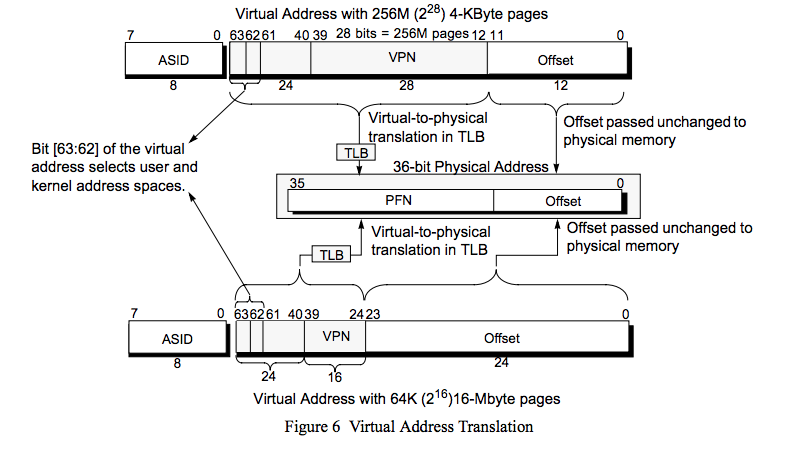

تحتوي Hayabusa-2 أيضًا على وحدة إدارة الذاكرة (MMU) ، مع وجود مخزن مؤقت للغة الترجمة (TLB). TLB هي أداة عالمية لتحويل العناوين بسرعة من الظاهري إلى الفعلي. TLB يتيح لك:

إخفاء ذاكرة نظام التشغيل من رمز غير منقطع.

حماية برامج المستخدم من بعضها البعض.

توفير وصول البرنامج إلى مقدار الذاكرة الظاهرية التي تتجاوز مقدار الذاكرة RAM الفعلية.

معالجة ذاكرة فعلية أكبر من العناوين الافتراضية المتاحة.

ضع البرنامج في أي جزء من الذاكرة الفعلية.

للسماح لمناطق ذاكرة متعددة بالظهور كقطعة متسلسلة.

يتيح لك تحميل أجزاء من البرنامج من جهاز خارجي حسب الحاجة.

يربط TLB أيضًا السمات المختلفة بالعنوان: القراءة والكتابة والتنفيذ ، بالإضافة إلى سمات ذاكرة التخزين المؤقت والتماسك.

هناك حاجة إلى سمة ذاكرة التخزين المؤقت لإظهار المعالج حيث تكون مساحة العنوان لمستوى ذاكرة التخزين المؤقت التالي ، ومكان لمقاومة I / O التي لا يمكن تخزينها مؤقتًا.

هناك حاجة إلى سمات التماسك لعدة نوى المعالج للعمل معًا ، ولكل منها ذاكرة تخزين مؤقت من المستوى الأول ، وتستخدم معًا ذاكرة تخزين مؤقت من المستوى الثاني.

يمكن TLB تخزين مؤشر أنه تم تسجيل صفحة مع عنوان معين. يساعد هذا عند تبديل صفحات الذاكرة وإلغاء تحميلها على أنظمة ذات ذاكرة فعلية أقل مما يحتاج التطبيق إلى معالجة جميع أجزاء التعليمات البرمجية والبيانات الخاصة به بعناوين افتراضية.

هذه هي الطريقة التي تبدو بها ترجمة عنوان ظاهري 64 بت إلى عنوان فعلي 36 بت على MIPS 5Kf. لماذا على Hayabusa-2 معالج 64 بت مع عناوين فعلية 36 بت؟ أظن أن Hayabusa-2 يلتقط صوراً ويتعين عليه معالجة الصور ، الأمر الذي يتطلب الكثير من الذاكرة. ربما بالنسبة لبعض الخوارزميات ، تعمل عمليات تبادل حسابات 64 بت وذاكرة التخزين المؤقت 64 بت (أو عمليات تبادل ذاكرة غير قابلة للتخزين 64 بت) على تحسين شيء ما ، وتبين أن ذلك مفيد في الفضاء. لكنني لا أعرف بالتأكيد ، ربما أحتاج إلى سؤال

Zelenyikot و

amartology ، الذين يعرفون المزيد عن الفضاء أكثر مني.

يمكنك أن تقرأ عن TLB في X&X و See MIPS Run ، لكن هناك فارقًا بسيطًا: يصف كلا الكتابين شكل TLB من وجهة نظر مبرمج. ولكن من وجهة نظر مطور الأجهزة ، فإن مصممي المعالج يخدعون المبرمج من خلال عرضه على TLB كجدول ترجمة ترابطي واحد ، على الرغم من حقيقة أن هناك ثلاثة جداول داخل TL: هناك ثلاثة تعليمات TLB متناهية الصغر ، وبيانات TLB متناهية الصغر ومشتركة (TLB مشترك). أولاً ، يقوم جهاز إدارة الذاكرة بالبحث في ITLB و DTLB ، وفقط إذا لم يعثر عليه ، فإنه يأخذ من JTLB. هذا يكلف المعالج 2 دورات إضافية. راجع أيضًا

العرض التقديمي القديم على TLB :

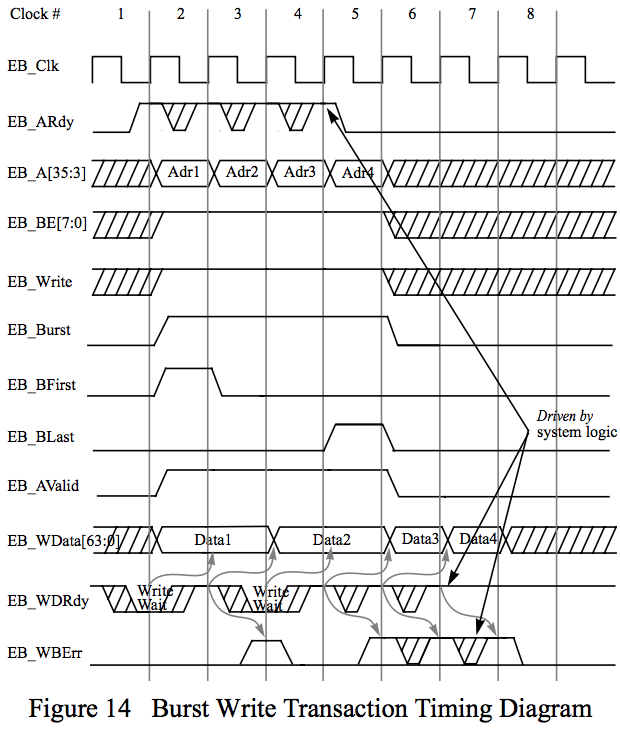

تسمى الواجهة بين ذاكرة التخزين المؤقت من المستوى الأول ووحدة التحكم في الذاكرة في MIPS 5Kf في Hayabusa-2 EB (نطق IB). هذا هو اختصار للحافلة الخارجية. يشبه AHB و AXI ، ويسمح لك أن تنفجر ، تفريغ من ذاكرة التخزين المؤقت ، أو ملء ذاكرة التخزين المؤقت من خط كامل ، باستخدام عمليات النقل في حلقات متسلسلة.

خارج وحدة المعالجة المركزية ، يحتوي HR5000 على وحدة تحكم مقاطعة ووحدة UART ووحدة تحكم وصول مباشر للذاكرة وأجهزة توقيت ووحدة تحكم PCI:

للعمل في الفضاء ، يجب حماية الرقاقة من الإشعاع. لست متخصصًا في مجال الحماية من الإشعاع ، فهناك أمر في

علم أمراض القلب لدى هابري ، لكنني أعلم أن هذه الحماية يمكن القيام بها على مستوى تكنولوجيا الإنتاج المادي ، وعلى مستوى فحوصات ECC المختلفة ، وحتى على مستوى الهندسة المعمارية ، مع وجود ثلاثة أضعاف ، إلخ. قرر مبتكرو نظام بلورات HR5000 استخدام مسار RTL2GDSII المعتاد المعتمد في التطبيقات التجارية ، وتوليف رسم بياني من عناصر منطقية من الكود في لغة وصف أجهزة Verilog. ومع ذلك ، بعد تلقي مثل هذا الرسم البياني (netlist) ، يقومون بتعديله باستخدام مكتبة خاصة من الصلابة حسب التصميم (HBD) (لم تستخدم هذا قط ، لذلك أي توضيح في التعليقات موضع ترحيب):

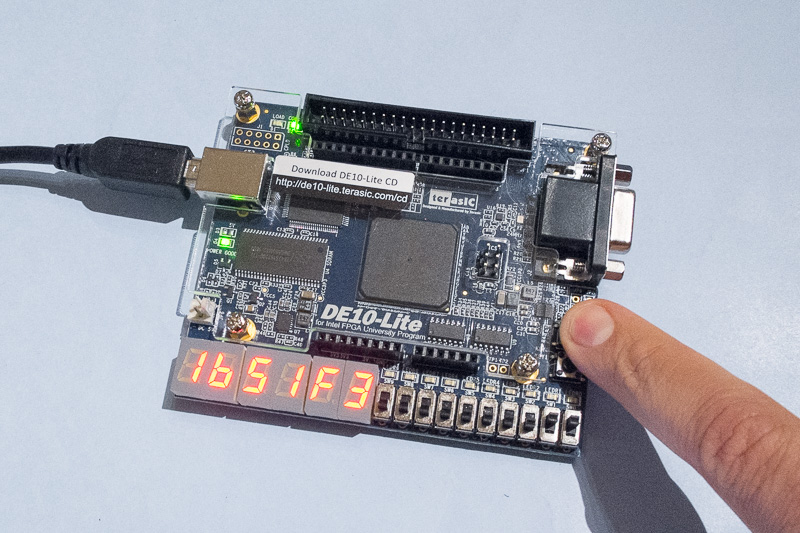

منذ كتابة MIPS 5Kf باللغة Verilog ، يمكن تحويلها ليس فقط إلى netlist ، وليس فقط إلى قناع لتصنيع شريحة في مصنع ، ولكن أيضًا في تكوين FPGA. لسوء الحظ ، فإن مصادر MIPS 5Kf ليست في المجال العام ، ولكن في المجال العام هي مصادر سليل "شقيقه الأصغر" ، معالج MIPS 4K ذي 32 بت. يسمى هذا "السليل" MIPS microAptiv UP ، ويتم تضمين التكوين الأساسي في حزمة MIPSfpga. تمت كتابة رمز MIPS 4K / 4KEc / microAptiv UP / M5150 (هذه كلها إصدارات تقدمية للخط) من قِبل لاري وريان ودارين.

يمكنك اللعب باستخدام خطوط الأنابيب ، ذاكرات التخزين المؤقت ، جهاز إدارة الذاكرة وقطاعات نواة MIPS microAptiv UP ، قم بتشغيلها على جهاز محاكاة أو لوحة مع FPGA / FPGA. للقيام بذلك ، فقط قم بتنزيل

حزمة بدء MIPS Open ™ FPGA ، إلى جانب

MIPS Open ™ FPGA Labs ، و (هذا مهم!)

استكملها مع

MIPSfpga + . في الأخير هناك

مختبرات حول خط أنابيب ، ذاكرة التخزين المؤقت وجهاز إدارة الذاكرة .

يمكنك تجميع وتشغيل معالج MIPS microAptiv UP على لوحة رخيصة بسعر 85 دولارًا (السعر الأكاديمي 55 دولارًا):

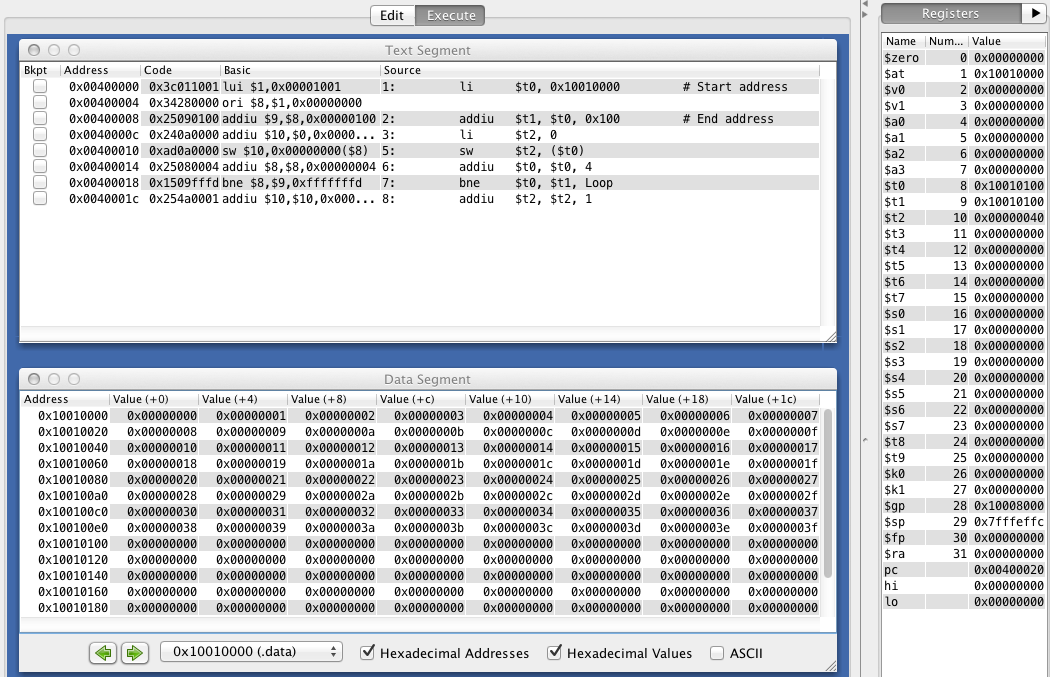

للعمل مع حزمة MIPSfpga / MIPSfpga + ، تحتاج إلى معرفة لغة وصف أجهزة Verilog ومبادئ التصميم على مستوى نقل السجل والقدرة على الكتابة في مجمّع MIPS.

مجمع MIPS هو الأسهل في التعلم. للقيام بذلك ، يمكنك

تنزيل محاكي MARS (MIPS Assembler و Runtime Simulator) . يمكنك معرفة كيفية استخدامه في 5 دقائق ، في الواقع ، هناك ثلاثة أزرار فيه - تجميع ، تشغيل ، تشغيل خطوة بخطوة:

ثم يمكنك قضاء اليوم في ممارسة الكتابة بلغة التجميع للكتب

Harris & Harris و

See MIPS Run Linux .

إذا كنت لا تعرف أي شيء على الإطلاق عن تطوير الدوائر الرقمية بشكل عام وباللغة لوصف المعدات على وجه الخصوص ، فيمكنك البدء في دورة Rosnanov عبر الإنترنت لتلاميذ المدارس ، في ثلاثة أجزاء:

"من الترانزستور إلى الدائرة الصغيرة" ،

"الجانب المنطقي للدوائر الرقمية" ،

"الجانب المادي للدوائر الرقمية" الدوائر الرقمية " ). ثم يمكنك دراسة Verilog على X&X وفهم وجود معالج على معالج

schoolMIPS المبسط.

إذا كنت مهتمًا بهذا الموضوع وترغب في المشاركة في العمل على

MIPS Open (في إطاره تم فتح MIPS microAptiv UP kernel) ، فاكتب في التعليقات. كما تعقد Rosnanovtsy

حلقة دراسية لأطفال المدارس حول التصميم الرقمي في الفترة من 17 إلى 19 أبريل ، والتي ستشمل ، من بين أشياء أخرى ، معالج الفضاء هذا. قصفت Hayabusa-2 ريوغا من دون جدوى - وهذه أيضًا مناسبة لتلاميذ المدارس الروس والطلاب لمعرفة ما بداخلها.