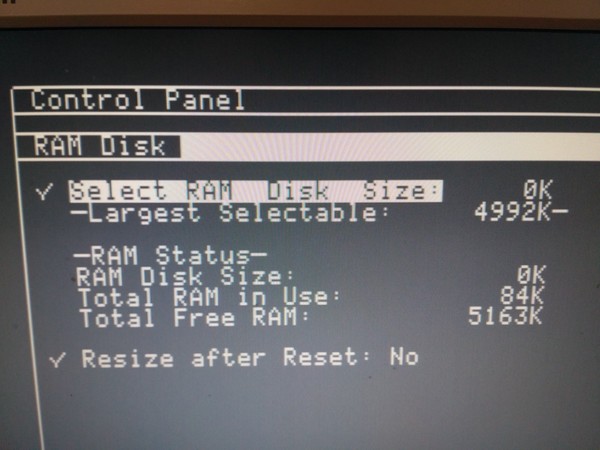

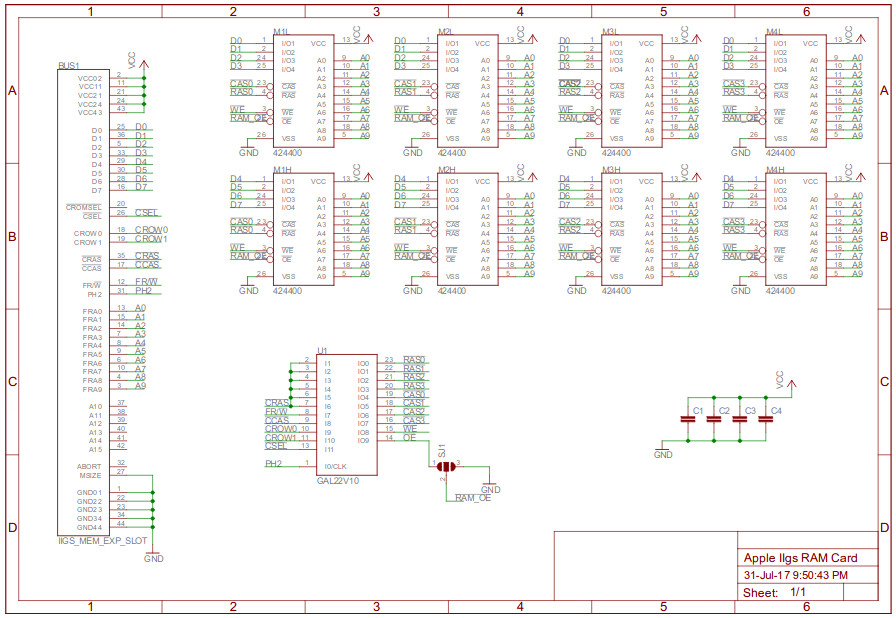

تعتمد لوحة توسيع ذاكرة الوصول العشوائي المقترحة لجهاز Apple IIgs على شرائح NEC uPD424400-70 من عدة وحدات SIMM بسعة 1 ميجابايت. كل من هذه الرقائق تخزّن 1 م من الحلمات وتوضع في علبة من نوع 26 SOJ.

كمبيوتر Apple IIgs مدعوم بمعالج 65C816 - 16 بت ، ولكن باستخدام ناقل بيانات 8 بت. تحتوي بطاقة التوسيع على 4 ميغابايت من ذاكرة الوصول العشوائي. تنقسم الذاكرة إلى أربعة أسطر ، 1 ميجابايت لكل منها. يتكون الخط من شريحتين من 1 M يقضم ، لذلك كان مطلوبًا ما مجموعه ثماني شرائح.

يحتوي الكمبيوتر بالفعل على فتحة لبطاقة توسيع ذاكرة الوصول العشوائي. يعرض جميع الإشارات اللازمة ، كما يهتم الكمبيوتر بتجديد ذاكرة الوصول العشوائي الديناميكية. لذلك ، بطاقة التوسع بسيطة للغاية. قرر المؤلف جعل اللوحة صغيرة الحجم ، نظرًا لأن تكلفة تصنيعها تعتمد على ذلك ، كما وضعت كل المنطق في GAL22V10 FPGA.

الإشارات التالية موجودة على فتحة توسيع ذاكرة الوصول العشوائي:

FRA0-FRA9 - عنوان الخلية المضاعفة 10 بت ، يتم تقديمه مباشرةً إلى مدخلات العنوان الخاصة برقائق RAM الديناميكية

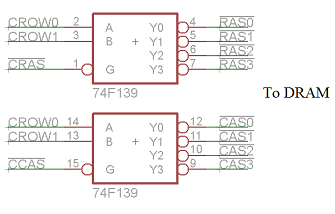

CROW0 ، 1- بتتان لتحديد أحد الأسطر الأربعة

/ CRAS - إشارة خط عنوان القوية من ذاكرة الوصول العشوائي الديناميكية

/ CCAS - إشارة عنوان العمود النابض من ذاكرة الوصول العشوائي الديناميكية

FR / W - إذن الكتابة في RAM ، هذه الإشارة تتطلب معالجة إضافية ، انظر أدناه

D0-D7 - ناقل بيانات ، متصل مباشرة بخطوط الإدخال / الإخراج الخاصة بشرائح RAM

/ CSEL - تظهر وحدة منطقية على هذا السطر عند القراءة من ذاكرة الوصول العشوائي (RAM) ، ويجب قلبها وتزويدها بمدخلات / OE الخاصة برقائق RAM

MSIZE - يخبر جهاز الكمبيوتر بحجم الخط: واحد - 256 كيلو بايت ، صفر - 1 ميجابايت ، هنا يرتبط هذا الخط بسلك شائع

14M ، PH2CLK ، A10-A15 - لا تشارك في اللوحة المقترحة

يجب إزالة إشارة إشارات / CRAS و / CCAS للحصول على إشارات منفصلة / RAS و / CAS لكل سطر. لهذا الغرض ، تعد شريحة 74F139 مناسبة (من المفهوم فيما بعد أنه لن تكون هناك شرائح منفصلة على اللوحة ، بدلاً منها سيكون هناك FPGA مشترك واحد).

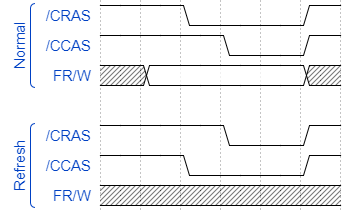

لا يمكن تغذية إشارة FR / W مباشرة بإدخال / WE لشرائح RAM الديناميكية ، ولهذا السبب. في عملية القراءة والكتابة العادية ، يصبح خط / RAS أولاً نشطًا (والذي يتوافق مع الصفر المنطقي) ، ثم سطر / CAS. أثناء دورة تجديد ذاكرة الوصول العشوائي الديناميكية ، على العكس من ذلك ، يصبح خط / CAS نشطًا أولاً ، ثم يصبح / RAS نشطًا. لكن الرقائق المستخدمة تتطلب ظهور وحدة على خط / WE قبل أن يصبح خط / RAS نشطًا. ولا تفي إشارة FR / W الواردة من Apple IIgs بهذا المطلب. حالة FR / W أثناء دورة التجديد غير معروف. لذلك ، يلزم وجود دائرة تكتشف دورة التجديد وتغذي الوحدة بـ / WE.

الخطوة الأولى هي تحديد دورة التجديد. أدناه هو توقيت المخطط:

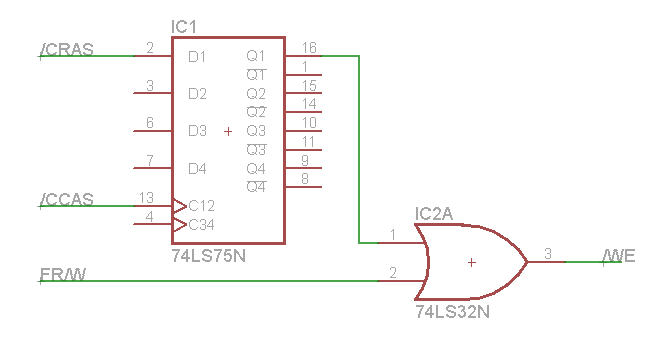

فكرة المؤلف هي استخدام مزلاج "شفاف". إشارة / CRAS لأنها هي إشارة الدخل ، / CCAS هي إشارة مزلاج. عندما تكون الوحدة في وضع التشغيل / CCAS ، يمرر الجهاز إشارة الدخل من خلال نفسه: تتغير حالة الإخراج بعد حالة الإدخال. عندما ينتقل / CCAS من واحد إلى صفر ، يتذكر المزلاج الإشارة عند الإدخال ، والآن لا يتغير عند الإخراج. في عملية القراءة / الكتابة العادية على / CRAS ، يوجد صفر في وقت التبديل / CCAS من واحد إلى صفر. وخلال دورة التجديد على / CRAS ، هناك واحدة أيضًا في لحظة التبديل / CCAS إلى الصفر. ثم ، عندما يعود / CCAS إلى واحد ، يصبح المزلاج شفافًا مرة أخرى. إنه يذكر زهرة رائعة من "أسرار الكوكب الثالث" ، والتي يمكن أن تكون "مرآة" و "كاميرا" على حد سواء.

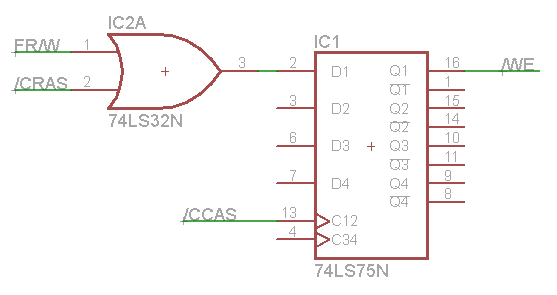

في البداية ، وضع المؤلف المخطط التالي:

ولكن لنقلها إلى GAL22V10 FPGA ، هناك حاجة إلى دبابيس الإخراج اثنين. لذلك ، كان مخطط أن تكون مبسطة. أثناء التشغيل العادي ، تأخذ إشارة FR / W القيمة المطلوبة إلى أن تنقر ، لذلك هذا ممكن أيضًا.

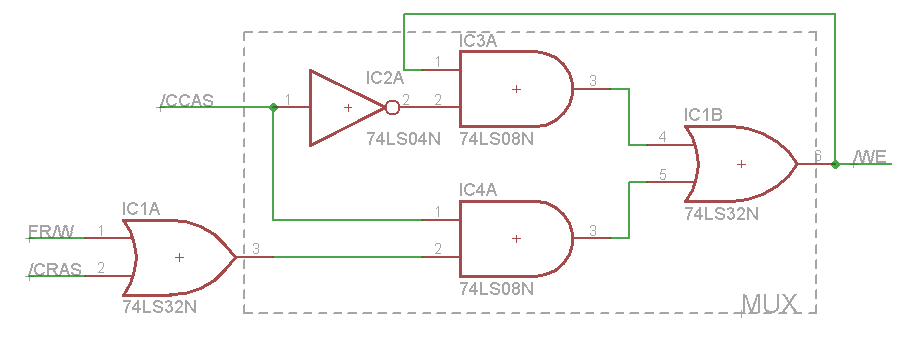

يمكن صنع مزلاج "شفاف" من مُضاعِف ، بدوره ، من عناصر منطقية. المخطط يصبح مثل هذا:

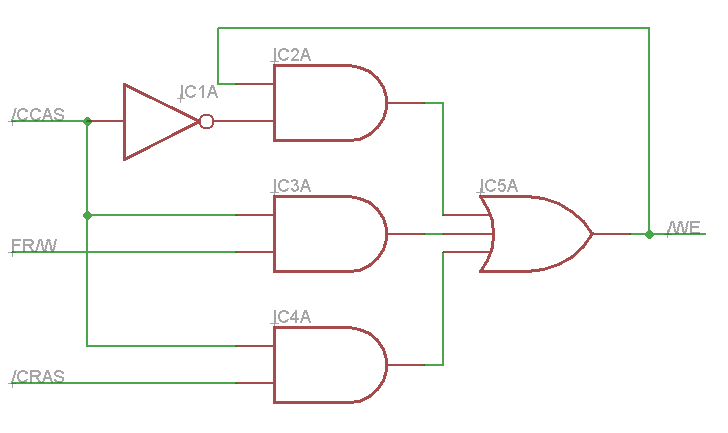

وبعد التبسيط - مثل هذا:

يتم نقل هذا الخيار إلى FPGA. للتجميع ، استخدم المؤلف WinCUPL. هذا البرنامج موجود على موقع اتميل. إنه الخام ويطير باستمرار ، لكنه تعامل مع المهمة تماما. مبرمج - عبقرية G540.

Jumper SJ1 على لوحة أعمال مثل هذا. إذا كان السنون 1 و 2 متصلين ، فإن إشارة / OE تمر عبر FPGA. إذا كان السنون 2 و 3 متصلاً ، فهو متصل بسلك شائع. لم يكن المؤلف متأكدًا من أن مخطط تحديد دورة التجديد سينجح. لذلك ، أضاف هذا الطائر في حالة إعادة تكوين FPGA.

نظرًا لأنه تبين أن كل شيء يعمل ، فأنت لست بحاجة إلى لحام المسامير ، فقط قم بتوصيل المحطتين 1 و 2 بنقطة لحام.

لتقليل حجم اللوحة ، قام المؤلف بتطبيق مكثف طاقة واحد لكل أربع شرائح RAM ، ووضع الشرائح نفسها على كلا الجانبين من اللوحة.

من الصعب لحام الرقائق في حالات SOJ ، وخاصة لحام ، باستخدام مكواة لحام. يوصي المؤلف باستخدام مجفف الشعر.

توسيع الرقائق بشكل صحيح. في الخلاصة هم مقلوبون. دبوس 1 ينظر إلى أسفل.

بعض من خلال الثقوب هي قريبة جدا من منصات. لا ماس كهربائى لهم مع جندى.

والمنصات 1 و 2 لالطائر ، على العكس من ذلك ، وثيقة.

تحتوي المكثفات C1 - C3 على سعة 0.1 μF ، C4 - 10 μF.

طلب المؤلف اللوحات في OSH Park. يتم تطبيق طلاء ENIG - الذهب ، ولكن رقيقة جدا. لخراطيش اللعبة ليست مناسبة - سيتم محوها بسرعة. وهنا تم وضع اللوحة في الفتحة مرة واحدة ولم تتم إزالة المزيد من هناك.

المؤلف يشكر

GGLabs على دارة لوحة مماثلة ، لقد ساعد كثيرا ، شكرا!

تحولت الدائرة النهائية من هذا القبيل:

ملفات:

FPGA البرامج الثابتة GAL22V10 ، تطبيق برنامج WinCUPL إصدار 5.30.4

المجلس ، تطبيق النسر الإصدار 7.1 البرمجيات

مخطط PDFحصل!