مقدمة صغيرة:

جاءت فكرة كتابة جوهرك الخاص بعد اجتياز ندوة مدرسية حول الدوائر الرقمية في مدينة تومسك . في هذا الحدث ، تم تقديم مقدمة إلى لغات وصف الأجهزة الحالية (Verilog HDL و VHDL) ، فضلاً عن مجموعة المعالجات schoolMIPS الصغيرة. لفهم بنية النوى ، تقرر اختراع دراجتهم الخاصة ، تتبع مسار تطوير schoolMIPS ، ولكن مع الأخذ بنظام قيادة آخر كأساس. نظرًا لتزايد شعبية RISC-V وانفتاح نظام القيادة الخاص بها (لم يكن MIPS يحتوي على نظام قيادة مفتوح وقت كتابة النواة) ، فقد تم اختيار مجموعة من تعليمات RISC-V ، وهي RV32I ، لتطوير kernel في المستقبل. يحتوي RV32I على مجموعة صغيرة من التعليمات الأساسية (37 باستثناء تلك الخاصة) ويمكن توسيعها إذا رغبت في ذلك ، على سبيل المثال ، عن طريق إضافة عدد صحيح من تعليمات الضرب والقسمة (RV32M) أو دعم للتعليمات المختصرة (RV32C). أيضًا ، تم تصميم هذا المشروع على أنه تعليمي ، لذلك تقرر زيادة وضوح النواة لإظهار عمله بفعالية.

قياسًا على schoolMIPS ، تم تنفيذ إصدارات kernel التالية:

- إصدار دورة واحدة (00_simple_risc_v_cpu).

- إصدار دورة واحدة مع دعم لتعليمات lw / sw (تحميل كلمة / كلمة مخزن) (01_simple_risc_v_cpu_lwsw).

- إصدار خطوط الأنابيب (ناقل ذو 5 مراحل) (02_pipe_risc_v_cpu).

حاليًا ، يتم وصف إصدار kernel التالي (03_pipe_risc_v_cpu_fc) بمجموعة كاملة من أوامر RV32I (دون مراعاة بعض الأوامر الخاصة).

في سياق وصف kernel ، تم التفكير في طرق لتحسين وضوح العمل وتصحيح الأخطاء والتحقق. تنفذ حاليا الطرق التالية:

إضافة وحدة VGA النص التصحيح (لفروع kernel أحادية الدورة). يتيح لك تضمين هذه الوحدة تتبع قيمة 32 تسجيلًا في وقت واحد على شاشة الشاشة ، وهو أمر غير ممكن عند استخدام إخراج المعلومات في مؤشرات السبعة قطاعات. في الأشكال الموضحة أدناه ، تحسب النواة أرقام ليوناردو وتعرض معلومات عن وحدة تصحيح الأخطاء المقابلة ؛

hex_display و DebugScreenCoreمخرجات المعلومات حول المؤشرات السبعة:

إخراج المعلومات على شاشة VGA:

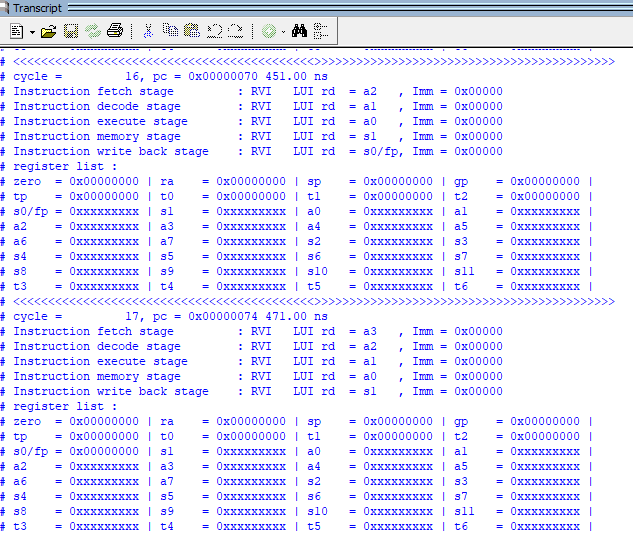

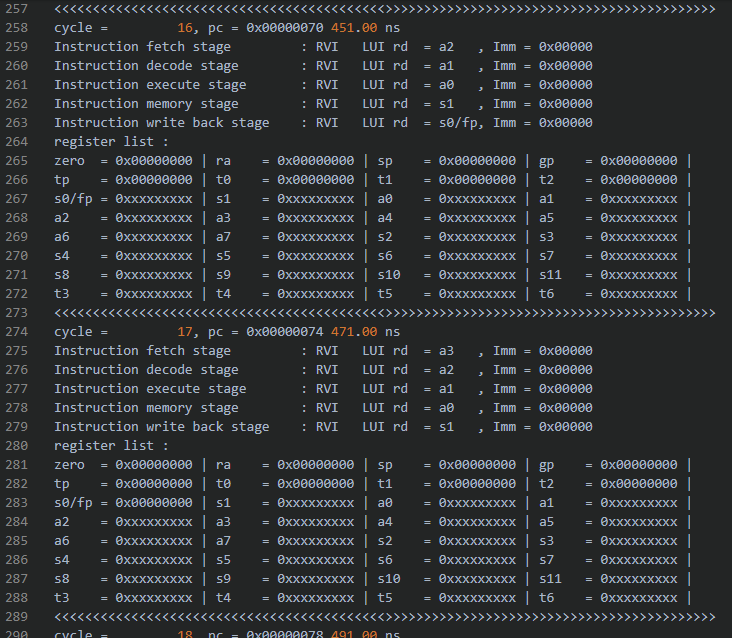

إضافة رسائل إلى محطة المحاكاة حول حالة ملف السجل والإرشادات المنفذة حاليًا. تتيح لك هذه الطريقة تحليل عملية النواة بشكل أفضل في المراحل الأولى من التطوير ، ولكنها ليست مريحة دائمًا ؛

محطةتهيئة ملف السجل:

تغيير قيمة sp:

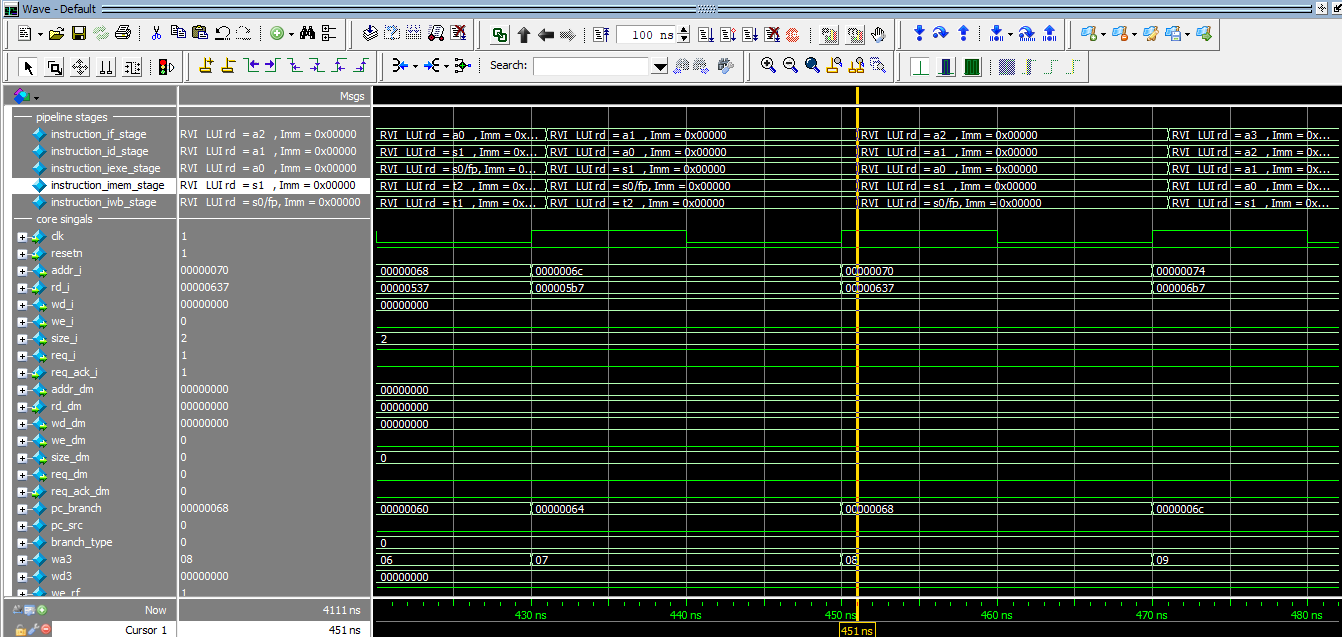

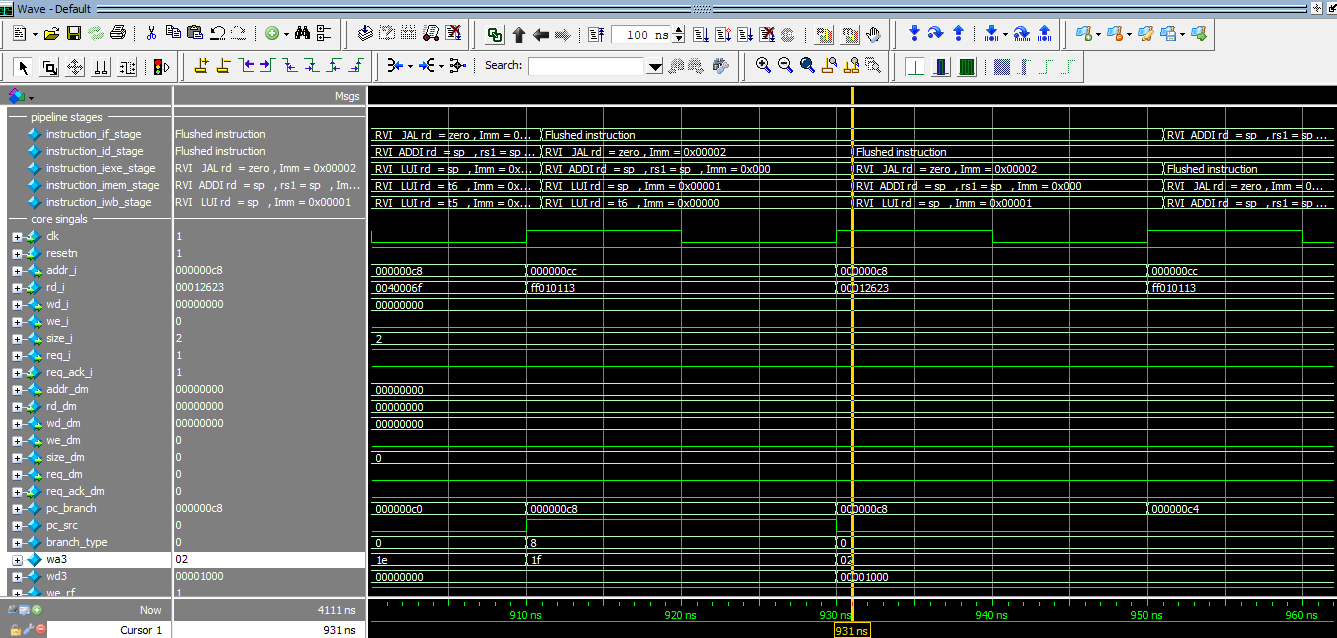

إضافة متغيرات السلسلة إلى الطول الموجي مع عرض الإرشادات القابلة للتنفيذ. باستخدام متغيرات السلسلة هذه ، يمكن للمطور تتبع الإعداد الصحيح لإشارات التحكم في جميع مراحل خط الأنابيب ؛

الموجيتهيئة ملف السجل:

تغيير قيمة sp:

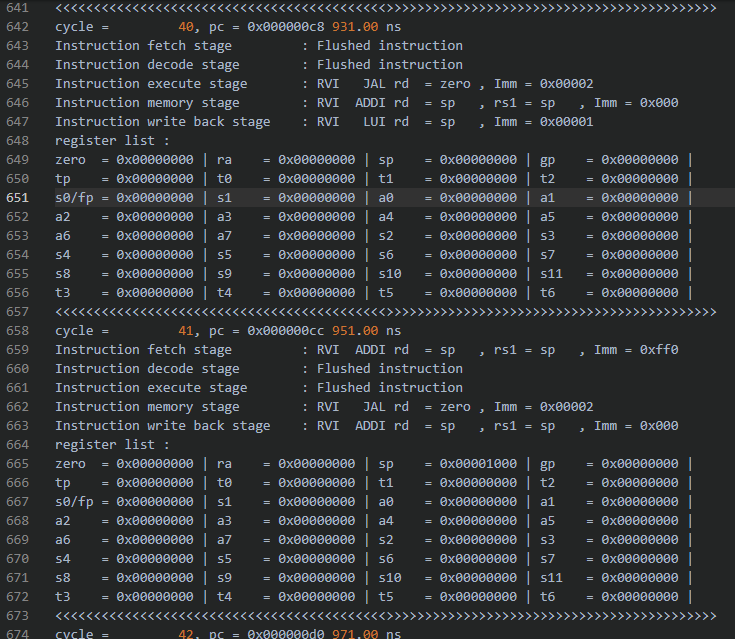

إضافة القدرة على كتابة معلومات تصحيح الأخطاء حول حالة النواة في ملف نصي. يتم تقديم حالة ملف السجل في شكل جدول ، ويشار أيضًا إلى التعليمات / التعليمات التي تنفذها النواة حاليًا. إنه تماثل نقطتين ، ولكنه يسمح بمعالجة أكثر بالمعلومات الواردة ؛

ملف نصيتهيئة ملف السجل:

تغيير قيمة sp:

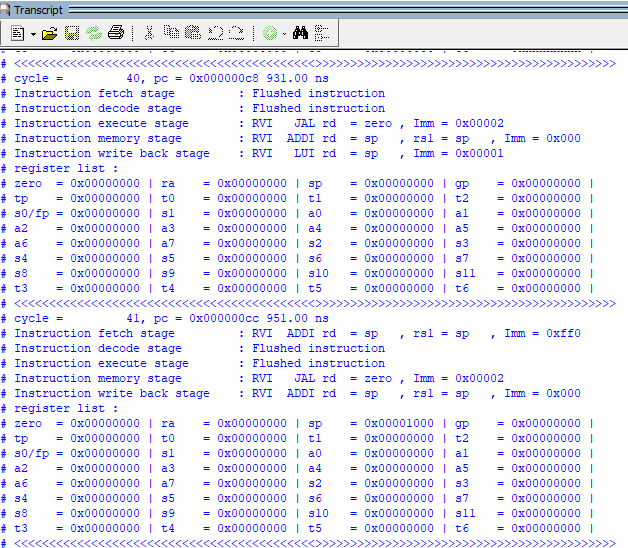

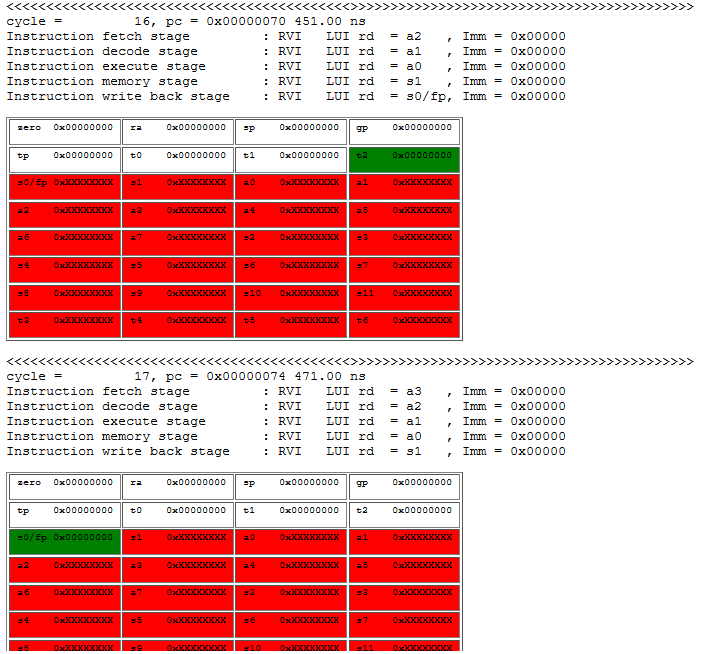

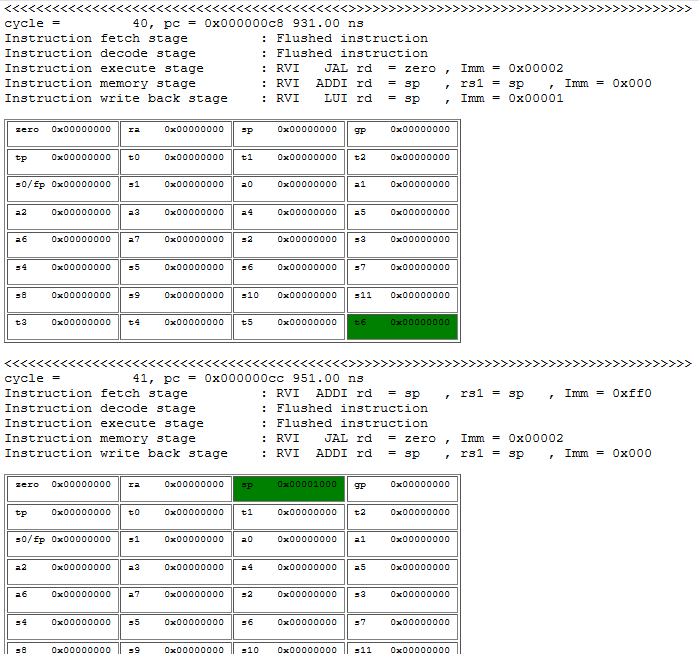

إضافة القدرة على كتابة معلومات تصحيح الأخطاء حول حالة النواة في ملف HTML. يتم تقديم حالة ملف السجل في شكل جدول مع ملاحظات حول تغيير قيم الخلايا ، بالإضافة إلى الإرشادات التي يتم تنفيذها حاليًا بواسطة kernel. إنه تماثل للفقرتين 2 و 4 ، لكن بالإضافة إلى ذلك ، يتيح لك الإشارة بسهولة إلى تغيير في البيانات. كما يتضح من الصور أدناه ، إذا لم يتم تحديد قيمة السجل ، فسيتم تمييز السجلات باللون الأحمر (السجلات s0 / fp - t6). في الدورة 17 ، تتغير قيمة السجل s0 / fp ويتم تمييز الخلية باللون الأخضر.

في الدورة 41 ، يتم تحميل القيمة 0x00010000 في سجل sp.

ملف HTMLتهيئة ملف السجل:

تغيير قيمة sp:

مقارنة بين فروع النواة:تعليمات kernel المدعومة حاليًا للفروع المختلفة:

الأجهزة الطرفية المدعومة:

اللغات المدعومة لبرامج الكتابة:

موارد FPGA المطلوبة للنواة (nf_cpu):

EP4CE22F17C6 (de0_nano):

10M50DAF484C7G (de10_lite):

تطوير المشروع.

ما هو المخطط القيام به في المستقبل:

- إضافة جميع تعليمات RV32I (في مرحلة الوصف) ؛

- تنفيذ تصحيح الأخطاء ؛

- إضافة وحدة تحكم DMA (DMA) ؛

- إضافة دعم للإطارات الأخرى AXI ، Avalon ، عظم الترقوة ؛

- إضافة ذاكرة التخزين المؤقت (ذاكرة التخزين المؤقت) ؛

- دمج الأجهزة الطرفية المختلفة (SPI ، TWI (I2C) ، Ethernet (10 base-t)) ؛

- إضافة تحكم المقاطعة ؛

- منفذ إصدارات مختلفة إلى لوحات التصحيح الأخرى ؛

- إضافة طرق أخرى لزيادة وضوح النواة ؛

- تشغيل RTOS ، على سبيل المثال zephyr .

كما يتم قبول التوصيات والاقتراحات لتطوير النواة.

رابط إلى المستودع: nanoFOX .