أرحب بالجميع.

في أعقاب آثار المقالات السابقة حول التحليلات المنطقية على حبري ، قررت إنهاء عملي "الأساسي".

سأبدأ قليلا من بعيد.

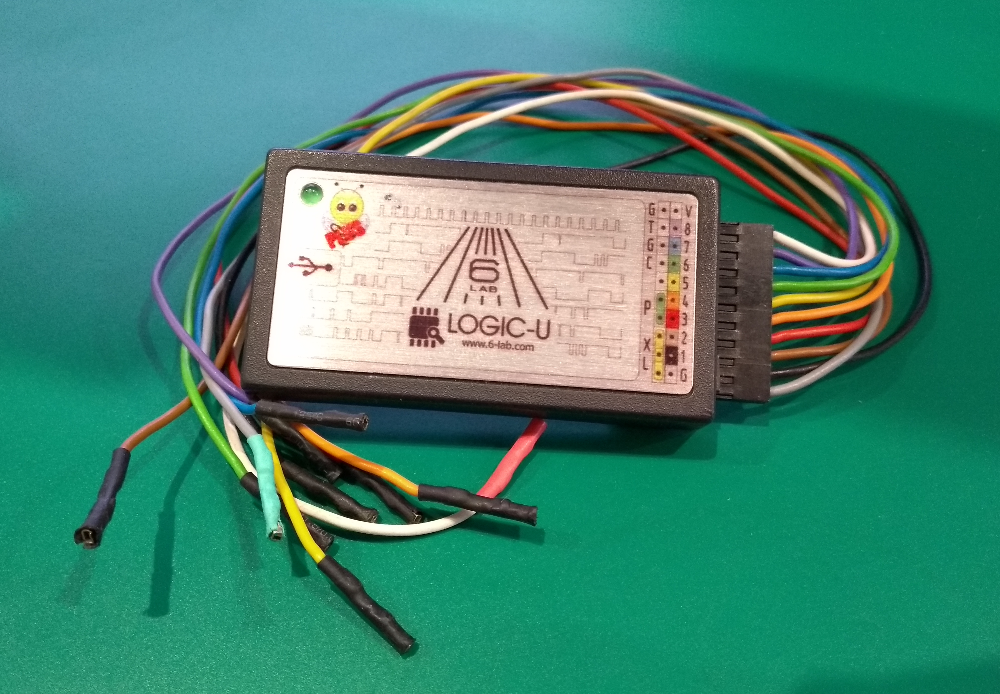

بدأ كل شيء في أوائل العشرات من القرن الماضي ، عندما اكتشفت لأول مرة عن Saleae Logic (المشار إليها فيما يلي باسم Saleae ، أعني محلل ذي 8 قنوات دون شريط تمرير) في أحد منتديات راديو الهواة.

أحاط علما. لكن بالفعل في الثالثة عشر من عمري أثناء تنفيذ مشروع آخر ، صادفت حقيقة أنني في حاجة فعلية إلى محلل منطقي مع مخزن مؤقت كبير. لم يحل مشكلة الذبذبات و hanteck la-5034 المتاحة في ذلك الوقت.

الميزة الرئيسية لـ Saleae واستنساخها هي عدم وجود مخزن مؤقت مدمج - يتم تعقب التيار بأكمله على الفور إلى جهاز الكمبيوتر وحفظه هناك. ثم يمكن تحليلها وفك تشفيرها وتصديرها. من ناحية ، نحن غير محدود عملياً من حيث عمق المشاهدة (يمكن تخزين البيانات لساعات) ، من ناحية أخرى ، الحد الأقصى لتردد أخذ العينات هو 24 ميجاهرتز. في معظم الحالات ، ومع ذلك ، بسبب الطبيعة البرنامجية لأخذ العينات ، يكون للعينات "ارتعاش" ملحوظ.

نتيجة لذلك ، بسرعة كبيرة ، في غضون يوم تقريبًا ، من خاركوف ، من المختبر 6 (المتوفى الآن) ، أرسلوا لي عبر استنساخ استنساخ sallee بهم مع اثنين من Eeeprom بنيت بالفعل للتبديل بين أنواع saleae و xbee (أجهزة هذه الأجهزة هي نفس vid الوحيد الذي يختلف: PID التي تومض في eeprom).

وفقًا لذلك ، يمكنك استخدام البرنامج من كلا المصنعين.

وذلك عندما أصبحت مهتمة بشيء مثل Y7C68013A ، حسناً ، أو أقصر من FX2 (على الرغم من أنه أكثر صحة من FX2LP).

هذا هو متحكم متوافق مع 8051 مع منفذ USB2.0 للأجهزة و 480 ميجابايت / ثانية صادقة.

تشمل الميزات: 16 كيلو بايت من ذاكرة الوصول العشوائي والقدرة على تنزيل البرامج الثابتة على حد سواء من I2C متصل EEPROM وعبر USB (لا يوجد فلاش مدمج هناك).

ويمكن لهذا MK أن يتظاهر بأنه أي جهاز على ناقل USB (بمعنى الاستجابة لأي VID: PID).

بعض التفاصيل من ورقة البيانات على إجراء التحميل

النظر في القضية عندما يتم توصيل I2C EEPROM إلى MK.

في هذه الحالة ، يتم تحليل البايتات الثمانية الأولى منه:

إذا كانت البايتة الأولى هي 0xC0 (كما هو الحال في البرامج الثابتة لاستنساخ Saleae) ، يقوم MK بتكوين منفذ USB باستخدام VID: PID المحدد في 1-4 بايت وينتظر تنزيل البرنامج الثابت عبر USB. اعتمادًا على VID تومض: PID MK يمكن أن يكون "جهازًا مختلفًا ، على الأقل صالحًا على الأقل Xbee على الأقل من قِبل شخص ما. مريح جدا يمكنك لحام EEPROMs في مكدس واختيار مع الطائر.

ولكن إذا كانت البايتة الأولى هي 0xC2 ، ثم تبدأ بـ 9 بايتات ، فيجب تخزين البرنامج الثابت الخاص بـ MK في EEPROM ، والذي سيتم تحميله في ذاكرة الوصول العشوائي (RAM) وبدء التنفيذ.

يشبه تنسيق التخزين HEX من Intel:

بمعنى ، يتم تقسيم البرنامج الثابت إلى كتل يتم تحميلها بشكل فردي في أقسام مختلفة من الذاكرة. وبناءً عليه ، لا معنى لتخزين المساحات الفارغة.

والآن نحن نقترب بسلاسة من الشخصية الرئيسية لمقالنا DreamSourseLab.

لن أروي القصة بأكملها (لا أعرفها حقًا ولا أرى أي معنى أعمق). هؤلاء ثلاثة مهندسين ، من خلال التمويل الجماعي ، شاهدوا مشروع محلل الأحلام المنطقي (تقريبًا).

ماذا فعلوا؟

وأضافوا إلى FX2 plisina رخيصة - المتقشف 6 (ربما تجسست على Saleae).

وهذا هو 16 قناة في وقت واحد ، وهذه هي نقاط أخذ العينات واضحة ، وهذه هي القدرة على حزم بت الفردية (يمكن أخذ عينات من سطرين 4 مرات أكثر من 8 ، والشيء الرئيسي هو الحفاظ داخل النطاق الترددي USB). هذه فرصة للحفظ في المخزن المؤقت بتردد عالٍ (400 ميغا هرتز / 4 قنوات ، 200 ميغا هرتز / 8 قنوات ، 100 ميغا هرتز / 16 قناة) ، ثم نقلها ببطء إلى جهاز كمبيوتر. وإذا كنت المسمار sigrok مع أقوى قاعدة لها من البروتوكولات فك الشفرة. بشكل عام ، أطلق المشروع - الجميع سعداء. ومع الأخذ في الاعتبار حقيقة أن المؤلفين حفظوا وضع الدفق (دون الحفظ في المخزن المؤقت الداخلي) ، حصلنا على محلل حلم منطقي (جيدًا ، لأنني كنت أرغب على الفور في 32 قناة و FX3).

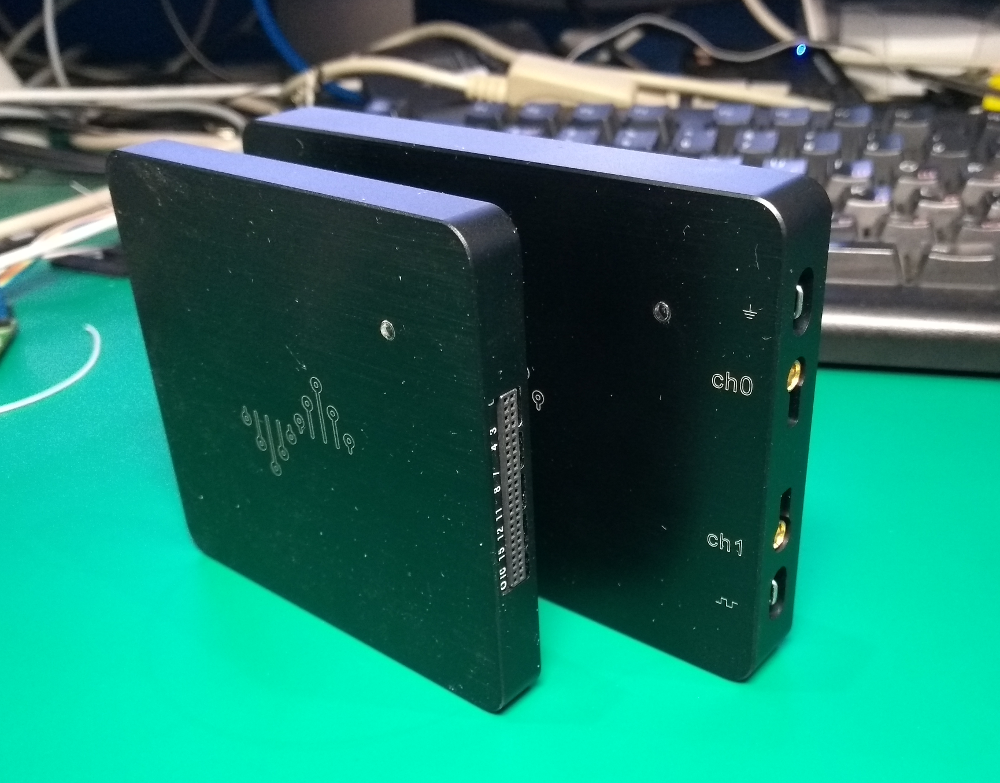

هكذا ظهرت DSLogicPro. مربع من الألومنيوم الأسود الصارم مع موصل USB-C.

ثم ضرب المهندسين الأعمال. وأصدروا مربعات تحمل اسم DSLogicBase و DSLogicPlus (كما أفهمها لغزو العالم من خلال المواقع الصينية) ، وكذلك DSCope (نقوم بتعليق ADC من 8 بتات والآن لدينا مرسمة الذبذبات ثنائية القناة).

حسنًا ، للحفاظ على هذه العملية تحت رقابة صارمة ، قمنا بتغيير تخطيط اللوحة قليلاً. أي أن DSLogicPlus و DSLogicPro متطابقان كهربائيًا ووظيفيًا ، لكن SRAM معلقة على القابس على المسامير الأخرى (يظهر هذا بوضوح في صورة المقطوعات). أظن أنه قد تم إجراء تحسينات في أماكن أخرى.

بالمناسبة ، تم إجراء مراجعة قيمة للغاية من حيث الكبل لتوصيل الإشارات التي تمت دراستها. في حالة توصيل 16 خطًا في Pro بموصل عريض واحد ، ثم في Plus ، تم تقسيم جميع الكابلات إلى مجموعات من 4 قنوات يمكن توصيلها بشكل منفصل. حسنًا ، الكبلات نفسها قصيرة ومحورية وفي مكان القطع (حيث يتم تقسيم المحورية إلى إشارة منفصلة وأسلاك شائعة) يوجد وشاح صغير به مرشح.

وهكذا ، في ربيع عام 17 ، أمرت DSLogicBase في الصين (لسوء الحظ ، لم أكن أعرف كل ما كتبته في ذلك الوقت). لقد أرسلوا لي كل شيء ، لكنني أتطلع إلى المخزن المؤقت الذي يبلغ حجمه 64 ميغابايت ، لقد قمت بفك ضغط اللوحة ورأيت مكانًا فارغًا. رفع بسرعة بوتشو عاد 50 ٪ من التكلفة. ثم بدأ في دراسة مسألة تحويل قاعدةي إلى Plus. هذا هو بالضبط الفرق بين Base و Plus - وجود مخزن مؤقت منفصل. يستخدم Base الذاكرة المضمنة في FPGA.

في صيف 17 ، في طريقي إلى العمل والعودة لمدة نصف ساعة في قطار مركز عملائي ، درست هذه المشكلة. وبسرعة كبيرة أصبح من الواضح أن الاختلافات كانت فقط في SRAM مختوم وزوج من بايت من البرامج الثابتة EEPROM.

قليلا عن ما يكمن في الدليل DSView / الدقة

هناك لدينا مجموعة من الملفات ذات الامتدادات بن و مهاجم.

بن - هذه هي البرامج الثابتة ل plisina. يتم تحميلها في وقت بدء البرنامج عبر fx2.

مهاجم هي ملفات البرامج الثابتة الثنائية ل FX2.

إذا قارنت جميع ملفات fw منه ، فإنها تختلف جميعها فقط في بايت PID على العنوان القريب من النهاية.

وهذا هو ، الاختلافات بين جميع الأجهزة هي هذا فقط والبرامج الثابتة للمكونات (التي ، كما قلت ، يتم تحميلها في وقت التهيئة).

المقارنة بين مهاجم مع ما هو مكتوب في EEPROM (بالطبع ، أنا على الفور التخلص من تفريغ من محلل بلدي) أظهرت أن البرامج الثابتة المنشورة هنا.

إذا قمت بنشر البرنامج الثابت من EEPROM ، فعندئذٍ (بقدر ما أتذكر) فإنها ستطابق (لإصدار البرنامج 0.96).

وبالتالي ، كما هو مكتوب بالفعل على لوحة الوصل ، تحتاج فقط إلى لحام الذاكرة وتغيير وحدتي بايت في البرنامج الثابت (في الرأس ثم في البرنامج الثابت).

بطريقة مماثلة ، يتم الانتهاء من DSCope ، نقوم بمضاعفة الذاكرة وتغيير PID في EEPROM.

هناك واحد أكثر فارق بسيط.

عند إصدار إصدارات برامج جديدة (0.96-0.99) ، تمت إضافة طرازات الأجهزة المدعومة وتغيير PID الخاص بهذه الطرز.

لذلك حصلت على مثل هذا الجهاز اللوحي:

بالإضافة إلى ذلك ، ظهرت بعض الإشارات في البرنامج الثابت على العنوان 0x20 لإصدار Pro هناك 5 ، بالنسبة لـ Base و Plus هناك 6. على الأرجح هذا هو مجرد إصدار من لوحة الدوائر المطبوعة.

بالمناسبة ، هناك طريقة أخرى للتنقيح. لا يلزم إعادة برمجة EEPROM. يكفي لحام SRAM ، ثم ، عند تجميع libsigrok4DSL ، قم بإجراء تصحيح على الملف libsigrok4DSL / hardware / DSL / dsl.h:

في الهيكل الذي يصف البنية الثابتة للمعدات DSL_profile support_DSLogic [] ،

في المكان الذي يتم فيه وصف DSLogic PLus و Base ، قم بتغيير حقول PID بحيث يعتقد البرنامج أن لديه Base PID 20 و Plus PID 21.

319 {0x2A0E, 0x0020, "DreamSourceLab", "DSLogic PLus", NULL, 320 "DSLogicPlus.fw", 321 "DSLogicPlus.bin", 322 "DSLogicPlus.bin", 323 {CAPS_MODE_LOGIC, 324 CAPS_FEATURE_VTH | CAPS_FEATURE_BUF, 325 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 326 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 327 SR_MB(256), 328 0, 329 DSL_BUFFER100x16, 330 0, 331 0, 332 DSL_STREAM20x16, 333 SR_MHZ(1), 334 SR_Mn(1), 335 0, 336 0} 337 }, 338 339 {0x2A0E, 0x0021, "DreamSourceLab", "DSLogic Basic", NULL, 340 "DSLogicBasic.fw", 341 "DSLogicBasic.bin", 342 "DSLogicBasic.bin", 343 {CAPS_MODE_LOGIC, 344 CAPS_FEATURE_VTH, 345 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 346 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 347 SR_KB(256), 348 0, 349 DSL_STREAM20x16, 350 0, 351 0, 352 DSL_STREAM20x16, 353 SR_MHZ(1), 354 SR_Mn(1), 355 0, 356 0} 357 },

وستعمل نسخة محللك مع هذا الإصدار من DSView كما لو كان لديك Plus حقيقي.

في غضون ذلك ، سأحلم بمجموعة من Spartan6 + FX3 + DSView.