بطريقة ما لا أستطيع التعبير عن أفكاري لفترة وجيزة. في الخريف الماضي ، كانت هناك رغبة في معرفة المزيد من التفاصيل حول هندسة PSoC التي أتقنتها ، والتي أسفرت عن سلسلة من المقالات حول هذا الموضوع. أشارك الآن في إعداد الأجهزة لمجمع Redd لتصحيح الأخطاء عن بُعد الخاص بنا ، والذي تم وصفه

هنا ، وأريد التخلص من التجربة المتراكمة في شكل نصي. لست متأكداً بعد ، لكن يبدو لي أنها ليست مجرد مقالة واحدة ، بل هي حلقة. أولاً ، هذه هي الطريقة التي سأوثق بها طرق التطوير المتقدمة التي قد تكون مفيدة لشخص ما عند العمل مع المجمع ، وبشكل عام ، وثانيًا ، ما زال المفهوم جديدًا ، وليس مستقرًا تمامًا. ربما ، أثناء مناقشة المقالات ، ستظهر بعض التعليقات ، والتي يمكن للمرء أن يستخلص منها شيئًا لتوسيعه (أو حتى تغييره). لذلك ، نحن المضي قدما.

مقدمة طويلة

لا أحب النظرية حقًا ، مفضلاً وضع بعض الأشياء العملية في وقت واحد. ولكن في بداية المقال الأول ، دون مقدمة طويلة في أي مكان. في ذلك ، أبرر النهج الحالي للتنمية. وكل شيء يدور حول شيء واحد: ساعة الإنسان مورد غالي الثمن. والأمر ليس فقط في الشروط المخصصة للمشروع. انه مكلف بدنيا. إذا تم إنفاقه على تطوير المنتج النهائي ، حسنًا ، ما الذي يمكنك القيام به دون أي مكان. ولكن عندما يتم إنفاقها على العمل الإضافي ، فهذا في رأيي أمر سيء. أتذكر أنه كان لدي نزاع مع أحد المطورين الذي قال إنه بعد أن صنع نماذج أولية من تلقاء نفسه ، فإنه سيوفر المال لشركته الأصلية. لقد تقدمت بحجة أنه سيقضي حوالي 3 أيام على التصنيع. هذا هو 24 ساعة رجل. نأخذ راتبه عن هذه الساعات ، ونضيف الضريبة الاجتماعية التي "يدفعها صاحب العمل" ، وكذلك استئجار المكتب لهذه الساعات. وقد فوجئنا برؤية لوحات الطلب على الجانب ، حيث يمكنك الحصول على تكاليف أقل. ولكن هذا أنا ، أنا أبالغ. بشكل عام ، إذا كان بالإمكان تجنب تكاليف العمالة ، فيجب تجنبها.

ما هو تطوير "البرامج الثابتة" لمجمع Redd؟ هذه وظيفة مساعدة. سيعيش المشروع الرئيسي في سعادة دائمة ؛ يجب القيام به بأكبر قدر ممكن من الكفاءة ، مع تحسين ممتاز ، إلخ. لكن إنفاق الوقت والطاقة على الأشياء المساعدة التي ستذهب إلى الأرشيف بعد التطوير يضيع. لقد تم تطوير معدات Redd من خلال هذا المبدأ. يتم تنفيذ جميع الوظائف ، إن أمكن ، كأشياء قياسية. يتم تطبيق حافلات SPI و I2C و UART على الدوائر الصغيرة القياسية FTDI ويتم برمجتها من خلال برامج تشغيل قياسية ، دون أي زخرفة. يتم تطبيق إدارة بكرات في تنسيق منفذ COM الظاهري. يمكن تعديلها ، ولكن على الأقل تم القيام بكل شيء حتى لا تنشأ مثل هذه الرغبة. بشكل عام ، يتم تطبيق كل شيء قياسي ، إن أمكن ، بطريقة قياسية. من مشروع إلى آخر ، يحتاج المطورون ببساطة إلى كتابة التعليمات البرمجية النموذجية بسرعة للكمبيوتر للوصول إلى هذه الحافلات. يجب أن تكون تقنية التطوير في C ++ واضحة لأولئك الذين يطورون برامج لأجهزة التحكم الدقيق (سنتحدث عن بعض التفاصيل الفنية في مقال آخر).

لكن FPGA تقف وحدها في المجمع. تتم إضافته إلى النظام للحالات عندما يكون من الضروري تنفيذ أي بروتوكولات غير قياسية مع متطلبات الأداء العالي. إذا كانت هذه مطلوبة ، فسيتعين عليك القيام بـ "البرامج الثابتة" لذلك. يتعلق الأمر ببرمجة FPGA وأريد أن أتحدث على وجه التحديد ، كل هذا فقط لنفس الغرض - لتقليل وقت تطوير الأشياء المساعدة.

حتى لا تخلط بين القارئ ، سأقوم بصياغة الفكرة في إطار:

ليس من الضروري إجراء تطوير لـ FPGAs في كل مشروع. إذا كانت هناك وحدات تحكم حافلة كافية متصلة مباشرة بالمعالج المركزي للعمل مع الجهاز الهدف ، يجب عليك استخدامها.

FPGA يضاف إلى المجمع لتنفيذ البروتوكولات غير القياسية.

مخطط كتلة من المجمع

دعونا نلقي نظرة على مخطط كتلة المجمع

في الجزء السفلي من الدائرة هو "آلة حاسبة". في الواقع ، هذا هو جهاز كمبيوتر قياسي مع لينكس. يمكن للمطورين كتابة برامج منتظمة في C ، C ++ ، Python ، إلخ ، والتي سيتم تنفيذها بواسطة الكمبيوتر. في الجزء العلوي الأيمن توجد المنافذ القياسية للإطارات القياسية. على اليسار يوجد مفتاح للأجهزة القياسية (SPI Flash ، بطاقة SD والعديد من مرحلات الحالة الصلبة المنخفضة الحالية ، والتي يمكن ، على سبيل المثال ، محاكاة مكابس الأزرار). وفي الوسط هو هذا الجزء بالتحديد ، العمل المزمع النظر فيه في هذه السلسلة من المقالات. قلبه عبارة عن FPGA من فئة FPGA ، حيث يمكن استخدام الخطوط المستقيمة (كأزواج تفاضلية أو خطوط عادية غير مقننة) ، وخطوط GPIO بمستوى منطق قابل للتكوين ، بالإضافة إلى ناقل USB 2.0 يتم تنفيذه من خلال رقاقة ULPI.

استمرار مقدمة حول نهج البرمجة FPGA

عند تطوير منطق تحكم عالي الأداء لـ FPGAs ، غالبًا ما يتم لعب لعبة صاحب الجلالة على الكمان الأول بواسطة جهاز حكومي. على الأجهزة ، يمكن تنفيذ منطق عالي السرعة ، لكنه معقد. ولكن من ناحية أخرى ، يتم تطوير الإكمال التلقائي بشكل أبطأ من برنامج للمعالج ، وتعديله هو عملية أخرى. هناك أنظمة تبسط تطوير وصيانة الآلات. تم تطوير واحدة منها بواسطة شركتنا ، ولكن لا تزال عملية التصميم لأي نوع من المنطق المعقد غير سريعة. عندما يكون النظام المطوّر هو المنتج النهائي ، فمن المنطقي إعداد وتصميم جهاز تحكم جيد وقضاء بعض الوقت في تنفيذه. ولكن كما لوحظ بالفعل ، فإن تطوير Redd هو وظيفة مساعدة. إنه مصمم لتسهيل العملية وليس تعقيدها. لذلك ، فقد تقرر أن التطوير لن يكون آليا ، ولكن أنظمة المعالج.

ولكن من ناحية أخرى ، عند تطوير الأجهزة ، تم رفض الخيار الأكثر عصرية حتى الآن ، FPGA مع ARM الأساسية. أولا ، لأسباب السعر. تعتبر اللوحة النموذجية المستندة إلى Cyclone V SoC مرتفعة التكلفة إلى حد ما ، ولكن الغريب في الأمر ، أن FPGA المنفصلة أغلى بكثير. على الأرجح ، يتم تفريغ سعر لوحات النماذج الأولية من أجل جذب المطورين لاستخدام بيانات FPGA ، ويتم بيع اللوحات بشكل فردي. سوف سلسلة لاتخاذ رقائق الفردية. لكن بالإضافة إلى ذلك ، هناك أيضًا "ثانية". ثانياً ، عندما كنت أجرب تجربة Cyclone V SoC ، اتضح أن نظام المعالج هذا ليس كذلك وهو منتج عندما يتعلق الأمر بوصول منفرد إلى المنافذ. دفعة - نعم ، هناك عمل سريع. وفي حالة الوصول الفردي بتردد مدار الساعة من جوهر المعالج البالغ MHz 925 ، يمكنك الوصول إلى المنافذ بتردد بضع ميغاهرتز. للجميع ، أقترح استدعاء الوظيفة القياسية لإدخال البيانات في FIFO من كتلة UART ، والتي تتحقق من تجاوز قائمة الانتظار ، ولكن الاتصال بها عندما تكون قائمة الانتظار فارغة بشكل واضح ، أي لا يتداخل مع العمليات. انتقلت إنتاجي من مليون إلى خمسمائة ألف مكالمة في الثانية (بالطبع ، بالعمل مع الذاكرة بالسرعة العادية ، تم ضبط جميع ذاكرات التخزين المؤقت ، حتى أن خيار الوظيفة الذي لم يتحقق من FIFO يعمل بشكل أسرع ، تمامًا أن الوظيفة قيد المناقشة قد اختلطت كثيرًا الكتابة والقراءة من الموانئ). هذا هو FIFO! في الواقع ، اخترع FIFO من أجل إسقاط البيانات هناك وننسى! إنهاء سريع! وليس مع الأداء ، أقل من عملية ضخمة واحدة في الثانية بتردد معالج قدره 925 ميجاهرتز ...

الكمون هو السبب. بين جوهر المعالج والجهاز يقع من ثلاثة جسور أو أكثر. علاوة على ذلك ، تعتمد سرعة الوصول إلى المنافذ على السياق (ستنطلق عدة سجلات متتالية بسرعة ، ولكن القراءة الأولى ستوقف العملية حتى يتم إلغاء تحميل البيانات المخزنة مؤقتًا بالكامل ، وسيتباطأ أيضًا الكثير من السجلات في صف واحد ، نظرًا لاستنفاد المخازن المؤقتة للكتابة). أخيرًا ، أظهر فحص الآثار المتراكمة في مخزن تصحيح الأخطاء أن بنية

Cortex A يمكنها تنفيذ نفس الجزء لعدد مختلف من دورات الساعة بسبب نظام ذاكرة التخزين المؤقت المعقدة. باختصار ، عند النظر إلى كل هذه العوامل (السعر ، تخفيضات الأداء عند العمل مع المعدات ، عدم استقرار سرعة الوصول إلى الجهاز ، الاعتماد العام على السياق) ، فقد تقرر عدم وضع مثل هذه الشريحة في المجمع.

أظهرت التجارب التي أجرتها شركة Cypress's PSoC أن هناك نواة

Cortex M تعطي نتائج أكثر قابلية للتنبؤ وقابلة للتكرار ، لكن السعة المنطقية وتكرار التشغيل الأقصى لوحدات التحكم هذه لم تتوافق مع المواصفات الفنية ، وبالتالي تم إهمالها.

تقرر تثبيت Cyclone IV FPGA نموذجي غير مكلف والتوصية باستخدام نواة معالج NIOS II مركبة. حسنًا ، وإذا لزم الأمر - لإجراء التطوير باستخدام أي طرق أخرى (الآلات الأوتوماتيكية ، والمنطق الصعب ، إلخ).

سأذكر بشكل منفصل (وأبرز هذه الفقرة) أن المعالج الرئيسي للمجمع هو x86 (x64). هو الذي هو المعالج المركزي للنظام. على ذلك يتم تنفيذ المنطق الرئيسي للمجمع. تم تصميم نظام المعالج ، الذي سيتم مناقشته أدناه ، لتوفير ببساطة منطق تشغيل الجهاز "تومض" في FPGA. علاوة على ذلك ، لا يتم بيع هذا الجهاز إلا إذا لم يكن لدى المطورين وحدات كافية بدوام كامل متصلة مباشرة بالمعالج المركزي.

عملية تطوير وتصحيح "البرامج الثابتة"

إذا كان مجمع Redd يعمل بنظام Linux ، فإن هذا لا يعني أنه يجب تنفيذ التطوير في نظام التشغيل هذا. Redd هو المنفذ عن بعد ، ويجب تنفيذ التطوير على جهاز الكمبيوتر الخاص بك ، أيا كان نظام التشغيل. كل من لديه Linux هو الأسهل ، لكن من اعتاد على Windows (اعتدت أن يكره WIN 3.1 كثيرًا ، لكنني كنت مجبرًا على العمل ، لكن في مكان ما بحلول WIN95 OSR2 اعتاد عليها ، والآن من غير المجدي مكافحته ، أصبح من السهل قبوله) ، تلك يمكن أن تستمر في قيادة التنمية في ذلك.

نظرًا لأن صداقتي مع Linux لم تنجح ، فلن أقدم تعليمات خطوة بخطوة لإعداد البيئة التي تحتها ، لكنني سأقتصر على الكلمات العامة. سيكون من يعمل مع نظام التشغيل هذا كافيًا لذلك ، وبالنسبة للباقي ... صدقني ، من الأسهل الاتصال بمسؤولي النظام. في النهاية ، لقد فعلت ذلك. لكن مع ذلك.

يجب عليك تنزيل وتثبيت Quartus Prime Programmer and Tools من نفس الإصدار مثل بيئة التطوير الخاصة بك. إذا لم تتطابق الإصدارات ، فقد تكون هناك مفاجآت. قضيت المساء كله لفهم هذه الحقيقة. لذلك ، فقط قم بتنزيل الأداة من نفس الإصدار مثل بيئة التطوير.

بعد التثبيت ، أدخل الدليل حيث تم تثبيت البرنامج ، دليل فرعي bin. بشكل عام ، يجب أن يكون الملف الأكثر أهمية هو jtagconfig. إذا قمت بتشغيله دون وسيطات (بالمناسبة ، طلبت بإصرار الدخول. / jtagconfig وفقط بذلك) ، ثم سيتم عرض قائمة من المبرمجين المتاحين في النظام و FPGAs المتصلة بهم. يجب أن يكون هناك مكبر USB. والمشكلة الأولى التي يطرحها النظام ليست هي حقوق الوصول الكافية للعمل مع USB. كيفية حلها دون اللجوء إلى sudo موصوفة هنا:

radiotech.kz/threads/nastrojka-altera-usb-blaster-v-ubuntu-16-04.1244ولكن هنا قائمة من الأجهزة المعروضة. الآن يجب أن تكتب:

./jtagconfig --enableremote <password>

بعد ذلك يتم تشغيل الخادم ، يمكن الوصول إليها من أي مكان من الشبكة.

سيكون كل شيء على ما يرام ، لكن جدار الحماية الخاص بالنظام لن يسمح لأي شخص بمشاهدة هذا الخادم. أظهر فحص على Google أنه بالنسبة لكل نوع من أنواع Linux (يوجد العديد منها) ، فإن المنافذ الموجودة في جدار الحماية تفتح بطريقتها الخاصة ، ويجب الإدلاء بالكثير من التعاويذ التي يفضل الاتصال بالمدراء.

تجدر الإشارة أيضًا إلى أنه إذا لم يتم تسجيل jtagd في التشغيل التلقائي ، فعندما تفتح الوصول عن بُعد ، سيتم إخبارك أنه من المستحيل تعيين كلمة مرور. لمنع حدوث ذلك ، يجب أن تبدأ jtagd ليس عن طريق jtagconfig نفسه ، ولكن قبل ذلك.

بشكل عام ، الشامانية على الشامانية. اسمحوا لي فقط إصلاح الأطروحة:

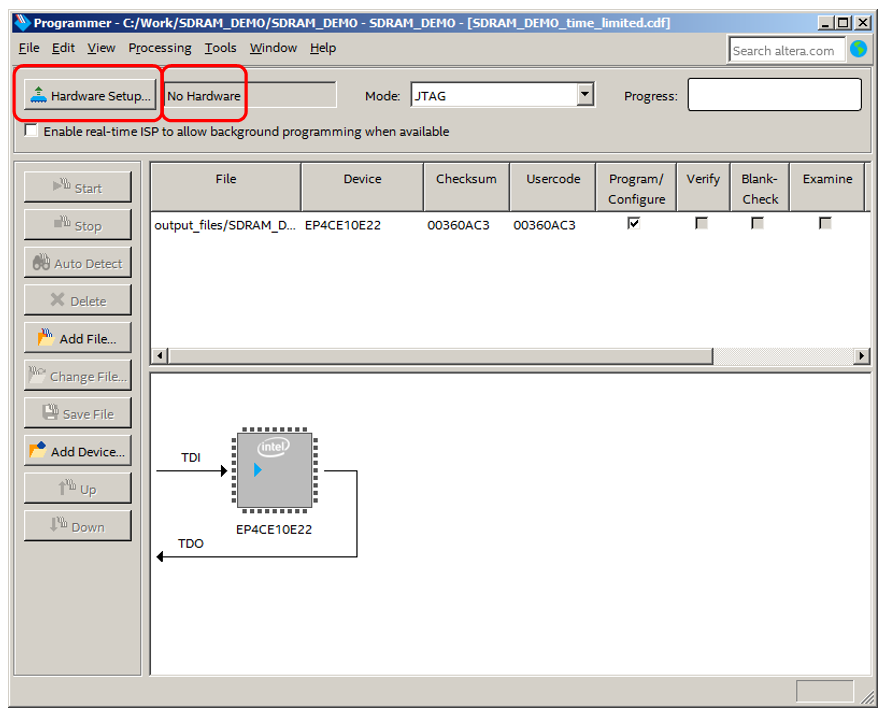

بالطبع ، هناك مسار مشابه يمر عبر واجهة المستخدم الرسومية ، لكن من المنطقي أن نفعل كل شيء دفعة واحدة. لذلك ، وصفت نسخة دفعة. عندما يتم الانتهاء من كل هذه الرسائل (وقد أكملها مسؤولو النظام) ، فإننا نطلق المبرمج على أجهزتنا ، ونرى رسالة حول نقص المعدات. انقر فوق إعداد الأجهزة:

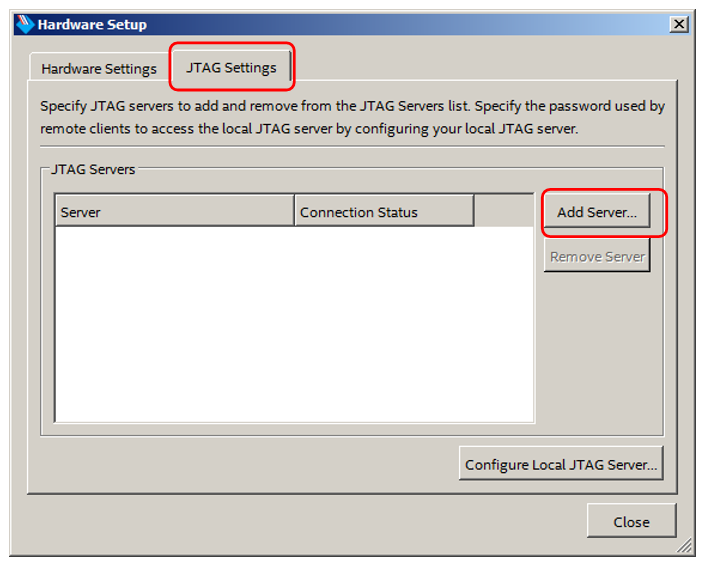

انتقل إلى علامة التبويب إعدادات JTAG وانقر فوق إضافة خادم:

ندخل عنوان شبكة Redd (بالنسبة لي هو 192.168.1.100) وكلمة المرور:

نتأكد من أن الاتصال كان ناجحا.

قضيت ثلاثة أيام عطلة لتحقيق ذلك ، ثم قرر المسؤولون كل شيء.

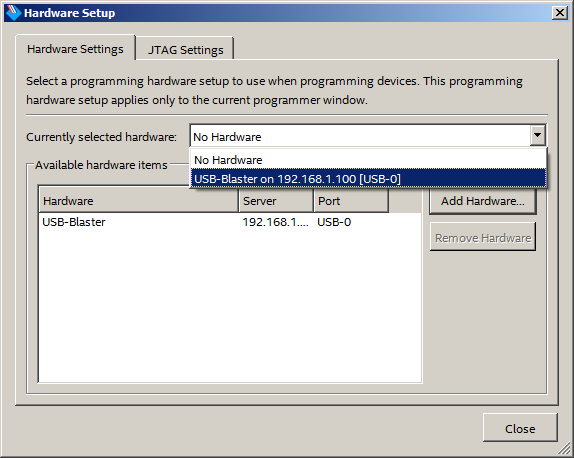

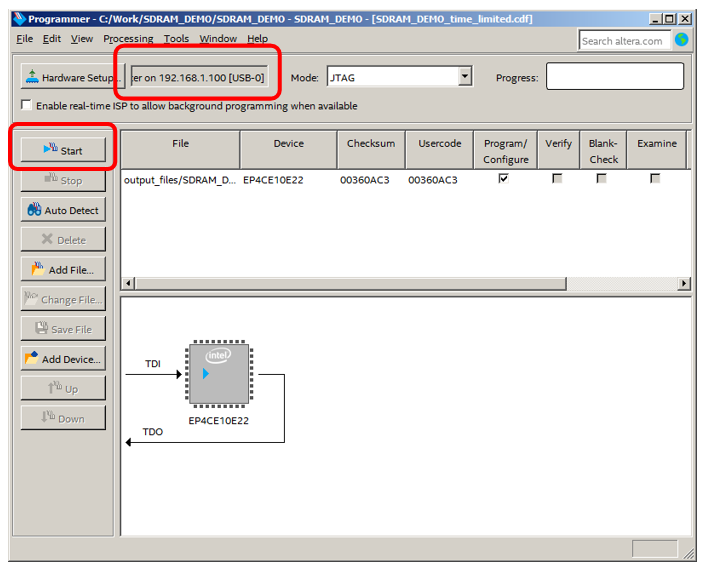

قم بالتبديل إلى علامة التبويب "إعدادات الأجهزة" ، وافتح القائمة المنسدلة وحدد المبرمج البعيد هناك:

كل شيء ، الآن يمكن استخدامه. زر ابدأ مفتوح.

أول "البرامج الثابتة"

حسنا اذن للحصول على قيمة عملية حقيقية لهذه المقالة ، دعنا نحلل أبسط "البرامج الثابتة" المصنوعة باستخدام الطرق المذكورة أعلاه. إن أبسط شيء تمكنت فعلاً من تنفيذه للمجمع هو اختبار لرقاقة SDRAM. هنا في هذا المثال والممارسة.

هناك عدد من النوى الهاوية لدعم SDRAM ، لكنهم جميعًا يشغلونها بطريقة صعبة. والمحاسبة لجميع الحيل هو العمل. سنحاول استخدام الحلول الجاهزة التي يمكن إدراجها في نظام الحوسبة NIOS II ، لذلك سوف نستخدم SDRAM Controller Core القياسي. تم وصف الجزء الأساسي نفسه في

دليل مستخدم IP Embedded Peripherals IP ، ويتم تخصيص مساحة كبيرة في الوصف لإزاحة الساعة بالنسبة إلى SDRAM بالنسبة للساعة الأساسية. يتم إعطاء الحسابات النظرية المعقدة والصيغ ، ولكن ما يجب فعله لا يتم الإبلاغ عنه بشكل خاص. يمكن العثور على ما يجب فعله في المستند

باستخدام SDRAM على لوحة DE0 من Altera مع Verilog Designs . في سياق التحليل ، سأطبق المعرفة من هذا المستند.

سوف أطور في الإصدار المجاني من Quartus Prime 17.0. إنني أركز على هذا ، لأنه أثناء التجميع ، يقولون لي أنه في المستقبل ، سيتم طرد جوهر

وحدة التحكم SDRAM من الإصدار المجاني. إذا كان هذا قد حدث بالفعل في بيئة التطوير الخاصة بك ، فلا أحد يكترث بتنزيل الإصدار السابع عشر المجاني وتثبيته على جهاز افتراضي. يتم العمل الرئيسي أينما كنت ، والبرامج الثابتة لـ Redd مع SDRAM في الإصدار السابع عشر. حسنًا ، هذا إذا كنت تستخدم الخيارات المجانية. لا أحد هدد بطرده من أموال مدفوعة بعد. ولكن كنت مشتتا. إنشاء مشروع جديد:

دعنا نسميها SDRAM_DEMO. يجب تذكر الاسم: سأقوم بتنفيذ عملية تطوير فائقة السرعة ، لذلك يجب أن يكون نظام المعالج نفسه في المستوى الأعلى ، دون أي طبقات Verilog. ولكي يحدث هذا ، يجب أن يتطابق اسم نظام المعالج مع اسم المشروع. لذلك تذكرها.

نتفق مع القيم الافتراضية في بضع خطوات ، نأتي إلى اختيار الكريستال. نختار EP4CE10E22C7 المستخدمة في المجمع.

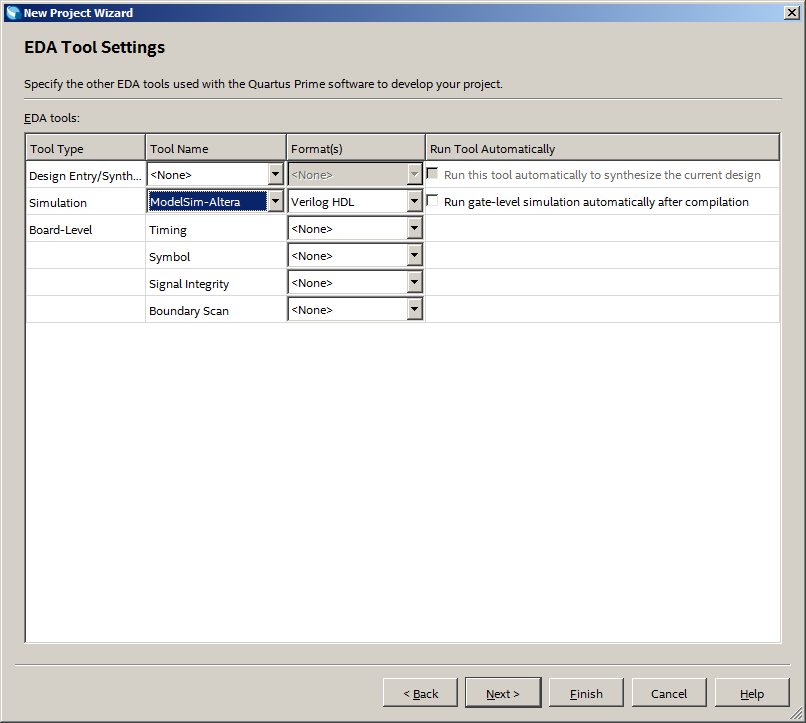

في الخطوة التالية ، انطلاقًا من العادة ، اخترت تصميم النماذج في ModelSim-Altera. اليوم لن نقوم بتصميم أي شيء ، ولكن كل شيء يمكن أن يكون مفيدًا. من الأفضل تطوير هذه العادة ومتابعتها:

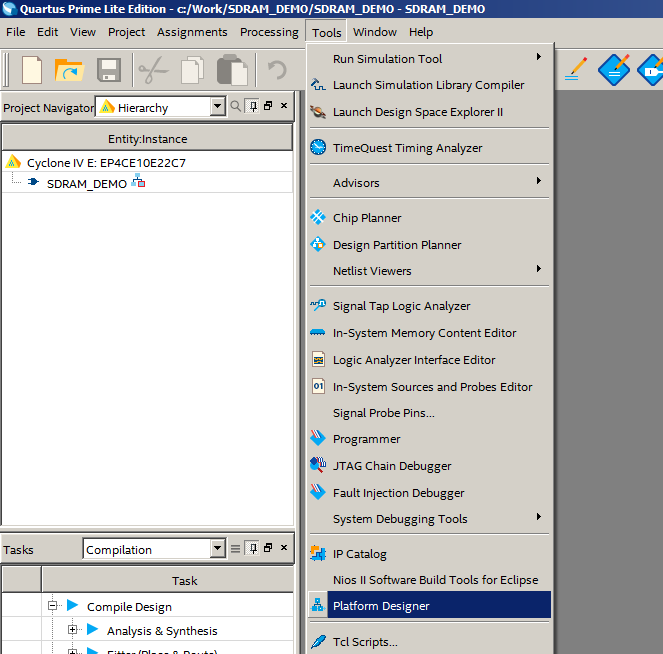

تم إنشاء المشروع. انتقل فورًا إلى إنشاء نظام المعالج (Tools-> Platform Designer):

لقد أنشأنا نظامًا يحتوي على ساعة وإعادة ضبط الوحدة النمطية:

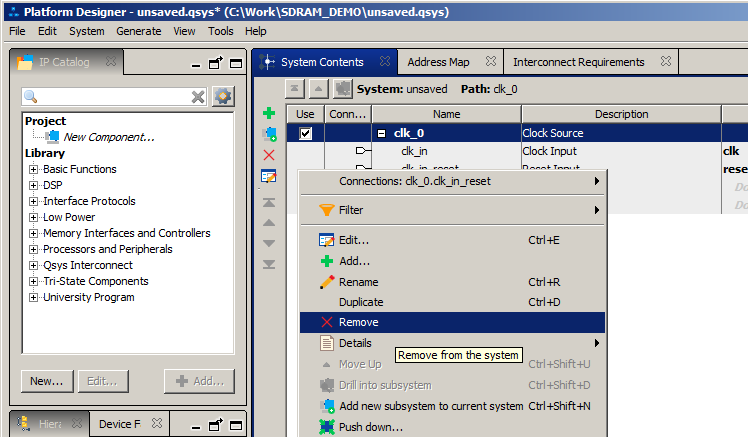

ولكن كما ذكرت بالفعل ، يلزم تسجيل وقت خاص لجوهر SDRAM. لذلك ، يتم طرح الوحدة القياسية بلا رحمة

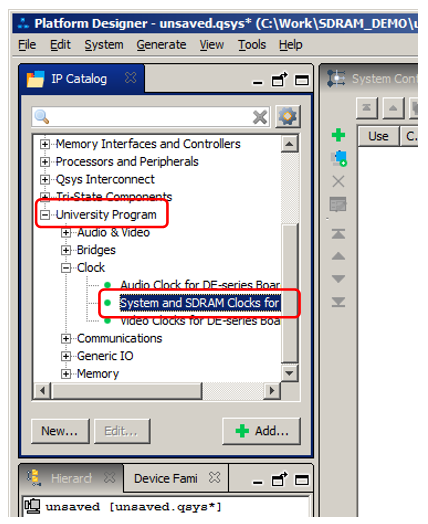

وبدلاً من ذلك ، أضف University Program-> System و SDRAM Clock for DE board series:

في الخصائص ، حدد DE0-Nano ، حيث تم استلهام دائرة تبديل SDRAM من هذه اللوحة:

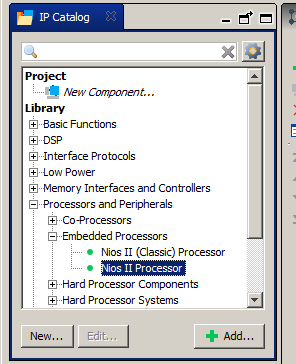

نبدأ في الاشياء نظام المعالج لدينا. بطبيعة الحال ، فإن أول شيء تضاف إليه هو جوهر المعالج نفسه. فليكن المعالج والأجهزة الطرفية-> المعالجات المضمنة-> معالج NIOS II.

بالنسبة له ، نحن لا نملأ أي عقارات بعد. فقط انقر فوق "إنهاء" ، على الرغم من أننا شكلنا سلسلة من رسائل الخطأ. حتى الآن ، لا توجد معدات من شأنها القضاء على هذه الأخطاء.

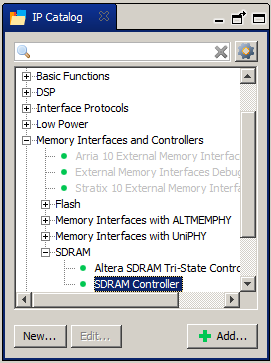

الآن إضافة SDRAM الفعلي. واجهات الذاكرة وأجهزة التحكم-> SDRAM-> SDRAM المراقب المالي.

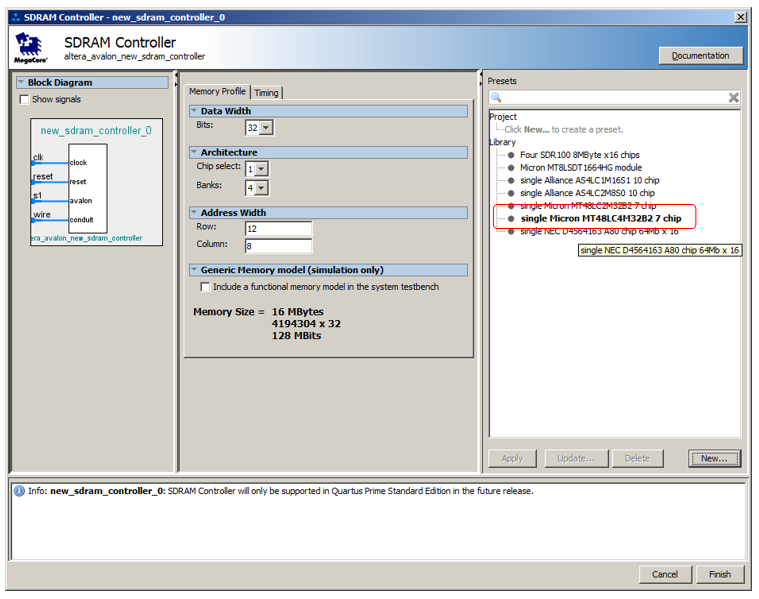

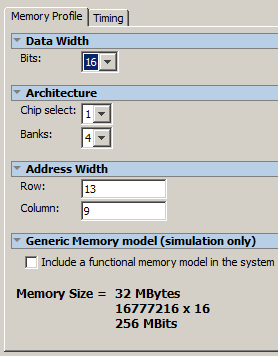

هنا علينا التمسك بملء الخصائص. حدد أقرب دائرة كهربائية متشابهة في المؤسسة من القائمة وانقر فوق Apppy. خصائصه تقع في حقول ملف تعريف الذاكرة:

الآن نقوم بتغيير عرض ناقل البيانات إلى 16 ، وعدد خطوط العناوين إلى 13 ، والأعمدة إلى 9.

لم أقم بتصحيح الأوقات ، ربما سيتم تغيير هذه التوصية في المستقبل.

نظام المعالج يعني وجود برنامج. يجب أن يتم تخزين البرنامج في مكان ما. سنختبر رقاقة SDRAM. في الوقت الحالي ، لا يمكننا الوثوق بها. لذلك ، لتخزين البرنامج ، إضافة ذاكرة تستند إلى كتلة RAM FPGA. الوظائف الأساسية-> في رقاقة الذاكرة-> على رقاقة الذاكرة (RAM أو ROM):

حجم ... حسنا ، فليكن 32 كيلو بايت.

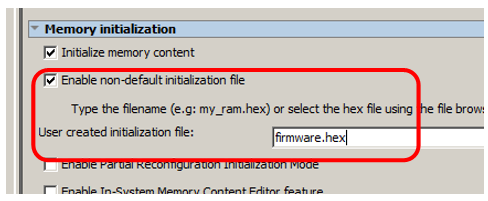

يجب أن يتم تحميل هذه الذاكرة من مكان ما. لكي يحدث هذا ، حدد مربع تمكين ملف التهيئة غير الافتراضي وأدخل اسم ملف ذا معنى. دعنا نقول firmware.hex:

المقالة معقدة بالفعل ، لذلك لن نفرط في تحميلها. سنقوم ببساطة بإخراج النتيجة الفعلية للاختبار في شكل خطوط PASS / FAIL (وسنرى النتيجة المنطقية باستخدام تصحيح JTAG المفضل لدي). للقيام بذلك ، أضف منفذ GPIO. المعالجات والأجهزة الطرفية> الأجهزة الطرفية> PIO (IO الموازي):

في الخصائص التي وضعناها 2 بت ، أود أيضًا تحديد المربع للتحكم الفردي في البتات. أيضا مجرد عادة.

لقد حصلنا على مثل هذا النظام مع مجموعة من الأخطاء:

نبدأ في القضاء عليهم. بادئ ذي بدء ، فإننا سوف كسر على مدار الساعة وإعادة تعيين. على مدار الساعة ووحدة إعادة الضبط ، يجب التخلص من المدخلات. للقيام بذلك ، هناك حقول تقول "انقر نقرًا مزدوجًا للتصدير":

نقر ، لكننا نقدم أسماء قصيرة أو أكثر.

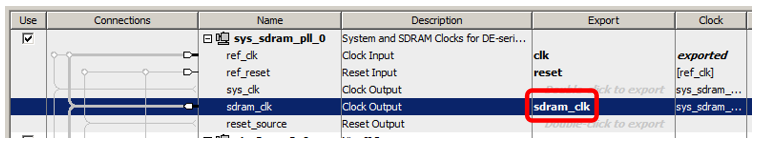

تحتاج أيضًا إلى إخراج إخراج ساعة SDRAM:

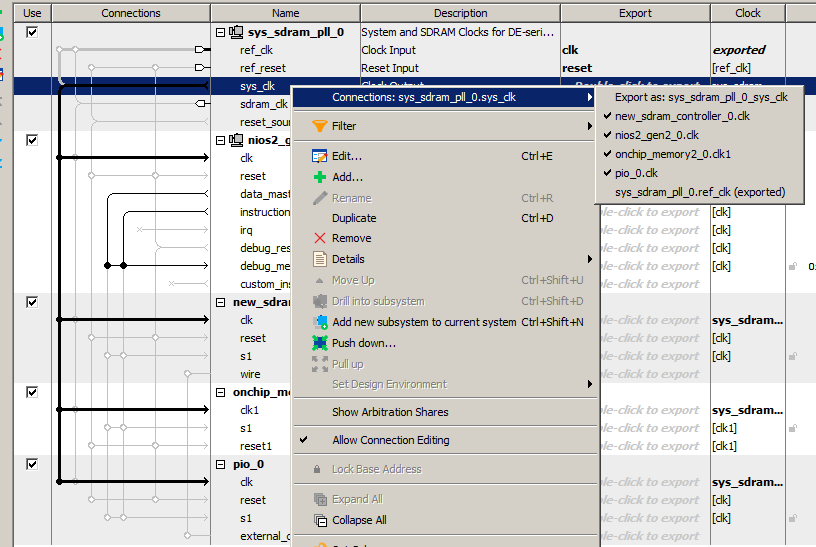

الآن نقوم بتقسيم sys_clk إلى جميع مدخلات الساعة ، و reset_source إلى جميع خطوط إعادة التعيين. يمكنك ضرب النقاط التي تربط الخطوط المقابلة مع "الماوس" بلطف ، أو يمكنك الانتقال إلى الخروج المقابل ، اضغط على زر الماوس الأيمن ، ثم انتقل إلى القائمة الفرعية اتصالات في القائمة المنسدلة واختر الاتصالات هناك.

ثم نربط الإطارات معا. نحن نربط Data Master بجميع حافلات جميع الأجهزة ، و Inctruction Master - إلى جميعها تقريبًا. ليس مطلوبًا توصيله بحافلة PIO_0. من هناك ، بالتأكيد لن تتم قراءة التعليمات.

الآن يمكنك حل تعارضات العناوين. للقيام بذلك ، حدد عنصر القائمة النظام> تعيين العناوين الأساسية:

وعندما نحصل على عناوين ، يمكننا أيضًا تعيين متجهات. للقيام بذلك ، انتقل إلى خصائص كور المعالج (أشر إليه ، اضغط على زر الماوس الأيمن وحدد عنصر القائمة تحرير) وقم بتكوين المتجهات على ذاكرة Onchip هناك. ما عليك سوى اختيار هذا النوع من الذاكرة في القوائم المنسدلة ، وسيتم استبدال الأرقام بنفسها.

لا توجد أخطاء اليسار. ولكن لا يزال هناك تحذيران. لقد نسيت تصدير خطوط SDRAM و PIO.

كما فعلنا بالفعل من أجل إعادة التعيين وحظر الساعة ، انقر نقرًا مزدوجًا على الأرجل المطلوبة ومنحهم أقصر الأسماء (ولكن المفهومة):

كل شيء ، لا يوجد المزيد من الأخطاء أو التحذيرات. احفظ النظام علاوة على ذلك ، يجب أن يتطابق الاسم مع اسم المشروع حتى يصبح نظام المعالج عنصرًا في المستوى الأعلى في المشروع. لم تنس ما نسميه؟

حسنًا ، نضغط على الزر الأكثر أهمية - توليد HDL.

كل شيء ، يتم إنشاء جزء المعالج. انقر فوق "إنهاء". يتم تذكيرنا بأنه سيكون من الجيد إضافة نظام المعالج هذا إلى المشروع:

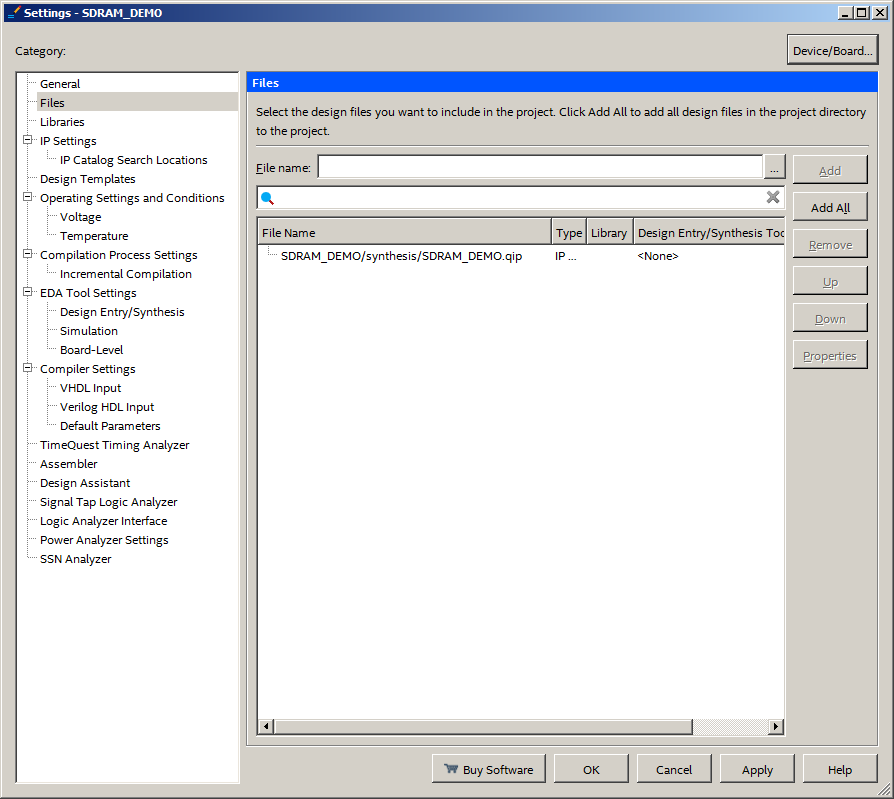

مضيفا:

وهناك ، باستخدام زر الإضافة ، نحقق الصورة التالية:

لم يتم إنشاء ملف SIP بعد. نعم ، ونحن لسنا في حاجة إليها في إطار هذه المقالة.

Ufff. لقد اتخذت الخطوة الأولى. نقوم بصياغة المشروع بحيث يكتشف النظام التسلسل الهرمي للمشروع والأرجل المستخدمة. أخطاء التجميع ليست مخيفة. فقط في الإصدار المجاني من البيئة ، تم إنشاء حبات تعمل فقط أثناء اتصال محول JTAG. لكن في مجمع Redd ، يكون متصلاً دائمًا ، لأنه مطلق على لوحة مشتركة ، وهذا ليس لدينا ما نخشاه. لذلك نحن نتجاهل هذه الأخطاء.

عد الآن إلى وصف نواة SDRAM. تقول أن خط CKE غير مستخدم ومتصل دائمًا بالوحدة. في الواقع ، في إطار المجمع ، أرجل FPGA ليست باهظة الثمن فحسب ، ولكنها مورد ثمين. وسيكون من الحماقة نشر الساق ، التي توجد دائمًا في الوحدة (وعلى لوحة DE0-NANO ، لا يتم فصلها أيضًا). ستكون هناك طبقة Verilog ، يمكن قطع السلسلة المقابلة هناك ، لكنني أوفر الوقت (ضحك عصبي ، أنظر إلى حجم المستند الذي تم الحصول عليه بالفعل ، ولكن بدون حفظه كان سيتحول أكثر). لذلك ، لا يوجد طبقة. كيف تكون انتقل إلى محرر الواجب. في ذلك ، لأنه في Pin Planner ، وفقًا للأوصاف ، لا توجد وظائف مماثلة.

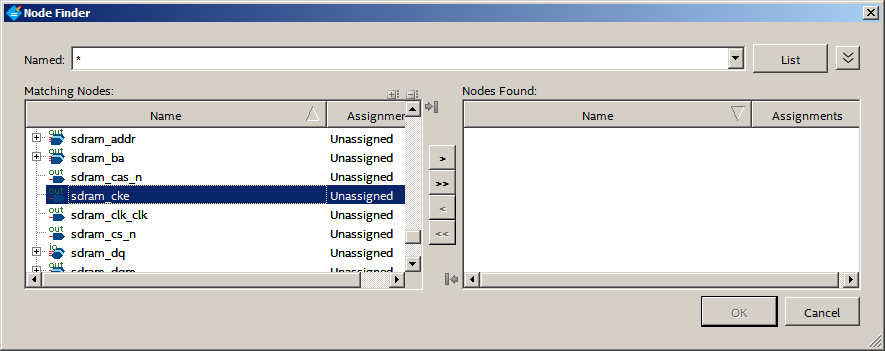

لا يوجد حتى الآن خط. حسنا. إنشاء واحدة جديدة

نختار الأيقونة التالية:

في نظام البحث الذي حددناه ، انقر فوق قائمة وفي نتائج البحث ، وجدنا CKE لدينا:

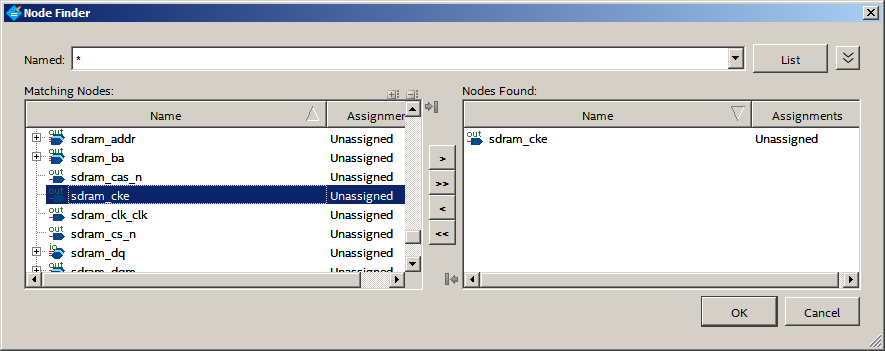

إضافته إلى العمود الأيمن ، انقر فوق "موافق".

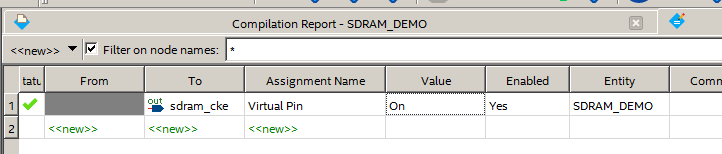

نحصل على القائمة التالية:

في الحقل الأصفر ، انقر فوق القائمة المنسدلة وابحث عن Virtual Pin. نختار. انتقلت الصفرة إلى خلية أخرى:

هناك نختار على:

ذهب كل اصفرار. وقد تم وضع علامة على السلسلة الآن على أنها افتراضية ، مما يعني أنها لا تتطلب ساقًا بدنية. لذلك ، لا يمكننا تعيينه إلى الاستنتاج المادي لـ FPGA. أغلق محرر الواجب ، افتح Pin Planner. يمكنك تعيين الأرجل ، بالإشارة إلى الشكل ، أو يمكنك أخذ القائمة من ملف * .qsf ، الذي يعد جزءًا من المشروع ، والذي سأرفقه بالمقال.

هذا كل شيء ، وثيقة Pin Planner ، نقوم بتنفيذ التجميع النهائي للمشروع. الجهاز جاهز ، نواصل تطوير البرنامج لنظام المعالج الناتج. لكن المقالة اتضح أنها ضخمة لدرجة أننا سنفعلها

في المرة القادمة .