لديك هذا الحلم: تجد نفسك في اختبار أو تتحدث أمام جمهور معين ، وفجأة تدرك أنك لم تكن تستعد على الإطلاق ، وعليك الآن الارتجال. في هذه الحالة ، ولكن ليس في المنام ، ولكن في الحياة الواقعية ، واجهت عطلة مايو في موسكو ، حيث سافرت من كاليفورنيا لإجراء ندوة مدتها ثلاثة أيام لأطفال المدارس الذين تم اختيارهم بعناية من مدارس الفيزياء الرائدة في موسكو. تحت رعاية RUSNANO ، في صالة RUT للألعاب الرياضية (MIIT) وبحضور معلمين من MIET و MIREA و MEPhI و MPEI و HSE MIEM.

اعتمد زملائي في موسكو علي ، ومن الناحية النظرية ، كان ينبغي عليّ أن أحضر إرشادات خطوة بخطوة وأمثلة على التدريبات المختلفة على لوحة دوائر مزودة بدائرة كهربائية منطقية قابلة لإعادة التشكيل. في الواقع ، كان لدي مجموعة من الأمثلة على المجالس الأخرى ، والتي لم أقوم ببناء أي شيء في فوضى الرحلات الجوية وغيرها من الأحداث.

لذلك ، أخذت مثالًا عالميًا ، كتبت منذ عام ونصف العام ، جالسًا على متن طائرة ألما-آتا أستانا ، وأطردت جميع الدواخل من المثال ، وبدأت في ملؤها بأطفال المدارس دون خطة قاسية. والغريب بما فيه الكفاية - أنها عملت. أثناء عملية التعبئة ، نشأت لحظات مفيدة من الدوائر الرقمية ولغة وصف أجهزة Verilog ، والتي لن تنشأ أثناء التخطيط.

في الرابع من يونيو ، قمت أنا وزملائي في Wave Computing بعقد حلقة دراسية مماثلة في لاس فيجاس ، ولكن للبالغين فقط ، وفي الفترة من 8 إلى 19 يوليو ، ساعدت MIET على إدارة مدرسة صيفية في زيلينوغراد. خطط لهذه الأحداث (ليست نهائية ، ولكن للمناقشة في مجموعة من المعلمين والمهندسين ، بما في ذلك هنا على Habré) - في نهاية المنشور.

لماذا نحتاج إلى حلقة دراسية حول FPGAs لأطفال المدارس؟ تعد الدوائر المتكاملة المنطقية القابلة للبرمجة (FPGAs أو FPGAs - صفائف بوابة قابلة للبرمجة الميدانية) طريقة تقليدية لتوحيد المعرفة في الممارسة العملية عند دراسة تصميم الدوائر الرقمية على مستوى عمليات نقل السجلات باستخدام لغات وصف الأجهزة. وبعبارة أخرى ، فإن التكنولوجيا الرئيسية لتطوير أجهزة iPhone - الرقائق الدقيقة داخل أجهزة iPhone مصممة بهذه الطريقة. كان تأخر روسيا خلف أجهزة iPhone يرجع إلى حقيقة أن FPGAs ، والهندسة المعمارية المصغرة ولغات وصف الأجهزة تم تقديمها في بيركلي ومعهد ماساتشوستس للتكنولوجيا في أوائل التسعينيات ، وفي روسيا بسبب انهيار الاتحاد السوفيتي في وقت لاحق.

مرت ندوة روسنانوف الأخيرة بسلاسة وبشكل مفاجئ في المقام الأول لأن الطلاب الذين حضروا إليها استهلوا دورة تدريبية نظرية عبر الإنترنت من خلال استقصاء موجه مهنيًا لأساليب تصميم الدوائر الصغيرة الحديثة. الدورة التدريبية عبر الإنترنت مخصصة لتلاميذ المدارس المتقدمين من النوع الأوليمبيدي وتتكون من ثلاث وحدات:

"من الترانزستور إلى الدائرة الصغيرة" و

"الجانب المنطقي للدوائر الرقمية" و

"الجانب المادي للدوائر الرقمية" . في هذه الدورة ، يتعرف الطلاب على ما يسمى بمسار RTL2GDSII - وهي مجموعة من التقنيات التي يستخدمها المهندسون في الشركات الإلكترونية لتصميم الرقائق المجمعة ، الدوائر المتكاملة للتطبيقات المحددة - ASIC. تُستخدم FPGAs / FPGAs في إعداد نماذج ASIC الأولية ، بما في ذلك شركات مثل Intel و Apple و NVidia.

منذ أن أخذ الطلاب الدورة التدريبية عبر الإنترنت ، تعلموا بالفعل ما هي D-trigger وآلة الحالة والتوليف المنطقي والتتبع. ورأوا أيضًا لغة وصف الأجهزة في الدورة التدريبية عبر الإنترنت. الآن هذه المعرفة ، التي تكمن بشكل سلبي في ذاكرتهم ، تحتاج فقط إلى إحياء.

الآن سأقوم دائمًا بحضور أي حلقات دراسية في بلدان رابطة الدول المستقلة (بالإضافة إلى الندوات التي تم التخطيط لها بالفعل ، لديّ مقترحات لعقدها في مينسك وسوتشي وياكوتسك) لوضع شروط للجانب المضيف لاستقبال تلاميذ المدارس أو الطلاب من خلال ثلاث وحدات للدورة عبر الإنترنت ، منذ بعد يبقى فقط الأشخاص الذين لديهم دوافع والذين مروا بالفعل بجميع الجوانب المملة ، والإبداع الخالص يظل قائما لتعزيزه ، آخر لحظة ، مثل سقوط تفاحة ضربت رأس نيوتن. بالإضافة إلى ذلك ، فإن الدورة التدريبية عبر الإنترنت تربط كل هذا النشاط بمهن البالغين ، وتوجه المرحلة التالية إلى هدف بعيد.

إجمالاً ، قبل السفر إلى موسكو ، أطلقت مثالًا عالميًا في منزلي في سانيفيل ، كاليفورنيا.

رمز المثال :

في اليوم الأول من ورشة العمل ، مارسنا بدورات كهربائية صغيرة مع درجة صغيرة من التكامل على اللوح. يبلغ عمر هذه التكنولوجيا 50 عامًا ، ولكن لم يأت أحد بفكرة أفضل ، في الحياة الواقعية ، أكثر من المحاكاة ، لإظهار كيفية عمل مشغلات D ، على سبيل المثال. على الرغم من أنه يبدو لكثير من معلمي التكنولوجيا الحديثة في المدارس أنه قديم وغير ضروري ، ولكن الآن في الدورة 6.111 من معهد ماساتشوستس للتكنولوجيا ، والآن ، في العام الدراسي 2018/2019 ، يذهب المختبر الأول في الدوائر الرقمية بهذه الطريقة تمامًا مع الدوائر الصغيرة ذات درجة صغيرة من التكامل - راجع

http: //web.mit.edu/6.111/volume2/www/f2018/index.html .

بالإضافة إلى ذلك ، باستخدام مثال لتوصيل الدوائر الصغيرة بدرجة صغيرة من التكامل مع الأزرار ، من المريح شرح ماهية هذا السبب ولماذا يلزمه وكيف تعمل مقاومات السحب. ولماذا تعطي إمكانية 0 عند عدم الضغط على الزر ، وكيف يرتبط ذلك بمقسم الجهد.

حتى عندما ، على سبيل المثال ، بدائرة كهربائية صغيرة بدرجة صغيرة من التكامل ، يحترق مؤشر LED ، يحصل الطلاب على تجربة الحياة أنه من الضروري وضع المقاوم هناك. إذا رأوا ذلك على شاشة الكمبيوتر في أحد برامج محاكاة اللوح ، فلن يحصلوا على هذه التجربة الحياتية ، حيث يمكنك رسم أي شيء على الشاشة ولن يتأكد تلاميذ المدارس من أن الإرهاق حقيقي.

إليكم كيفية ظهور وظيفة D-flip-flop بوضوح على الدوائر الصغيرة ذات درجة التكامل الصغيرة:

بدأ اليوم الثاني برسم تاريخي: كيف تم تصميم الرقائق منذ 50 عامًا وكيف تغيرت مرتين منذ ذلك الحين. تم فرض أحد الثورات على انهيار الاتحاد السوفيتي وهذا هو السبب التقني الرئيسي لعدم امتلاك روسيا لأجهزة iPhone.

في الساعة 8.45 ، تم القبض على قصة تجسس العوالم السوفيتية ، التي راقبت حركة السفن الأمريكية ، في المحيطات ، وما أدى إلى ذلك.

في 13 مارس ، قصة كيف قام أحد المدونين جون كولي بنقل الصناعة العالمية بأكملها من VHDL إلى Verilog.

في 16.10 ، قصة كيف خسر مايكروسوفت ويندوز لينكس كمنصة لعمل مصممي الرقائق.

في هذا الجزء - عرض توضيحي لكيفية تشغيل برنامج لتوليف المنطق الرقمي وتكوين البرامج الثابتة في FPGA. بطريقتين - عن طريق تشغيل البرنامج النصي تحت لينكس وفي قذيفة رسومية متكاملة. أيضا وصفا موجزا لمحتويات التجريبي. بعد هذا الركض في جميع أنحاء أوروبا ، يجلس الطلاب على غلاف الرسوم ويقومون بتمارين بسيطة ، بدءًا من العناصر المنطقية AND-OR-NOT ، والتي ترتبط مدخلاتها بالأزرار ومخرجات LEDs. شيء من هذا القبيل:

module top (input [2:0] key, output [7:0] led); wire a = ~ key [0]; // 0, , wire b = ~ key [1]; wire c = a & b; assign led [0] = ~ c; // , 0 endmodule

في هذه العملية ، ظهر سؤالان مثيران على الفور. أولاً ، أولاً نسيت نفسي أن كل من الأزرار ومصابيح LED مقلوبة في هذا المنتدى. وهذا هو ، عند الضغط على الزر ، ثم 0 على السلك ، وعندما لا يتم الضغط عليه ، ثم 1. وعندما يتم تغذية 0 إلى LED ، يكون قيد التشغيل ، وعندما لا يكون 1 قيد التشغيل. إذا كنت لا تعرف الانعكاس ، فسيبدأ العنصر المنطقي AND (led [0] = key [0] & key [1]) في التصرف مثل OR ، و OR - مثل I. Law of de Morgan in action! ~ (a & b) == ~ a | ~ b ، وكذلك ~ (a | b) == ~ a & ~ b.

ولكن حتى بعد تصحيح بعض تلاميذ المدارس ، لا يزال هذا العمل يعمل في الاتجاه المعاكس. ثم نظرت إلى الكود ووجدت أنه عندما كانوا يعيدون كتابة الكود الذي كتبته على السبورة ، ظنوا أن "~" (التلدة) هي "-" (ناقص). لقد أعطاني هذا سببًا ممتازًا للتحدث عن الفرق بين الكود

المباشر والرمز

الإضافي ، وأيضًا سبب وجود أرقام بت واحدة (- 0) == 0 و (- 1) == 1 ، بينما (~ 0) == 1 و (~ 1) == 0. وأيضًا ، من أجل حساب النفي للأرقام متعددة البتات في كود إضافي ، يكفي عكس ذلك في اتجاه عقارب الساعة وإضافة واحد: - a == ((~ a) + 1).

استمرار - أجزاء

2.3 ،

2.4 ،

2.5 .

تم عقد الدرس بالكامل في نظام Linux ، وبشكل أكثر دقة تحت Lubuntu 18.04 مع تثبيت Intel FPGA Quartus II عليه. تم تحميل Lubuntu بمحركات الأقراص الثابتة التي تم تثبيت Intel FPGA Quartus II Lite Edition 18.1 عليها أيضًا. للتمهيد من SSD ، تحتاج فقط إلى توصيله بمنفذ USB 3.0 وتشغيل الكمبيوتر والضغط على المفتاح F12. ثم أدخل القائمة وقل "تحميل من USB".

على الرغم من أن برنامج التوليف لـ FPGA متاح أيضًا في نظام Windows ، إلا أن Linux مفيد لسببين:

1. Linux قادر على التشغيل على أجهزة كمبيوتر أضعف من Windows. على سبيل المثال ، لدي جهاز كمبيوتر محمول به ذاكرة 2 جيجا بايت ، لذا فإن Intel FPGA / Altera Quartus II for Windows يضعها على الجهاز ، ويعمل بشكل جيد في نظام Linux.

2. يستخدم جميع مطوري البرامج الكبار من الرقائق الكبيرة في Apple و NVidia وغيرها من الشركات الإلكترونية Linux ، الذي يقوم بتشغيل البرامج Synopsys Design Compiler و Synopsys IC Compiler و Synopsys VCS و Cadence IES ، إلخ.

لماذا من الأفضل أن تفعل كل شيء على سواقات الأقراص الصلبة القابلة للتشغيل وعدم وضعها على أجهزة الكمبيوتر في الفصول الدراسية؟ نظرًا لأن تثبيت البرامج من شركات FPGA يعد عملية كئيبة ، وحول Altera Quartus أو Xilinx Vivado ، فأنت بحاجة إلى تشغيل مع الدف ، وتغيير الملفات في / الخ وتثبيت مكتبات 32 بت قديمة لبعض المكونات ، على وجه الخصوص ، للحصول على الإصدار المجاني من Mentor ModelSim. يجب أن يتم تجميع بعض المكتبات من أكواد المصدر. هناك

نصوص من Stanislav Zhelnio تقوم بكل ذلك تلقائيًا ، ولكن حتى مع هذا البرنامج النصي ، سيستغرق تثبيت كل شيء على جهاز الكمبيوتر بضع ساعات.

لماذا لا تفعل كل شيء في الأجهزة الافتراضية؟ على سبيل المثال مع VirtualBox؟ لقد جربنا هذا في جامعة موسكو الحكومية وغيرها من الأماكن ، ولكن يمكن أن تحدث مواطن الخلل مع سحب USB هناك. يبدو SSD القابل للتشغيل مع Lubuntu الخيار الأفضل.

لإعداد SSD لتعيين ورشة العمل ، تحتاج إلى وضع كل شيء على SSD واحد ، ثم استنساخه باستخدام أمر يتيح لك الكتابة على الفور إلى ثلاثة SSDs من واحدة:

time sudo dcfldd if=/dev/sdb bs=1M of=/dev/sdc of=/dev/sdd of=/dev/sde

هنا تحتاج إلى معرفة أن حاويات SSD ليست كلها تدعم Linux ، على سبيل المثال ، غنائم Kingwin Data Star للأقراص. العبوات الصحيحة هي Orico و Eluteng.

أيضًا ، لا أوصي بمحاولة استبدال محركات أقراص الحالة الصلبة بمحركات أقراص فلاش USB بسيطة وقابلة للتنزيل. على الرغم من أنه يعمل أيضًا على عصي USB ، إلا أن بعض العمليات بطيئة بشكل لا يصدق ، مما يسبب عدم الراحة والتهيج. ولكن على محركات أقراص SSD المحملة المزودة بـ USB 3.0 ، كل شيء يسير أسرع من نظام Linux على محرك أقراص ثابت داخلي.

حاولت أيضًا التمسك بمحرك أقراص SSD قابل للتمهيد في Apple Mac عن طريق الضغط على مفتاح Option في وقت التمهيد ، لكنه لم ينجح. لا من خلال منفذ USB 3.1 ، ولا من خلال 3.0. يبدو أن نظام التشغيل Mac عند التمهيد لا يريد فهم نظام الملفات Ext4 أو جدول القسم. هل هناك برامج تشغيل خشخاش و linuxoids بين القراء؟ سيكون من المثير للاهتمام معرفة ما يجب القيام به (إلى جانب خيار استخدام VirtualBox أو الأجهزة الظاهرية الأخرى).

ومن المثير للاهتمام أن اثنين فقط من الطلاب من المجموعة بأكملها استخدموا Linux قبل الندوة. هذا غريب جدًا بالنسبة لي ، حيث أنه في مكان وزارة التعليم الروسية أود أن أنقل جميع المدارس الروسية إلى نظام Linux قبل 10 سنوات ، عندما أصبح Ubuntu سهل الاستخدام. بالإضافة إلى أوبونتو ، يمكن للمرء أن يصنع نسخة روسية خاصة من نظام Linux للتعليم. نوافذ مسدودة بالفيروسات ، أنت بحاجة إلى دفع إتاوات مقابل ذلك ، لماذا يكون Windows أفضل من نظام Linux ليقول دورات بيثون المدرسية؟ أم أن مستندات Google لن تكون كافية لتلاميذ المدارس ، ولكن هناك حاجة إلى Microsoft Word؟ أنا فقط لا أفهمها.

حتى حكومة كوريا الجنوبية قررت في عام 2020 التحول إلى نظام Linux .

على أي حال ، في الحلقة الدراسية الخاصة بي ، لم يكن لدى تلاميذ المدارس أي مشكلة في نظام Linux ، على الرغم من أنني ، كما قلت ، استخدمها معظم الأطفال لأول مرة.

في بداية اليوم الثالث ، تأخرت لأنني دُعيت لإلقاء محاضرة للفرع الروسي من Samsung والحدث الذي استمر لمدة 3 ساعات (يمكنك تنزيل شرائح المحاضرة:

1 و

2 و

3 ومقال عن جزء من المحتوى ) ، وبعد ذلك شعرت بالجوع. إن تناول الحنطة السوداء وزيت الزيتون في مومو (الذي افتقده حقًا في كاليفورنيا) وجد أن درسي في صالة الألعاب الرياضية سيبدأ خلال 5 دقائق.

ثم اتصلت بالكسندر Silantiev من MIET وطلبت أن أبدأ الدرس بدوني. في اليوم السابق ، بدأ الطلاب في ممارسة الرياضة باستخدام مؤشر من سبعة أجزاء ، يعرض حرفًا واحدًا. الآن ، إذا تجاوزت ناتج حرف واحد بسجل إزاحة ، فيمكنك تنفيذ الإخراج على مؤشر سبعة قطاعات ديناميكي متعدد بت ، وفي الوقت نفسه ، سيتعلم الطلاب كيفية ترميز المنطق المتسلسل على veril.

كانت الخطة ناجحة - عندما دخلت الفصل الدراسي ، كان بعض تلاميذ المدارس يقومون بالفعل بتشغيل الحروف ببطء على المؤشر الديناميكي ، وهكذا اندمجوا في الكلمات ، كل ما كان مطلوبًا هو رفع وتيرة توليد إشارة تمكين (تمكين) لسجل التحول:

ثم أعطيت الكلمة لستانيسلاف تشيلنيو

سبارف من شركة IVA Technologies ، وقد أوجز بإيجاز كيفية الانتقال من كتل المنطق البسيطة إلى معالج صغير ولكنه حقيقي تمامًا (انظر

منشورات Stanislav على Habr و

schoolMIPS على GitHub ):

استمرار المحاضرة التي كتبها ستانيسلاف تشيلنيوعقدت الندوة في مدرسة القواعد بجامعة النقل الروسية (MIIT). في الندوة وقبلها ، ساعدت إيرينا جرونشيفا وجليب رومانوف (eNano) ؛ أليكسي بيرفيرزيف ، ألكساندر سيلانتييف وإفغيني بريماكوف من MIET ، ألكساندر رومانوف من HSE MIEM وطلابه ، أليكسي Kochnov من NIIIS ، League of Robots (obraz.pro) ، Pavel Kirichenko (ICST ، Intel ، مؤلف الكتب

bhv.ru/books/book). php؟ id = 201192 ) ، كان Yegor Kuzmin من

معهد الرياضيات التطبيقية ، الأكاديمية الروسية للعلوم ، Daria Krivoruchko ، تلميذة من SUNTs ، في LYuP ، Timofey Cherkasov (أكاديمية التقنيات الرقمية في سانت بطرسبرغ ، كلية التفكير الهندسي LNMO) ، ألكسندر بيكروف ، وجوليا شلتايفا فورونتسوف من MPEI ، يفغيني بيفتسوف من MIREA ، فيتالي Kravchenko من Nautekh ، Arkady Poe ياكوف وسيرجي Pevchenko من MEI.

جلب رسلان تيخونوف من Amperka مكونات للتمارين مع الدوائر الصغيرة بدرجة صغيرة من التكامل.

قام الناشر ديمتري موفشان ، من DMK Press ، بتزويد كل مشارك بكتب مفيدة - كتاب مدرسي شامل كثيف من تأليف ديفيد هاريس وسارة هاريس ، والدوائر الرقمية وهندسة الكمبيوتر ، وقراءة سهلة من قبل أ. الدوائر الرقمية. المانجا.

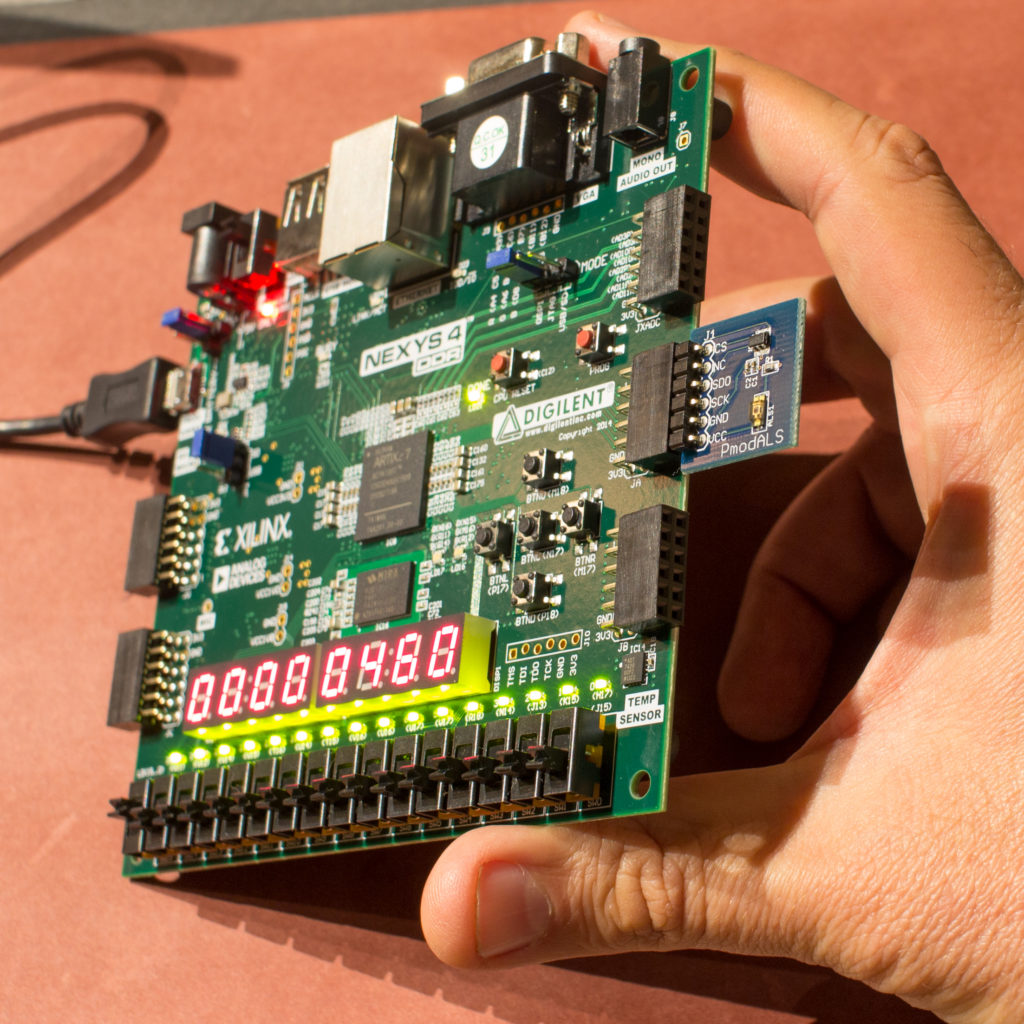

حضر ماكسيم ماسلوف ، المرتبط بمعهد موسكو للفيزياء والتكنولوجيا ، الندوة وتبرع بألواح FPGA للمدارس الصيفية (اعتادوا على القول إنه في روسيا يوجد القليل من الأعمال الخيرية للتعليم).

ماذا سيحدث بعد ذلك؟ وبعد ذلك ، سيكون هناك حدثان من شأنه توسيع وتعميق ما فعلناه في مدرسة RTH Grammar School. من 8 إلى 26 يوليو ستكون المدرسة الصيفية MIET في زيلينوغراد. هنا اقتراح لبرنامجها. يتكون أول أسبوعين لها من خمسة أجزاء:

- أساسيات الدوائر الرقمية على الدوائر الصغيرة بدرجة صغيرة من التكامل.

- تمارين بسيطة مع منطق التوافقية ومتسلسل على لوحة FPGA.

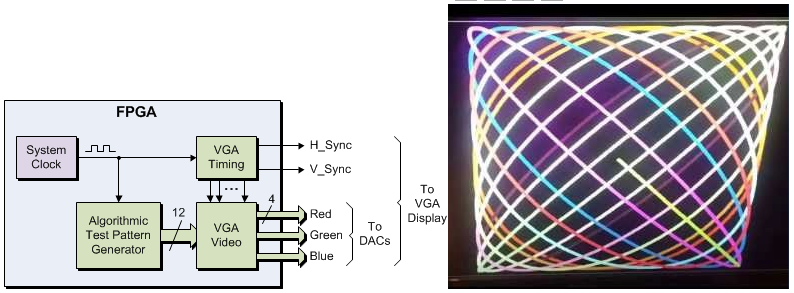

- استخدام FPGAs للتحكم في عرض الرسوم.

- الجهاز وتنفيذ أبسط معالج دقيق على FPGA.

- مشاريع فردية لإنشاء ألعاب Angry Birds مبسطة ، كلاهما يعتمد على جهاز الحالة في أجهزة FPGA بحتة ، ومع التحكم في البرنامج من أبسط معالج تم تصنيعه في FPGA.

ولكن قبل المدرسة في 4 يونيو ، ستكون هناك ندوة في لاس فيجاس ، والتي لن نتعامل فيها مع معالج المدرسة ، ولكن مع المعالج الصناعي.

برنامج أكثر تفصيلا في Zelenograd:

الأسبوع 1. أساسيات المنطق الرقمي.

اليوم 1. دوائر متكاملة صغيرة الحجم ، تمارين منطق اندماجي

اليوم 2. دوائر مصغرة مع درجة صغيرة من التكامل ، وتمارين مع منطق تسلسلي

اليوم 3. FPGA ، تمارين مع الأزرار ، مفاتيح ، LED ، مؤشر سبعة قطعة

اليوم 4. FPGA ، إخراج الأشكال الهندسية إلى VGA

يوم 5. FPGA ، آلة الدولة لطيور غاضبة

الأسبوع 2. المعالج

اليوم 1. البرمجة في لغة التجميع.

اليوم 2. دورة واحدة schoolMIPS المعالج.

اليوم 3. تفاعل المعالج مع الانتهاء من الأشكال الهندسية على VGA.

اليوم 4. محاضرة عن الانقطاع وتعدد المهام. مشروع فردي - لعبة فيديو مبرمجة على المعالج مع إخراج إلى VGA.

يوم 5. محاضرة عن الناقل. منافسة المشاريع الفردية.

الأسبوع 1. اليوم 1. دوائر متكاملة صغيرة الحجم.

1.1. تمارين مع منطق اندماجي.

1.1.1. عنصر المنطق XOR على CD4070 ، بدون أزرار وسجلات السحب - كرر العرض.

1.1.2. عنصر المنطق XOR ، إضافة أزرار وسجلات السحب - كرر العرض.

1.1.3. مهمة فردية - من خلال مجموعة البيانات لإنشاء عرض توضيحي لأحد العناصر المنطقية و / أو / لا / XOR / NOR / NAND / XNOR ، مع اثنين أو ثلاثة أو أربعة أو ثمانية مدخلات:

1.1.3.1. CD4081 ، رباعية 2-الإدخال و

1.1.3.2. CD4071 ، رباعي الإدخال أو OR

1.1.3.3. CD4011 ، رباعي الإدخال NAND

1.1.3.4. CD4001 ، رباعي الإدخال 2 NOR

1.1.3.5. CD4073 ، ثلاثة مدخلات و

1.1.3.6. CD4025 ، ثلاثية 3-الإدخال NOR

1.1.3.7. CD4082 ، المزدوج 4 الإدخال و

1.1.3.8. CD4072 ، ثنائي 4 - الإدخال أو

1.1.3.9. CD4012 ، ثنائي 4-الإدخال NAND

1.1.3.10. CD4002 ، 4 مدخلات NOR

1.1.3.11. CD4068 ، 8 المدخلات و NAND

1.1.3.12. CD4078 ، 8 مدخلات NOR

1.2. مؤشر من 7 شرائح مع كاثود مشترك.

1.2.1. تجميع على اللوح مع المقاومات ، حاول شرائح الفردية.

1.2.2. مزيج مع برنامج تشغيل مؤشر 7 قطاعات ، CD4511 ، BCD إلى 7-القطعة فك مزلاج.

1.2.3. الخيار - مؤشر مع الأنود المشترك. تتحد مع العاكس CD4069 ، العاكس.

1.2.4. الخيار - إضافة 4 أزرار مع مقاومات قابلة للسحب لإدخال CD4511.

1.3. كتل المنطق التوافقية - مهمة فردية في نهاية اليوم أو في شكل واجبات منزلية:

1.3.1. CD4532 ، 8 بت الأولوية التشفير

1.3.2. CD4051 ، مفتاح تناظري ذو 8 قنوات ، يستخدم كجهاز فك تشفير رقمي

1.3.3. CD4051 ، مفتاح تناظري ذو 8 قنوات ، يستخدم كمضاعف رقمي

1.3.4. CD4052 ، مفتاح تناظري ثنائي القناة ، يستخدم كمضاعف رقمي

1.3.5. CD4053 ، مفتاح تناظري ثلاثي القنوات ، يستخدم كمضاعف رقمي

1.3.6. CD4008 ، 4 بت Comberational Adder

1.3.7. CD4063 ، مقارن رقمي 4 بت

1.3.8. CD4585 ، مقارن رقمي 4 بت

في نهاية اليوم ، يظهر الجميع من فعل ما.

الأسبوع 1. اليوم 2. تمارين مع منطق تسلسلي.

1.2.1. قم بتجميع مولد ساعة على أساس رقاقة 555. جرب المكثفات والمقاومات المختلفة.

1.2.2. D- الزناد على رقاقة CD4013 ، المزدوج D- الوجه بالتخبط مع إعادة تعيين.

1.2.3. مشروع فردي:

1.2.3.1. سجل التحويل على أساس CD4015 ، سجل التحويل الثنائي الثابت 4 بت ، التسلسلي ، الموازي.

1.2.3.2. سجل التحول على أساس CD4035 ، سجل التحول على 4 مراحل ، بالتوازي مع ، خارج التدريجي.

1.2.3.3. سجل التحول على أساس CD4014 ، سجل التحول ذو الـ 8 مراحل ، بالتوازي ، التسلسل التدريجي.

1.2.3.4. عداد مع إخراج LED CD4029 ، ثنائي عشري أعلى أسفل العداد.

1.2.3.5. مواجهة مع الإخراج إلى مؤشر 7 قطعة من خلال برنامج التشغيل.

1.2.3.6. أكثر تعقيدًا هو مزيج من سجلات الإزاحة CD4035 (متوازية ، متسلسلة للخارج) مع adder التسلسلي CD4038. انها تحتاج الى العاكس CD4069. قبل ذلك ، سوف أعرض المسلسل CD4032 الأفعى دون العاكس.

1.2.3.7. أكثر تعقيدًا هو مزيج من سجلات الإزاحة CD4014 (متوازية ، متسلسلة للخارج) مع adder التسلسلي CD4038. انها تحتاج الى العاكس CD4069.

الأسبوع 1. اليوم 3. FPGA ، تمارين مع الأزرار ، مفاتيح ، LED ، مؤشر سبعة قطعة

1.3.1. عنصر منطقي في منطق التوافقية هو إدخال من الأزرار ، الإخراج إلى المصابيح.

1.3.2. إخراج حرف واحد على مؤشر من سبعة قطاعات.

1.3.3. أبسط معدد هو إخراج الحروف اعتماداً على المفتاح المضغوط. التنفيذ باستخدام البنيات "؟" ، "إذا" ، "الحالة".

1.3.4. سجل التحول.

1.3.5. يتم عرض الكلمة على مؤشر سبعة قطاعات ديناميكي ثمانية بت باستخدام سجل التحول.

1.3.6. مشروع فردي ، ربما واجبات منزلية لعطلة نهاية الأسبوع:

1.3.6.1. الأشكال على مصفوفة LED.

1.3.6.2. ثعبان يعمل على مؤشر من سبعة قطاعات.

1.3.6.3. توليد إشارة تردد الصوت ، جهاز الصوت.

1.3.6.4. الإدخال من لوحة مفاتيح 16 زر.

1.3.6.5. قفل الكود - التعرف على تسلسل المفاتيح بواسطة جهاز الحالة.

1.3.6.6. التكامل مع جهاز استشعار المدى.

1.3.6.7. التكامل مع زاوية التشفير.

اليوم 4. FPGA ، إخراج الأشكال الهندسية إلى VGA

يوم 5. FPGA ، آلة الدولة لطيور غاضبة

الأسبوع 2. المعالج

اليوم 1. البرمجة في لغة التجميع.

اليوم 2. دورة واحدة schoolMIPS المعالج.

اليوم 3. تفاعل المعالج مع الانتهاء من الأشكال الهندسية على VGA.

اليوم 4. محاضرة عن الانقطاع وتعدد المهام. مشروع فردي - لعبة فيديو مبرمجة على المعالج مع إخراج إلى VGA.

يوم 5. محاضرة عن الناقل. منافسة المشاريع الفردية.

الأسبوع 3. الراديو القابلة للبرمجة. يتكون برنامج الكتلة من ثلاثة أجزاء رئيسية:

- أساسيات الديناميكا الكهربائية وانتشار الموجات الراديوية (الجزء النظري) ؛

- مبدأ تشغيل مسار الإرسال والاستقبال (النظرية والتطبيق) ؛

- أساسيات معالجة الإشارات الرقمية - الترشيح والتحليل الطيفي (النظرية والتطبيق).

اليوم 1. الأسس النظرية للديناميكا الكهربائية وانتشار الموجات الراديوية. المخطط الهيكلي لمسار الإرسال ، وظائف المكونات. إشارات (التوافقي ، مستطيلة). ممارسة إشارة باستخدام NI الفيس.

اليوم 2. نقل الإشارات إلى التردد العالي. مبرر رياضي لنقل التردد باستخدام Matlab. ممارسة عملية في نقل الترددات باستخدام NI Datex.

اليوم 3. تضخيم وانبعاث الإشارات. تدرب على استخدام NI Datex. مظاهرة اتجاهية الهوائيات.

يوم 4. تصفية الإشارة. تدرب على استخدام NI Datex. تصفية الإشارات الرقمية في ماتلاب

اليوم 5. نقل الإشارات إلى تردد منخفض. تدرب على استخدام NI Datex. تلخيص المواد المغطاة ، تلخيص.

حول بقية أيام المدرسة ، ستكون مزيد من التفاصيل في وظيفة منفصلة ، بعد مناقشة ذلك في اللجنة المنظمة للمدرسة الصيفية. إذا كنت ترغب في المشاركة في المدرسة الصيفية في MIET في زيلينوجراد كطالب أو مدرب ، فقد قام

المنظمون بنشر جهات الاتصال والتسجيل . إذا كنت طالبًا ، فمن المهم أن تكمل بحلول تموز (يوليو) جميع الوحدات الثلاثة لدورة Rosnanov عبر الإنترنت (

"من الترانزستور إلى الدائرة الصغيرة" و

"الجانب المنطقي للدوائر الرقمية" و

"الجانب المادي للدوائر الرقمية" ). ستكون الممارسة صعبة ، ولن نكون قادرين على التوقف عن تحديد الدورة التي تكون القيمة عند إدخال أو إخراج مشغل D. هذا لا يلائم رأسك على الفور ، ولكن إذا درست دورة عبر الإنترنت ، فسيكون ذلك أسهل بالنسبة لك.

بعض التفاصيل

حول الندوة في لاس فيجاس في 4 يونيو :

لا يحدث غالبًا أن ندوة هندسية ، تم تطويرها في الأصل لصالح روسيا ، وتم اختبارها في روسيا (بما في ذلك MIPT) وأوكرانيا وكازاخستان ، ثم تبدأ في لاس فيجاس ، في مؤتمر لأتمتة تصميم الإلكترونيات. في روسيا وأوكرانيا كان يطلق عليه ورشة MIPSfpga ، وفي مؤتمر أتمتة التصميم كان يطلق عليه يوم المطور المفتوح MIPS. تعال إلى 4 يونيو في أمباسي سويتس باي هيلتون كونفنشن سنتر في 3600 بارادايس رود ، لاس فيجاس ، وسوف تشارك في عرض أن الطلاب والمدرسين من جامعة موسكو الحكومية ، معهد موسكو للفيزياء والتكنولوجيا ، معهد موسكو للفيزياء الهندسية ، زيلينوغراد ميت ، سان بطرسبرج ، ITMO ، تومسك TSU ، كييف كي بي آي ، ألماتي ألما وجامعة نزارباييف جزئيا في أستانا.

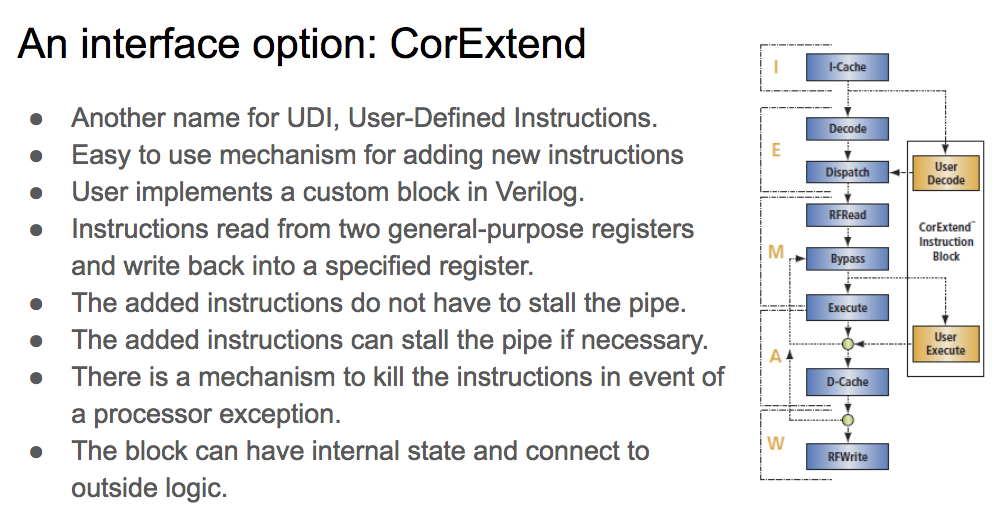

MIPSfpga هي حزمة تحتوي على جوهر المعالج في شفرة مصدر Verilog ، والتي يمكنك تغييرها ، وإضافة تعليمات جديدة ، ومراقبة تشغيل ذاكرة التخزين المؤقت وخطوط الأنابيب ، وبناء أنظمة متعددة المعالجات ، وتغيير البرامج والأجهزة في نفس الوقت ، إلخ. في الإصدار الجديد من الندوة ، ستقوم بإضافة المعالج إلى المعالج لتسريع خوارزميات الذكاء الاصطناعي.

بالإضافة إلى ذلك ، في الإصدار الجديد من الندوة سوف نعرض كيفية تكوين النواة من حزمة MIPS microAptiv UP وإدخالها في رابط MIPSfpga. عند التهيئة ، يمكنك إنشاء خيارات المعالج الغريبة ، على سبيل المثال معالج يحتوي على 16 مجموعة من 32 سجل. يمكنك تبديل هذه المجموعات تلقائيًا عند الدخول في مقاطعة ، وبالتالي تغيير السياق بسرعة دون حفظ / استعادة السياق من الذاكرة ، والذي يستغرق RTOS العادي حوالي ألف دورة.

MIPSfpga غير مخصص ليتم حقنه في كائن من الصفر المطلق. لاستخدامه المثمر ، يجب أن يعرف الطالب بالفعل أساسيات الدوائر الرقمية ، وأن يكون قادرًا على البرمجة في C والمجمع ، وكذلك تقديم مفاهيم الهندسة المعمارية - الناقل ، وتعارضات خطوط الأنابيب ، إلخ. هذا ما يتم دراسته في schoolMIPS ، والذي نستخدمه في Zelenograd.

فيما يلي شريحة حول آلية إضافة الإرشادات إلى معالج MIPS microAptiv UP:

في حلقة دراسية في لاس فيجاس في 4 يونيو ، وربما في مدرسة صيفية للمهندسين الإلكترونيين الشباب ، والتي ستعقد في الفترة من 8 إلى 26 يوليو في معهد ماساتشوستس للتكنولوجيا في زيلينوجراد ، ستساعدني ابنتي إليزابيث بانشول (إذا حصلت على تأشيرة في الوقت المحدد). نظرًا لأن إليزابيث شبه روسية وشبه روسية / أوكرانية ، فهي تتحدث الإنجليزية فقط. لذلك ، يمكن للمدربين الروس (الطلاب أو طلاب الدراسات العليا في معهد موسكو للفيزياء والتكنولوجيا ، وجامعة موسكو الحكومية ، وما إلى ذلك الذين هم على استعداد لمساعدتنا مع إليزابيث و MIET في إدارة المدرسة) أن يتعلموا لهجتها الإنجليزية الصحيحة ، وهي منهم - أساسيات اللغة الروسية. بالإضافة إلى دراسة Verilog و MIPS والهندسة المعمارية والبنية الدقيقة وتنظيم DMA في الذاكرة عند عرضها على شاشة رسم:

نحن في انتظارك في جميع الندوات ، وكذلك في اللجان لإنشاء برامجهم!