استغرق الإفطار مع تشارلز ويثرلي ، مؤلف كتاب عبادة Etudes للمبرمجين ، أربع ساعات. في النهاية ، سألتنا النادلة من مطعم في بالو ألتو ، قائلة إن هناك طابورًا طويلًا في المطعم ، وكنا نجلس هنا من الساعة الثامنة صباحًا. خلال هذا الوقت ، ناقشنا الكثير من الأشياء المثيرة للاهتمام: عمل تشارلز في مختبر ليفرمور وأوراكل ، البرمجة الموجهة للكائنات والوظيفية ، المجمعين ولغات وصف الأجهزة ، إشارات مرجعية إلى المعالجات ، عدم كفاءة الشبكة العصبية ، زيارة Prolog المنسية ، زيارة تشارلز إلى روسيا ، معالجة النصوص مع آلة حكومية في coprocessor الأجهزة وإنشاء ألعاب الفيديو على FPGAs من قبل أطفال المدارس.

إن محتوى أربع ساعات من كتاب Charles Weatherly يكفي لخمسين مقالة عن Habré ، وبالتالي سأدرج الموضوعات بشكل رئيسي ، وبعد ذلك سأقدم بعض التفاصيل حول ثلاثة منها:

- وجوه المنحى والبرمجة الوظيفية. مهمة واحدة ، والقيم وظيفة ، والتخلص من الطفرات ، والتخلص من التوقيت.

- هياكل البيانات وخوارزميات المترجم. الكثير من SSA وكتاب التحسينات. بوب مورغان (البوصلة) بناء الأمثل المجمعين. ناقلات المجمعين وراندي ألين (زميلي الموجي وزميل تشارلز عن الشركات الأخرى).

- تطور المحلل اللغوي Yacc ، اللغة الداخلية للغة Ada (DIANA) ، الواجهة الأمامية لـ VHDL في سينوبسيس.

- قواعد اللغة العزيزة وغير الناجحة ، في رأيي ، استخدامها في دليل التدريب MIPT على نظرية تنفيذ لغات البرمجة (TRNP).

- لغة البرمجة JOVIAL وتوحيد آدا. لغة IDL.

- البرمجة في مختبر الحوسبة ليفرمور للفيزيائيين والكيميائيين على CDC 7600 و Cray-1. تعد ليفرمور فورتران امتدادًا لسيارة فورتران 77 ذات الهياكل وتخصيص الذاكرة الديناميكي. استخدام الميكروفيش ، بما في ذلك البحث التلقائي وإنتاج الرسوم المتحركة. هاري نيلسون وكيف دخل مكعب روبيك إلى المعمل قبل أن يصبح معروفًا.

- استنساخ السوفياتي كراي -1 إلكترونيات SS BIS. المترجم Fortran في IPM والمترجم C الذي عملنا عليه في MIPT.

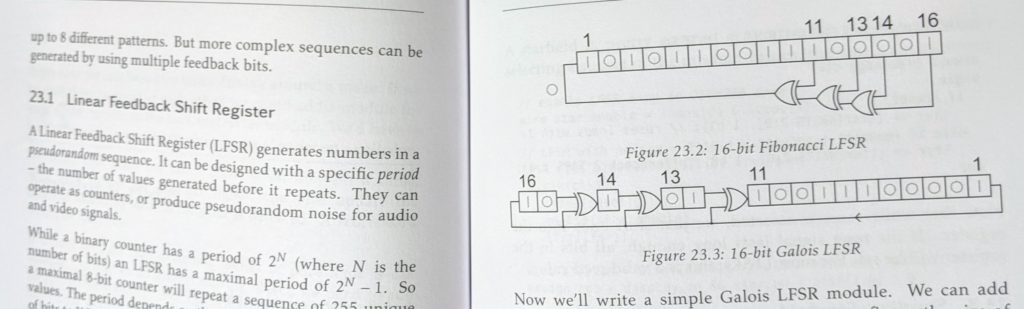

- عكس الهندسة مولد رقم عشوائي في سينوبسيس VCS. مولد متطابق مع سجل التحول. LSFR.

- عدم كفاءة الشبكة العصبية ولغة Prolog المنسية.

- تطبيق الأساليب من Prolog لتحليل ثابت لنص البرنامج.

- بما في ذلك تحليل رمز المعالج المكتوب في فيريلوج أو VHDL من أجل العثور على العلامات في ذلك. إشارة مرجعية منتشرة في أجزاء مختلفة من وصف المعالج على مستوى نقل السجل. البحث عن رمز "متكرر" يقوم بشيء خارج المواصفات. على سبيل المثال ، آلة الحالة المحدودة التي تنتظر عبارة رئيسية ، نص في السجلات مرئية للمبرمج ، وبعد ذلك ينتقل المعالج إلى الوضع المميز.

- طرق تحليل الشفرة المختلطة - التنفيذ الديناميكي مع الاستقصاء الثابت اللاحق لمساحة الحالة من نقطة تنفيذ معينة.

- قائمة حكم من معهد ماساتشوستس للتكنولوجيا.

- يستخدم معظم المبرمجين في الحياة خمس خوارزميات فقط - فرز سريع ، والبحث الثنائي ، والتجزئة ، وإدراج القائمة ، وشيء آخر (الإدراج الثنائي لشجرة AVL؟).

- تاريخ يونكس تروف في بيل مختبرات.

- عمل تشارلز وازيريل في أوراكل على SQL.

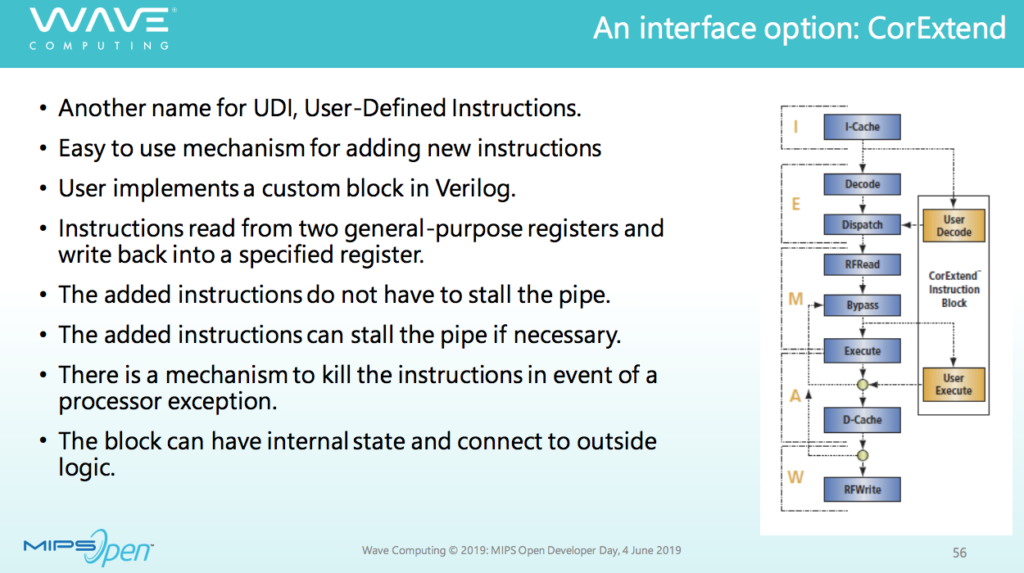

- مثال جيد على استخدام معالج مساعد للجهاز لـ MIPS CorExtend / UDI هو "تعليمات معرفة من قبل المستخدم". إضافة تعليمات إلى المعالج لتحليل معجمي سريع ، مع وجود جهاز الحالة داخل المعالج الثانوي والحفاظ على الحالة بين التعليمات الفردية. خلفية منذ IBM / 360 ترجمة الاختبار و CDC STAR.

- استخدام معالج مساعد للجهاز لتنظيف دفق البيانات مسبقًا قبل تطبيق خوارزميات تعلم الآلة عليه.

- لعبة روغ ، العلمية الأمريكية في الولايات والاتحاد السوفياتي.

- المدرسة الصيفية للمبرمجين الصغار في نوفوسيبيرسك والبعوض فيها (حسب ذكرياتي وقصص زملائي تشارلز ويثرلي)

- كيف قضى تشارلز 36 ساعة في موسكو وأسبوعين في سان بطرسبرغ. المحبسة. في جامعات سان بطرسبرج ، لم يلقي محاضرات.

- اقترح تشارلز أن يذهب إلى مدرسة صيفية في MIET / Zelenograd في يوليو أو في مكان آخر في الخريف (جامعة موسكو الحكومية؟ MIPT؟ ITMO؟).

- التعليم لأطفال المدارس والطلاب الأصغر سنا. الحاجة إلى الخروج من القالب (على سبيل المثال ، البرمجة المتسلسلة) وتعلم Verilog على FPGA كطريقة واحدة للخروج من هذا القالب.

- استخدام الدوائر الصغيرة مع درجة صغيرة من التكامل قبل تمارين FPGA ، بحيث يفهم تلميذ أو طالب بشكل حدسي أن كود Verilog هو وصف لدائرة إلكترونية ، وليس برنامجًا (سلسلة من التعليمات).

- ومن الأمثلة على RTL على FPGA للمدرسة الصيفية في MIET / Zelenograd في يوليو / تموز ، آلة حكومية محدودة للتعلم الذاتي تقوم بحساب اتجاهات الخصم في لعبة "مقص الأوراق الحجرية".

- مثال آخر هو المنافسة بين آلات الحالة المحدودة (الحيوانات) التي تنقل اللاعب إلى هدف على الخريطة (الكرة الأرضية). الكائنات الموجودة على الخريطة لها "رائحة" - إيجابية (طعام) أو سلبية (كهرباء يمكن أن تضرب). تصميم بطاقة في FPGA ، إخراج وشغل لاعب على VGA باستخدام وحدة توليد المسح الضوئي.

هنا درسنا النزاعات الأخيرة حول حبري حول OOP. يقوم Charles بحملات من أجل كل من OOP والبرمجة الوظيفية ، عند الاقتضاء. لقد عرضت على تشارلز

مثالاً رأيته في مشروعين من

تصميم فصولي غير ناجح لتمثيل عقد شجرة تحليل وتحسينات على هذه الشجرة ، وبعد ذلك قال تشارلز إنه بالطبع ، لا ينبغي أن تنتشر خوارزميات تحويل الأشجار في فصول صغيرة بهذه الطريقة ، ولكن بدلاً من ذلك ، يجب أن تكون شجرة التحليل رمي بسرعة في الرسم البياني تدفق التحكم ، والتي لاستخدام تحويلات الجدول يحركها على أساس مهمة واحدة ثابتة ، مع بعض الاستثناءات القليلة. قام تشارلز بتنوير لي حول اتجاه موشنك وبوب مورغان وراندي ألين:

ثم أخبرت تشارلز أنه في اليوم التالي غدًا ، سنعقد

ندوة في لاس فيغاس في مؤتمر لأتمتة تصميم الإلكترونيات ، وكنت بحاجة لنصيحته بشأن مثال جيد على معالج مشارك يستند إلى بروتوكول CorExtend / UDI - تعليمات محددة من قبل المستخدم. يستخدم هذا البروتوكول في النوى MIPS. يسمح لك CorExtend / UDI بتضمين كتلة في المعالج تقوم بفك تشفير وتنفيذ التعليمات الإضافية للنظام الرئيسي للتعليمات التي يمكن أن يحددها مصمم النظام على شريحة. يمكن تصنيع الكتلة وتصبح جزءًا من الدائرة الصغيرة أو تكوينها في FPGA / FPGA.

تعليمات إضافية تتحرك على طول خط أنابيب المعالج جنبا إلى جنب مع الرئيسية. تلقي البيانات من السجلات العامة مرئية للمبرمج ويمكن إرجاع النتيجة إلى السجل. يمكن لهذه الإرشادات أيضًا حفظ بعض الحالات في المعالج الثانوي. يمكن قتلهم عن طريق استثناءات في حالة حدوث استثناء ، على سبيل المثال ، في خط الأنابيب باتباع هذه التعليمات:

في اليوم التالي غدًا ، في

عرض تقديمي في الندوة ، سأستخدم مثالًا بتعليم الإلتفاف البسيط لشبكة عصبية. لكن التسارع الذي تحقق في هذه الحالة ليس مثيرًا للإعجاب - مرتين فقط. هل من الممكن تقديم مثال أفضل؟

توصل تشارلز على الفور إلى مثال أفضل بكثير: تحليل معجم الأجهزة. يمكن وضع آلة الحالة في المعالج الثانوي ، والتي ستحدد الأرقام والمعرفات والتعليقات في دفق النص. سيتم حفظه عن طريق تخزين الحالة بين الأوامر الفردية التي تنقل النص من السجلات إلى الجهاز. سيتم أيضًا إرجاع نتيجة التحليل الحالي (النص المرمز) إلى السجل.

أخبرني تشارلز أيضًا قصة تعليمات تحليل النص منذ أن قام IBM / 360 بترجمة الاختبار و CDC STAR. أخبرني أيضًا أن مثل هذا المعالج يمكن استخدامه للتعلم الآلي ، لتنظيف دفق البيانات مسبقًا قبل تطبيق خوارزميات تعلم الآلة عليه.

ثم أخبرت تشارلز ساغا كيف قامت مجموعة من المهندسين والمدرسين بترجمة وتنفيذ

كتاب مدرسي لديفيد هاريس وسارة هاريس في جامعات روسية مختلفة إلى

"الدوائر الرقمية وهندسة الكمبيوتر" (انظر المنشورات على موقع Habr.

1 ،

2 ،

3). الآن ، مع الجهود المشتركة التي بذلتها MIET و RUSNANO ومعلمي MEPhI والجامعات الأخرى ، نخطط لإنشاء مدرسة صيفية في MIET حيث يقوم أطفال المدارس المتقدمون

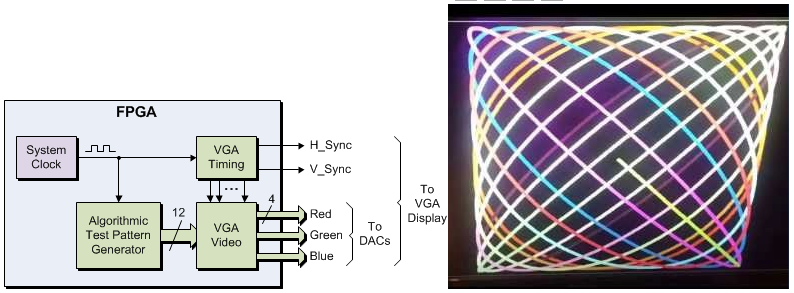

بعرض ألعاب فيديو على FPGA مع الإخراج إلى شاشة بيانية (قسم

بين الفيزياء والبرمجة ). لهذا الغرض ، يتم استخدام أفكار من كتاب Designing Video Game Hardware in Verilog لـ Steven Hugg ، 15 ديسمبر 2018:

يمكن تطوير الألعاب في شكل أجهزة حالة محدودة للأجهزة بحتة ، أو في مجموعة من رسومات الأجهزة على FPGAs مع برامج على schoolMIPS بسيطة المعالج ، والتي تم وصفها في

منشورات Stanislav Zhelnio on Habr و

wiki على schoolMIPS على GitHub . على FPGAs ، يمكنك ببساطة

إجراء مسح ضوئي لـ VGA وعرض بطاقة من الذاكرة وتحريك العفاريت بأشكال:

اقترح تشارلز ، بالإضافة إلى الألعاب مع الدبابات والأجناس ، إجراء مسابقة للأوتوماتا المحدودة (الحيوانات) التي تنقل اللاعب إلى الهدف على الخريطة (الكرة الأرضية). الكائنات الموجودة على الخريطة لها "رائحة" - إيجابية (طعام) أو سلبية (كهرباء يمكن أن تضرب). يمكن للتلاميذ أن يكتبوا آلات محدودة على veril يرون البيئة ، ويدمجونها في شفرة ترسم رسومات وتدعم الخريطة ، ثم تتنافس مع من هو أفضل:

لإنشاء عناصر السلوك العشوائي الزائف ، يمكنك استخدام كتل الأجهزة LFSR:

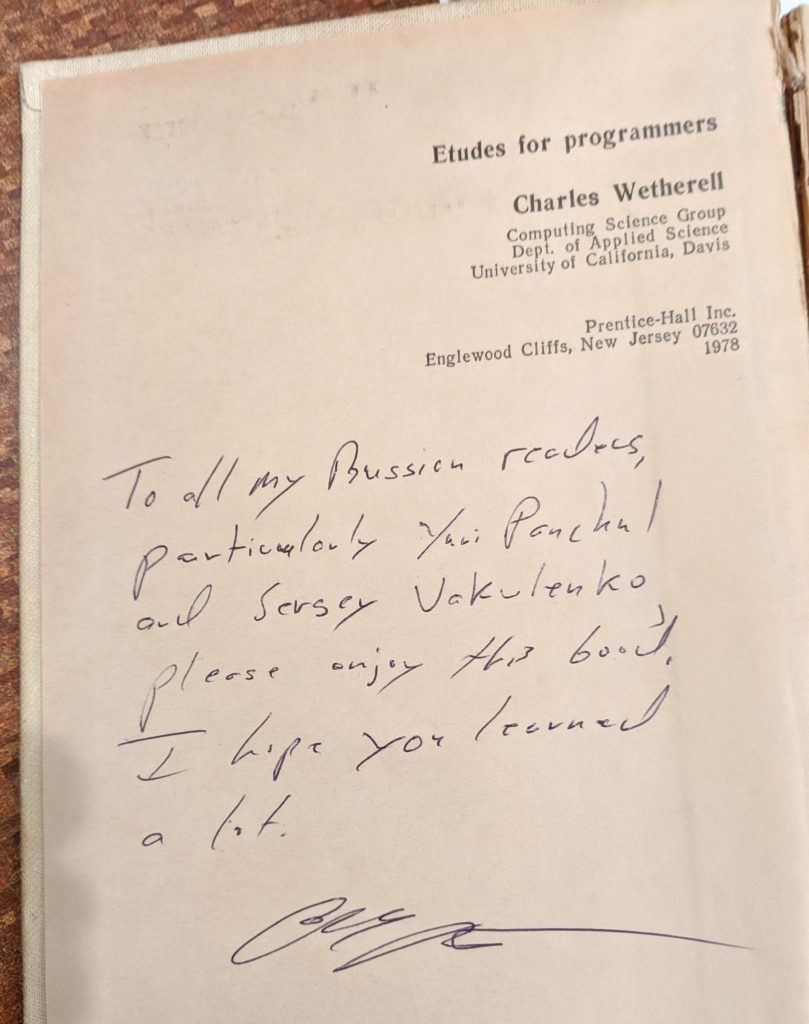

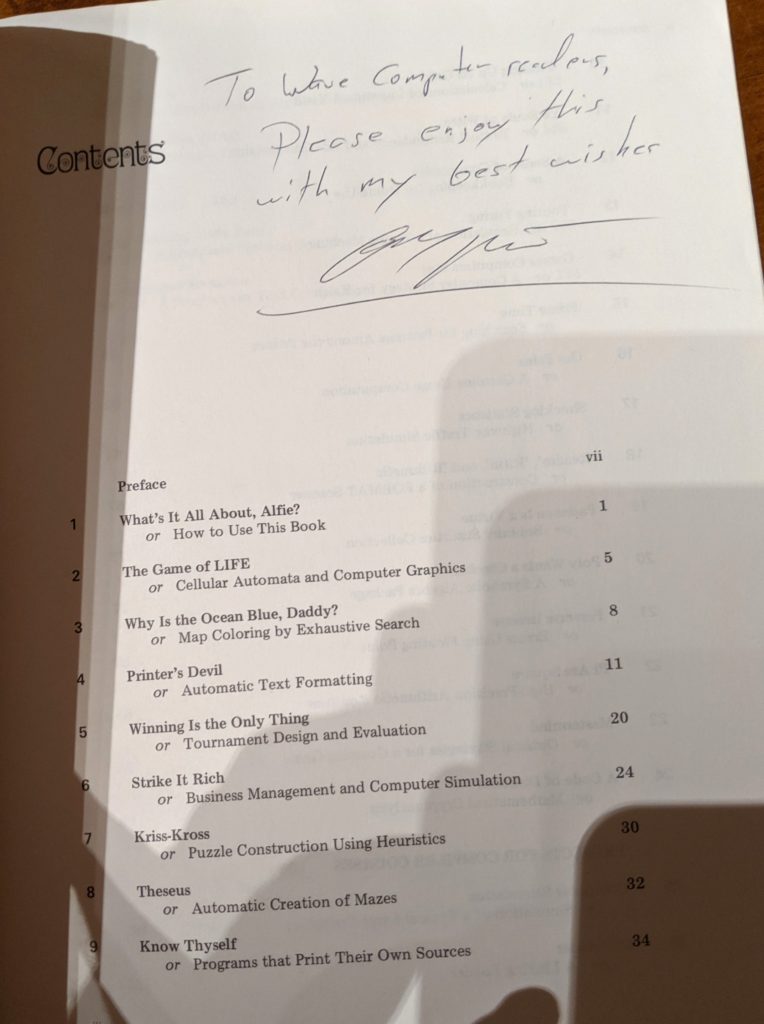

في النهاية ، ترك تشارلز توقيعين - للقراء الروس (استعارت كتابًا روسيًا من

سيرجي فاكولينكو ) والقراء في شركتنا Wave Computing ، الذين استعارت كتابًا أصليًا من مكتبته الداخلية ، باللغة الإنجليزية: