لذلك ، في

المقالة الأولى من الدورة قيل إنه من الأفضل استخدام نظام المعالج للتحكم في أجهزتنا التي تم تنفيذها باستخدام FPGAs لمجمع Redd ، وبعدها تم خلال المادتين الأولى والثانية عرض كيفية عمل هذا النظام. حسنًا ، لقد تم ذلك ، حتى يمكننا اختيار بعض الألبومات الجاهزة من القائمة لإدراجها فيها ، لكن الهدف النهائي هو إدارة الألبومات المخصصة الخاصة بنا. لقد حان الوقت للنظر في كيفية تضمين نواة تعسفية في نظام المعالج.

جميع مقالات الدورة:

تطوير أبسط "البرامج الثابتة" لأجهزة FPGA المثبتة في Redd ، وتصحيح الأخطاء باستخدام اختبار الذاكرة كمثالتطوير أبسط "البرامج الثابتة" لأجهزة FPGA المثبتة في Redd. الجزء 2. رمز البرنامجلفهم نظرية اليوم ، يجب أن تجد وتنزيل وثيقة

مواصفات Avalon Interface ، لأن ناقل

Avalon هو الناقل الأساسي لنظام NIOS II. سأشير إلى الأقسام والجداول والأرقام الخاصة بمراجعة وثيقة 26 سبتمبر 2018.

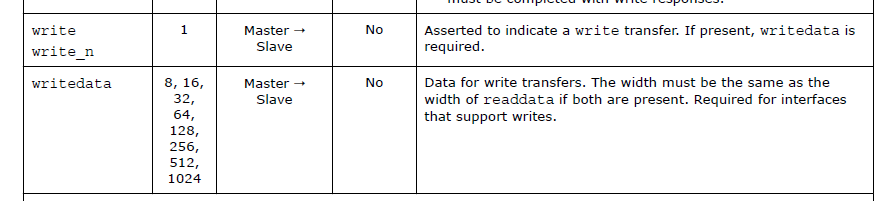

نفتح القسم 3 المكرس لواجهات الذاكرة المعينة ، أو بالأحرى - 3.2. يسرد الجدول 9 إشارات الحافلة. يرجى ملاحظة أن كل هذه الإشارات اختيارية. لم أجد إشارة واحدة تحمل "نعم" في العمود "مطلوب". قد لا نعيد توجيه هذه الإشارة أو تلك إلى جهازنا. لذلك ، في أبسط الحالات ، يكون الحافلة بسيطًا للغاية في التنفيذ. تبدو بداية الجدول كما يلي:

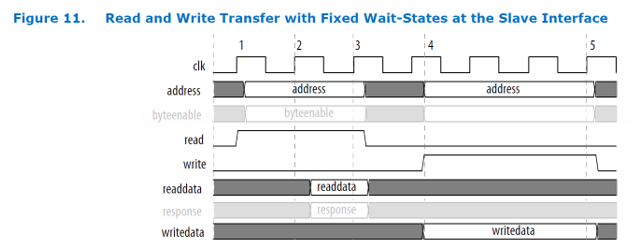

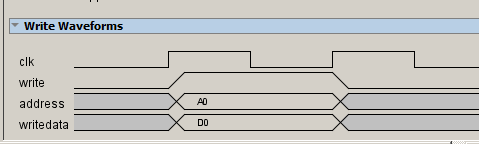

كما ترون ، فإن جميع الإشارات موصوفة جيدًا (باستثناء أن ذلك يتم باللغة الإنجليزية). فيما يلي المخططات الزمنية لمختلف الحالات. القضية الأكثر أبسطًا لا تثير أي أسئلة. سأخذ الآن المخطط الزمني من المستند وأغطي بعض الأسطر بملء شفاف (كلها اختيارية ، ولدينا الحق في استبعاد أي من الاعتبارات).

مخيف؟ ولكن كل شيء بسيط: لقد تم إعطاءنا العنوان وقوية

القراءة ، يجب علينا تعيين البيانات على ناقل readdata. والعكس بالعكس: لقد حصلنا على العنوان والبيانات الموجودة على حافلة writedata وحركة الكتابة القوية ، وعلينا أن نجمع البيانات. إنه ليس مخيفًا على الإطلاق ، إنه ناقل متزامن نموذجي.

هناك حاجة إلى خطوط byteenable السرية للحالة عندما لا يكون الوصول إلى الذاكرة كلمات 32 بت. هذا مهم للغاية عندما نصمم حبات عالمية. لكن عندما نصمم نواة ليوم واحد ، نكتب ببساطة في المستند عن هذا النواة (أنا خصم للعلامة في رأسي ، ولكن يمكن لأي شخص أن يقصرها على ذلك) نحتاج إلى استخدام كلمات ذات 32 بت وهذا كل شيء. حسنًا ، وإشارة

الاستجابة ، إنها خاصة جدًا ولا تهمنا من حيث المبدأ.

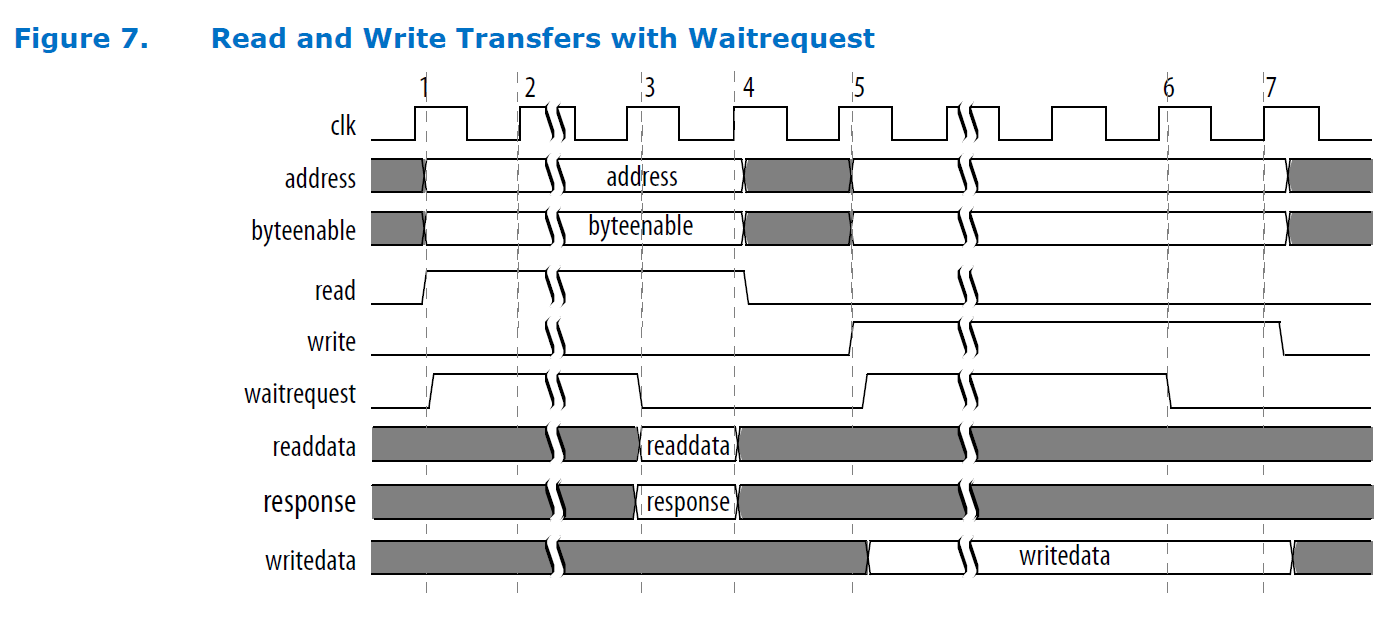

من المهم في بعض الأحيان أنه عندما لا تكون المعدات جاهزة ، فمن الممكن تأخير تشغيل الحافلة لعدة دورات على مدار الساعة. في هذه الحالة ، يجب إضافة إشارة

WaitRequest . سيتغير مخطط التوقيت كما يلي:

بينما

يكون WaitRequest معبأ ، يعرف المعالج أن الجهاز لدينا مشغول. كن حذرًا إذا لم تتم إعادة تعيين هذه الإشارة ، فسيقوم النظام بأكمله "بالتجمد" عند المعالجة ، لذلك يمكن فقط لإعادة تشغيل FPGA إعادة تعيينها. JTAG معلقة مع النظام. آخر مرة لاحظت فيها هذه الظاهرة كانت في إعداد هذه المقالة ، لذلك لا تزال الذكريات حية.

كذلك في مستند الشركة ، يتم النظر في الحالات الأكثر إنتاجية لأنابيب البيانات والمعاملات الدفعية ، لكن مهمة المقال ليست في النظر في جميع الخيارات الممكنة ، ولكن لإظهار القارئ طريقة للعمل ، مع التأكيد على أن كل هذا ليس مخيفًا على الإطلاق ، لذلك سنقتصر على هذين الخيارين البسيطين.

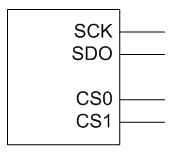

دعونا تصميم بعض الأجهزة البسيطة التي ستصبح غير متوفرة بشكل دوري في الحافلة. أول ما يتبادر إلى الذهن هو الواجهة التسلسلية. أثناء انتقال الإرسال ، سنجعل النظام ينتظر. وفي الحياة ، أنصحك بشدة بعدم القيام بذلك: سيتوقف المعالج حتى نهاية المعاملة المزدحمة ، لكن هذه هي الحالة المثالية لمقال ، حيث أن كود التنفيذ سيكون مفهومًا وليس مرهقًا جدًا. بشكل عام ، سنقوم بإنشاء جهاز إرسال تسلسلي يمكنه إرسال إشارات اختيار البيانات والرقاقة إلى جهازين.

لنبدأ بأبسط خيار للإطارات. لنقم بإنشاء منفذ إخراج متوازي ، والذي يشكل إشارات اختيار البلورات.

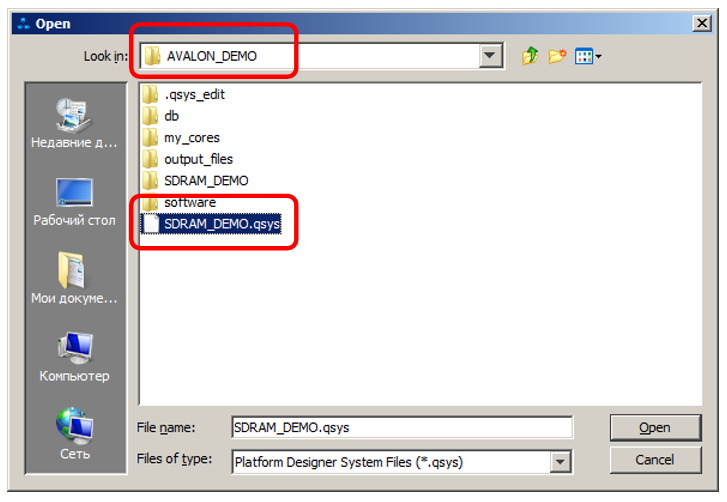

لهذا ، سوف آخذ المشروع الذي تم الحصول عليه في المقالة السابقة ، ولكن من أجل تجنب الالتباس ، سوف أضعه في دليل AVALON_DEMO. لن أغير أسماء الملفات الأخرى. في هذا الدليل ، قم بإنشاء دليل

my_cores . اسم الدليل يمكن أن يكون أي شيء. سنقوم بتخزين النوى لدينا في ذلك. صحيح ، اليوم سيكون واحد. قم

بإنشاء ملف

CrazySerial.sv بالمحتويات التالية:

module CrazySerial ( input clk, input reset, input [1:0] address, input write, input [31:0] writedata, output reg [1:0] cs ); always @(posedge clk, posedge reset) begin if (reset == 1) begin cs <= 0; end else begin if (write) case (address) 2'h00: cs <= writedata [1:0]; default:; endcase end end endmodule

هيا بنا بادئ ذي بدء ، خطوط واجهة.

CLK وإعادة

تعيين هي خطوط الساعة وإعادة تعيين. يتم أخذ أسماء

العناوين وخطوط الكتابة والكتابة من الجدول مع قائمة إشارات وثيقة

واجهات الذاكرة المعينة .

في الواقع ، أنا يمكن أن تعطي أي أسماء. سيتم ربط الخطوط المنطقية مع الخطوط المادية في وقت لاحق. لكن إذا أعطيت الأسماء ، كما في الجدول ، فإن بيئة التطوير ستربطها بنفسها. لذلك ، من الأفضل أن تأخذ الأسماء من الجدول.

حسنًا ،

cs هي خطوط التحديد البلورية التي ستخرج من الشريحة.

التنفيذ بحد ذاته تافه. عند إعادة التعيين ، يتم إخراج النواتج. وهكذا - في كل قياس نتحقق مما إذا كانت هناك إشارة

للكتابة . إذا كان هناك عنوان يساوي الصفر ، فانقر فوق البيانات. بالطبع ، سيكون من الممكن إضافة وحدة فك ترميز هنا ، والتي ستمنع اختيار جهازين في وقت واحد ، ولكن ما هو جيد في الحياة سوف يثقل كاهل المقالة. توفر المقالة فقط الخطوات الأكثر أهمية ، ومع ذلك ، تجدر الإشارة إلى أنه في الحياة يمكن القيام بكل شيء أكثر تعقيدًا.

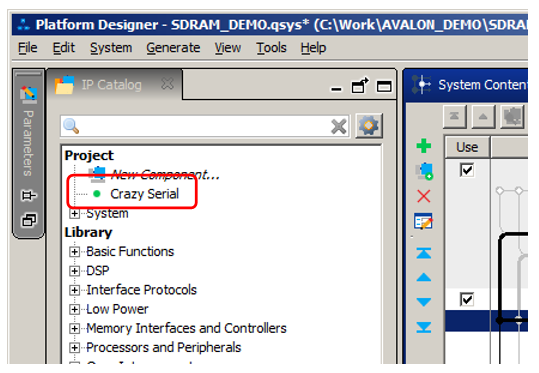

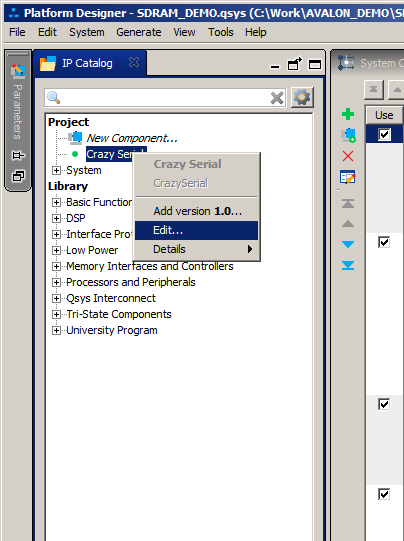

غرامة. نحن على استعداد لإدخال هذا الرمز في نظام المعالج. نذهب إلى "

مصمم النظام الأساسي" ، وحدد كملف إدخال النظام الذي أنشأناه في التجارب السابقة:

نلفت الانتباه إلى عنصر "

المكون الجديد" في الزاوية اليسرى العليا:

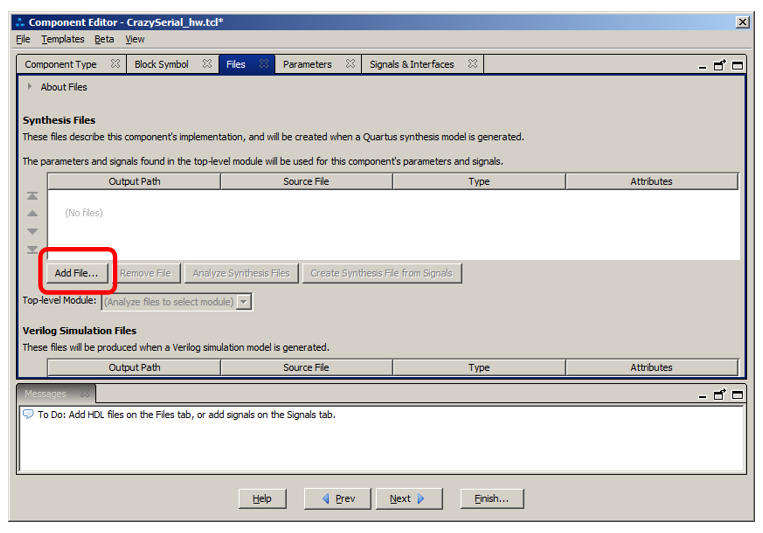

لإضافة المكون الخاص بك ، انقر فوق هذا العنصر. في مربع الحوار الذي يفتح ، املأ الحقول. وللمقال ، املأ اسم المكون فقط:

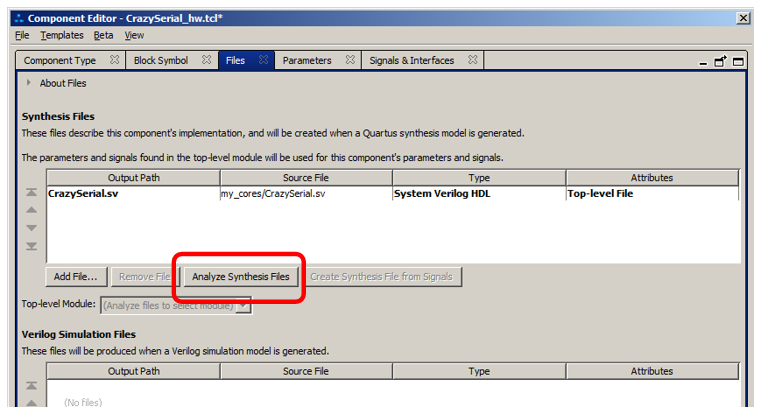

انتقل الآن إلى علامة التبويب "

الملفات" وانقر فوق "

إضافة ملف" :

أضف الملف الذي تم إنشاؤه مسبقًا ، حدده في القائمة وانقر فوق

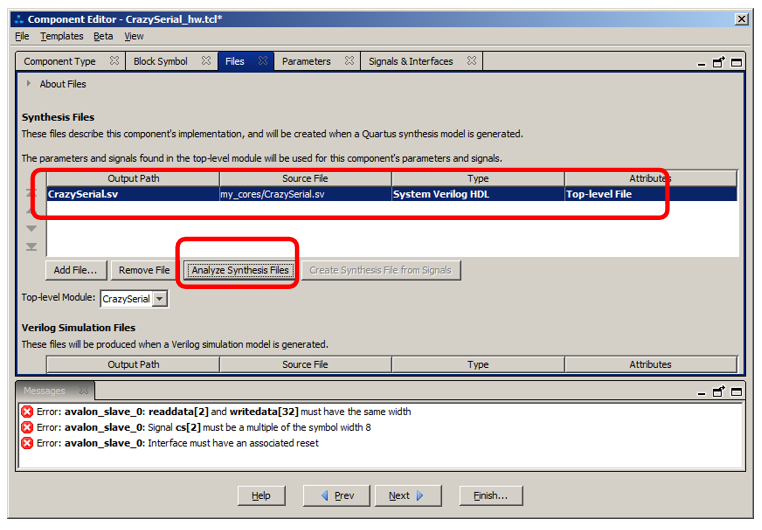

تحليل ملف التجميع :

لا توجد أخطاء في تحليل

SystemVerilog ، ولكن هناك العديد من الأخطاء المفاهيمية. سببها حقيقة أن بعض الخطوط كانت مرتبطة بشكل غير صحيح بواسطة بيئة التطوير. نذهب إلى علامة التبويب

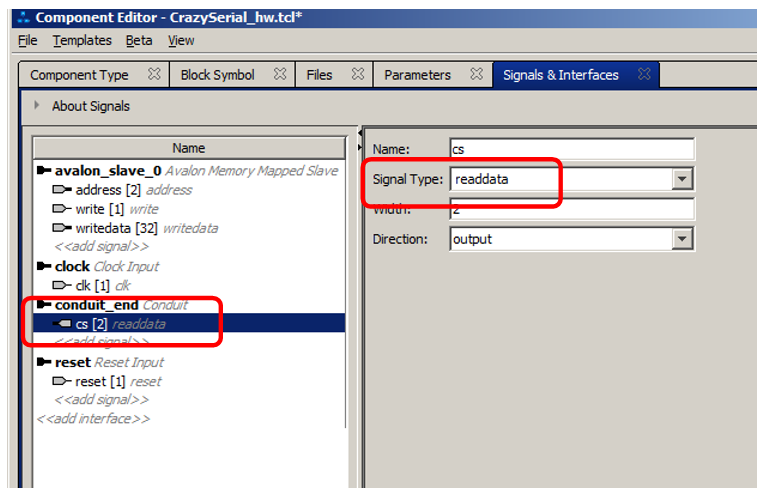

Signal & Interfaces وننتبه هنا:

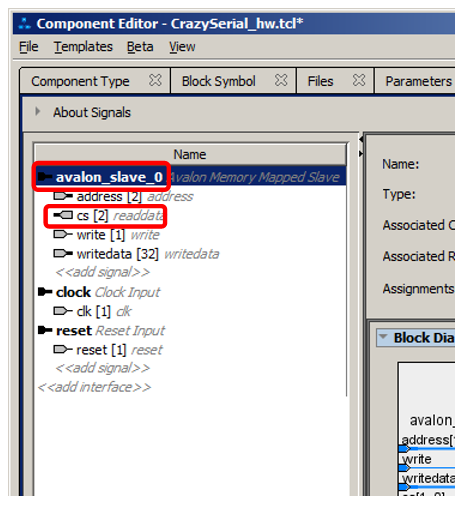

تم تعيين خطوط

cs بشكل غير صحيح إلى واجهة

avalon_slave0 ، إشارة

readdata . ولكن بعد ذلك تم التعرف على جميع الأسطر الأخرى بشكل صحيح ، وذلك بفضل حقيقة أننا قدمنا لهم أسماء من جدول المستندات. ولكن ماذا تفعل مع خطوط المشكلة؟ يجب تعيينهم إلى واجهة مثل

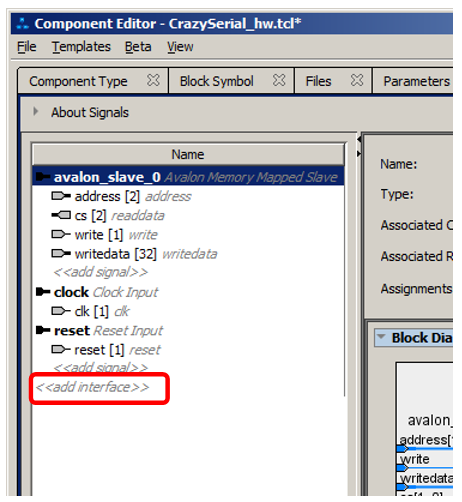

القناة . للقيام بذلك ، انقر فوق العنصر "إضافة واجهة"

في القائمة المنسدلة ، حدد

القناة :

نحصل على واجهة جديدة:

إذا رغبت في ذلك ، يمكن إعادة تسميته. صحيح ، سيكون هذا ضروريًا بالتأكيد إذا أردنا إنشاء عدة واجهات خارجية. كجزء من المقالة ،

سنتركها اسم

conduit_end . نحن الآن

نربط خط

cs بالماوس واسحبه في هذه الواجهة. يجب أن نتمكن من رمي إشارة أسفل خط

المواجهة ، ثم سيتم السماح لنا بذلك. في أماكن أخرى ، سيظهر المؤشر كدائرة متقاطعة. في النهاية ، يجب أن يكون لدينا هذا:

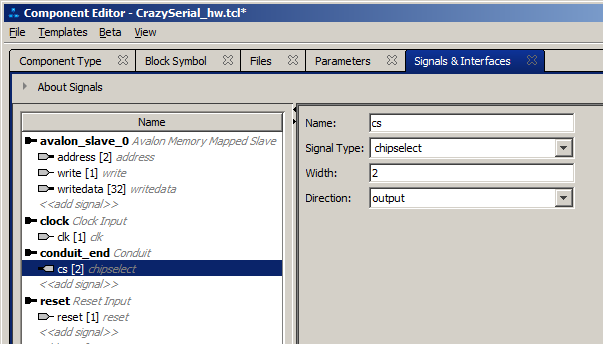

استبدل نوع الإشارة

بقراءة البيانات ، على سبيل المثال ،

chipselect . الصورة النهائية:

لكن الأخطاء بقيت. لم

يتم تعيين إشارة

avalon الحافلة . نختار

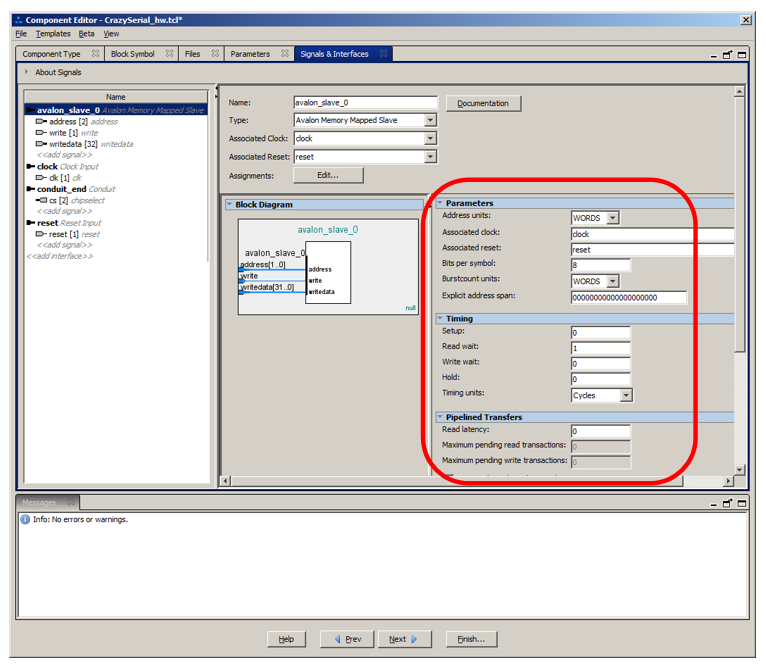

avalon_slave_0 من القائمة وننظر في خصائصه.

استبدال

لا شيء مع

إعادة تعيين . في الوقت نفسه ، سوف ندرس خصائص الواجهة الأخرى.

يمكن ملاحظة أن المعالجة بالكلمات. حسنًا ، تم تكوين عدد من الأشياء الأخرى من الوثائق هنا. سيتم رسم المخططات الزمنية التي يتم الحصول عليها في هذه الحالة في أسفل الخصائص:

في الواقع ، لا توجد المزيد من الأخطاء. يمكنك النقر فوق "

إنهاء" . ظهرت الوحدة النمطية التي تم إنشاؤها في شجرة الجهاز:

إضافته إلى نظام المعالج ، توصيل إشارات الساعة وإعادة تعيين. نقوم بتوصيل ناقل

البيانات بمعالج

Data Master . انقر نقرًا مزدوجًا فوق

Conduit_end وتعطي الإشارة الخارجية اسمًا ، على سبيل المثال ،

خطوطًا . اتضح بطريقة ما مثل هذا:

من المهم ألا ننسى أنه نظرًا لأننا أضفنا كتلة إلى النظام ، يجب أن نتأكد من أنه لا يتعارض مع أي شخص في مساحة العنوان. في هذه الحالة بالذات ، لا يوجد تعارض في الشكل ، ولكن على أي حال ،

سأختار عنصر القائمة

النظام> تعيين العناوين الأساسية .

هذا كل شيء. يتم إنشاء الكتلة وتهيئتها وإضافتها إلى النظام. انقر فوق الزر

إنشاء HDL ، ثم

إنهاء .

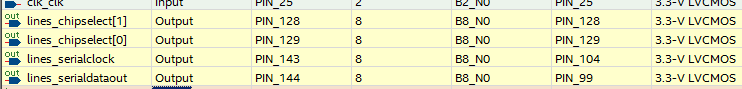

نقوم بعمل مسودة تقريبية للمشروع ، وبعد ذلك نذهب إلى

Pin Planner ونخصص الأرجل. اتضح مثل هذا:

الذي يتوافق مع جهات الاتصال B22 و C22 من موصل واجهة.

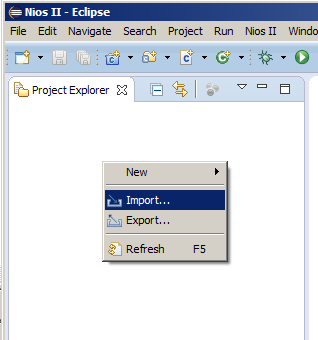

نجعل التجميع النهائي ، تحميل نظام المعالج في FPGA. نحن الآن بحاجة إلى تحسين رمز البرنامج. إطلاق الكسوف.

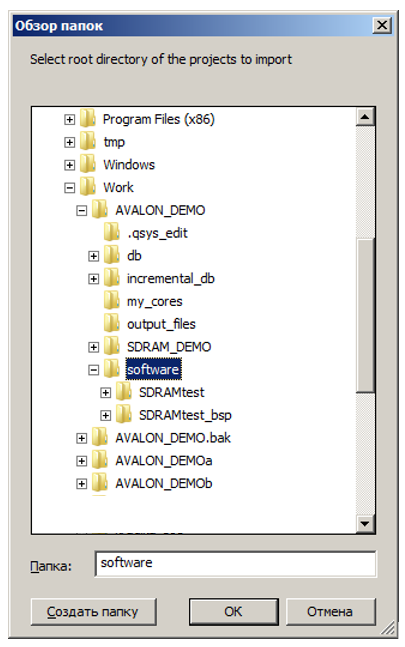

اسمحوا لي أن أذكرك بأنني أعمل حاليًا مع مشروع موجود في دليل مختلف بالنسبة إلى عملي الأخير في Redd. حتى لا أكون مرتبكًا ، سأحذف المشروعات القديمة من الشجرة (ولكن فقط من الشجرة ، دون مسح الملفات نفسها).

بعد ذلك ، انقر فوق زر الماوس الأيمن على شجرة فارغة وحدد

استيراد من القائمة:

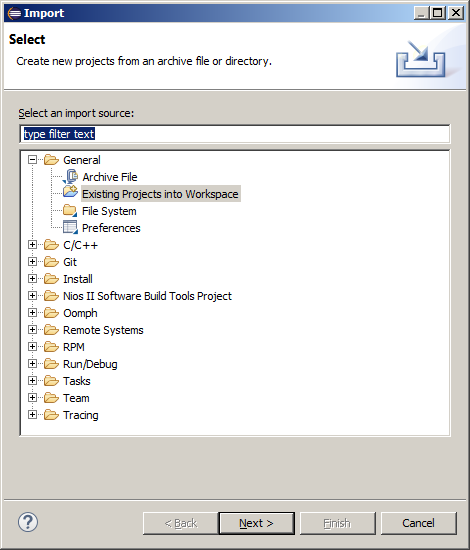

التالي -

عام-> مشروع موجود في مساحة العمل :

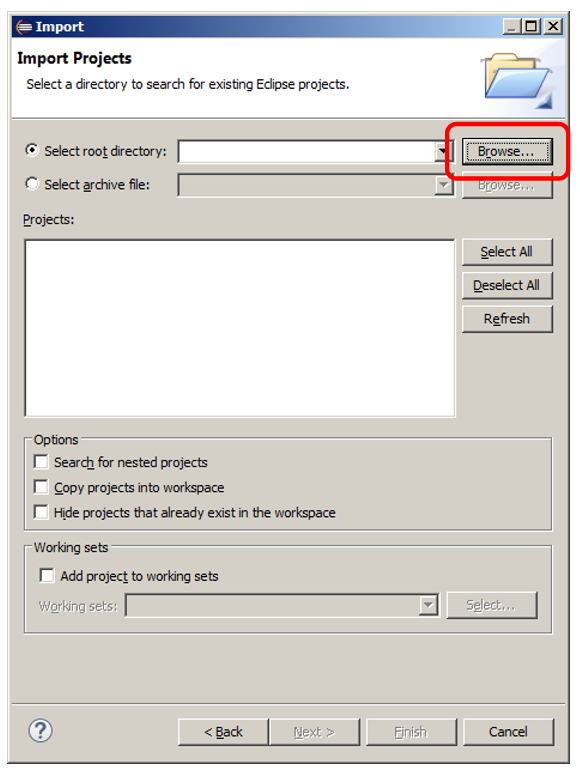

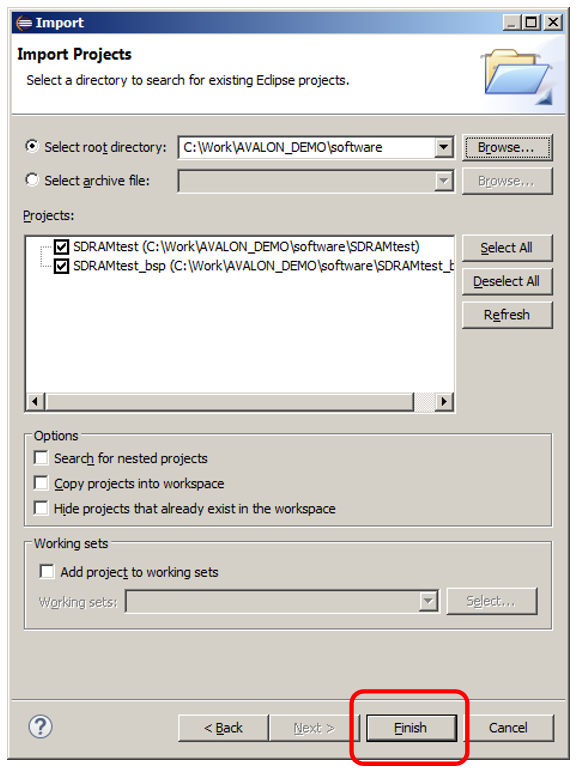

وحدد فقط الدليل الذي يتم تخزين ملفات المشروع فيه:

كلا المشروعين الموروثين من التجارب السابقة سوف يتصلان ببيئة التطوير.

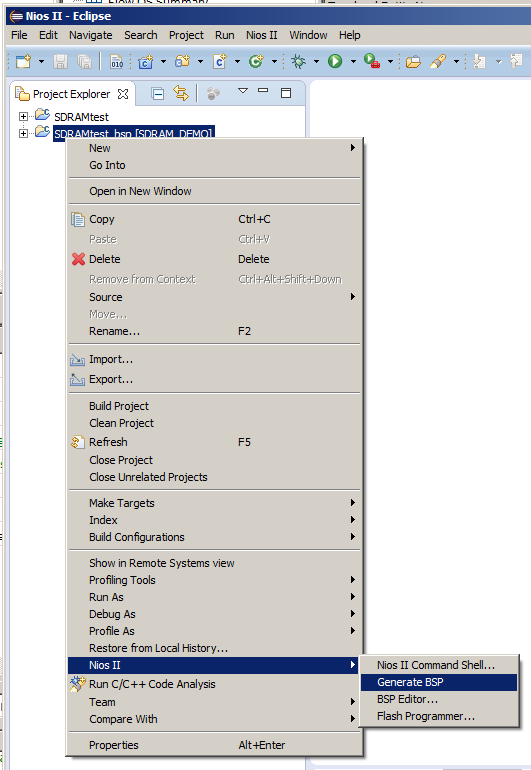

سأسلط الضوء على العنصر التالي في الإطار:

في كل مرة بعد تغيير تكوين الأجهزة ، حدد Nios II -> إنشاء عنصر قائمة BSP لمشروع BSP مرة أخرى.

في الواقع ، بعد هذه العملية ، ظهرت كتلة جديدة في الملف

\ AVALON_DEMO \ software \ SDRAMtest_bsp \ system.h :

/* * CrazySerial_0 configuration * */ #define ALT_MODULE_CLASS_CrazySerial_0 CrazySerial #define CRAZYSERIAL_0_BASE 0x4011020 #define CRAZYSERIAL_0_IRQ -1 #define CRAZYSERIAL_0_IRQ_INTERRUPT_CONTROLLER_ID -1 #define CRAZYSERIAL_0_NAME "/dev/CrazySerial_0" #define CRAZYSERIAL_0_SPAN 16 #define CRAZYSERIAL_0_TYPE "CrazySerial"

بادئ ذي

بدء ، نحن مهتمون باستمرار

CRAZYSERIAL_0_BASE .

أضف الكود التالي إلى الوظيفة

الرئيسية () :

while (true) { IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x00); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x01); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x02); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x03); }

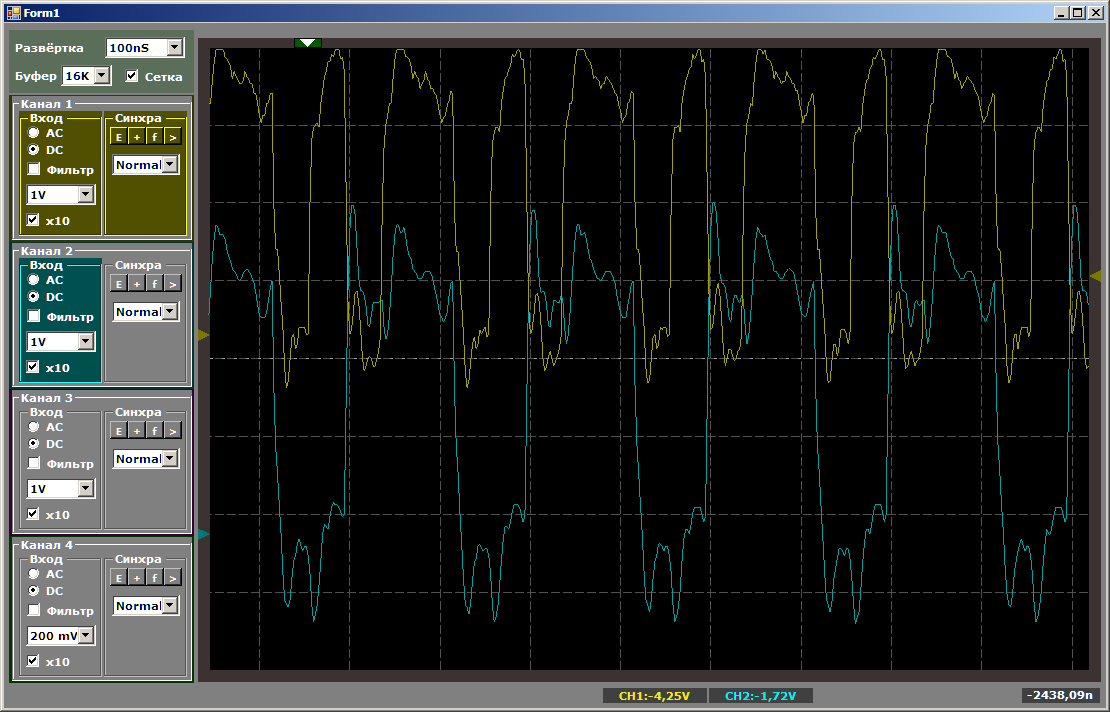

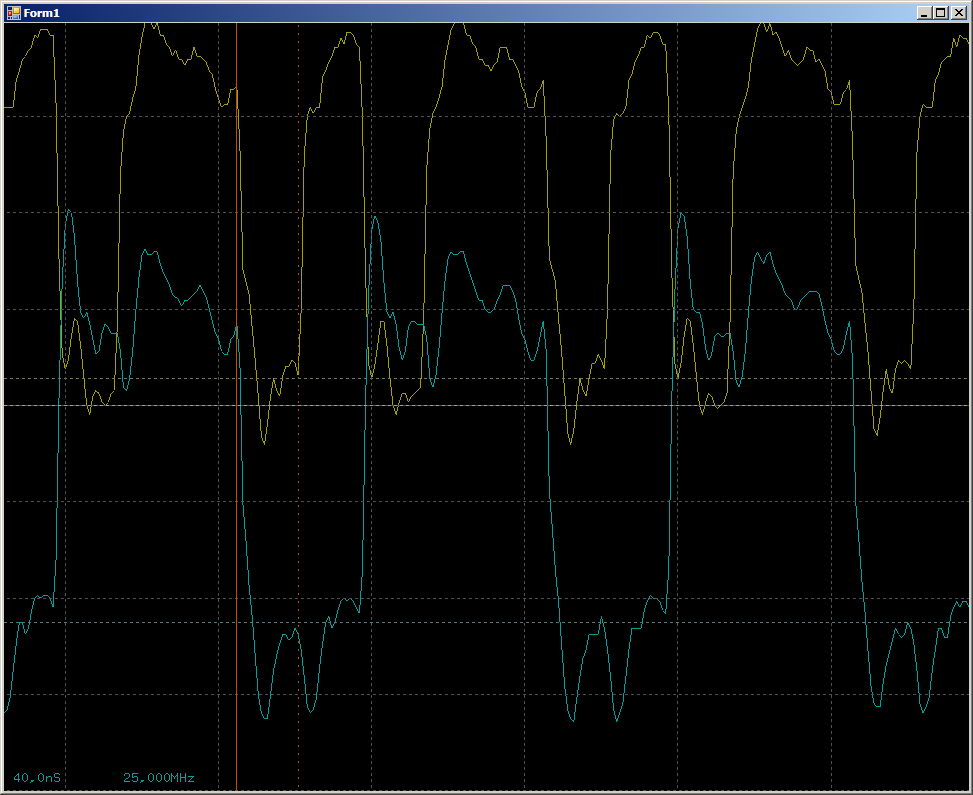

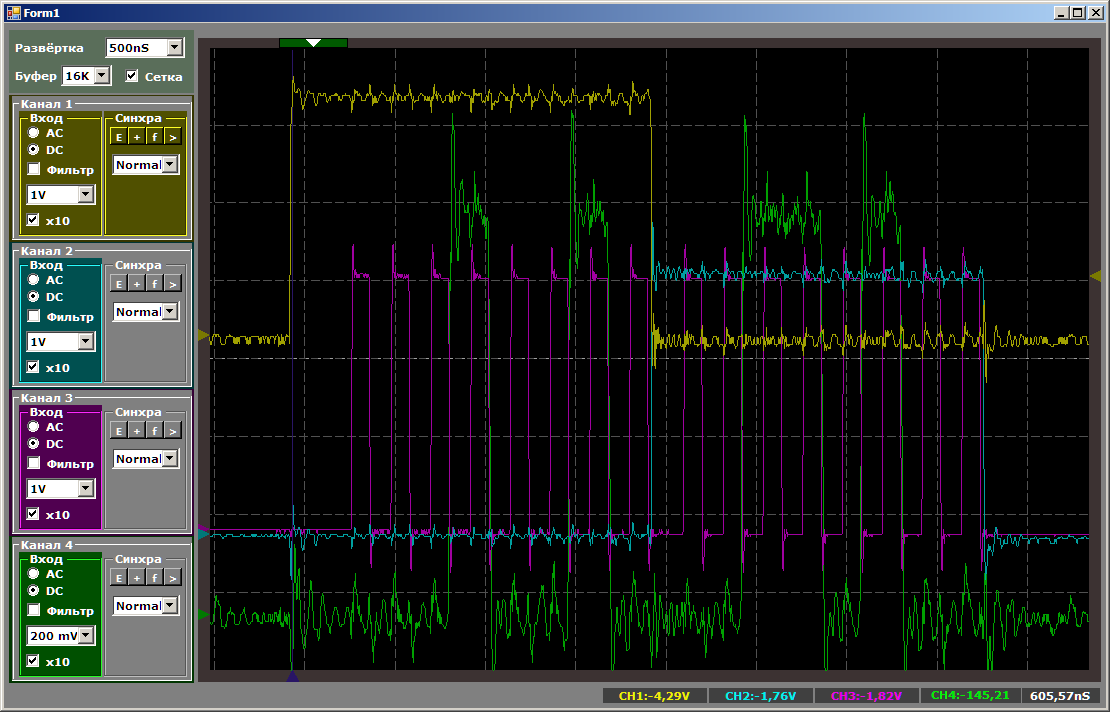

نبدأ في تصحيح الأخطاء وإلقاء نظرة على محتويات الخطوط مع الذبذبات. يجب أن يكون هناك كود ثنائي تزايدي. هو هناك.

علاوة على ذلك ، فإن تواتر الوصول إلى المنافذ رائع:

حوالي 25 ميغاهرتز هو نصف تردد الحافلة (دورتان على مدار الساعة). في بعض الأحيان ، لا يكون وقت الوصول إلى دورتين ، ولكنه أطول من ذلك. هذا يرجع إلى تنفيذ عمليات المتفرعة في البرنامج. بشكل عام ، أبسط وصول إلى أعمال الحافلة.

حان الوقت لإضافة وظيفة المنفذ التسلسلي على سبيل المثال. للقيام بذلك ، قم بإضافة إشارة واجهة

waitrequest المتعلقة بالحافلة وزوج من إشارات المنفذ التسلسلي -

sck و

sdo . إجمالي ، نحصل على جزء التعليمات البرمجية التالي على

systemverilog :

نفس النص: module CrazySerial ( input clk, input reset, input [1:0] address, input write, input [31:0] writedata, output waitrequest, output reg [1:0] cs, output reg sck, output sdo );

وفقًا لقواعد الشكل الجيد ، تحتاج إلى صنع آلة بسيطة تنقل البيانات. لسوء الحظ ، فإن الآلة الأكثر تعقيدًا في المقالة ستبدو صعبة للغاية. لكن في الواقع ، إذا لم أقم بزيادة وظائف الجهاز (وكجزء من المقالة لن أقوم بذلك) ، فستتضمن حالتين فقط: الإرسال قيد التقدم والإرسال لا يزال قيد التقدم. لذلك ، يمكنني ترميز الحالة بإشارة واحدة:

ريج الإرسال = 0 ؛

أثناء الإرسال ، أحتاج إلى عداد بسيط ، ومقسّم عقارب الساعة (أقوم به جهاز بطيء عن عمد) وسجل تحويل للبيانات المرسلة. أضف السجلات المناسبة:

reg [2:0] bit_cnt = 0; reg [3:0] clk_div = 0; reg [7:0] shifter = 0;

سأقسم التردد على 10 (مسترشداً بمبدأ "لماذا لا؟"). وفقًا لذلك ، في الخطوة الخامسة سأقوم بصيحة SCK ، وفي المرحلة العاشرة - أسقط هذا السطر ، وبعد ذلك - انتقل إلى الجزء التالي من البيانات. على جميع التدابير الأخرى ، ببساطة قم بزيادة عداد الفاصل. من المهم ألا ننسى أنك في المقياس الرابع تحتاج أيضًا إلى زيادة العداد ، وفي التاسعة - صفر. إذا تجاهلنا الانتقال إلى البت التالي ، فسيبدو المنطق المحدد كما يلي:

if (sending) begin case (clk_div) 4: begin sck <= 1; clk_div <= clk_div + 1; end 9: begin sck <= 0; clk_div <= 0; // < > end default: clk_div <= clk_div + 1; endcase end else

الذهاب إلى الشيء التالي سهل. لقد قاموا بتحويل سجل الإزاحة ، فإذا كانت البتة الحالية هي السابعة ، فقد توقفوا عن العمل عن طريق تبديل حالة الماكينة ، وإلا زادوا من عداد البتات.

shifter <= {shifter[6:0],1'b0}; if (bit_cnt == 7) begin sending <= 0; end else begin bit_cnt <= bit_cnt + 1; end

في الواقع ، هذا كل شيء. يتم أخذ بت الإخراج دائمًا من البت العالي في سجل الإزاحة:

assign sdo = shifter [7];

وأهم خط للمراجعة الحالية. يتم

ضبط إشارة

waitrequest إلى الوحدة دائمًا عند إرسال البيانات التسلسلية. أي أنها نسخة من إشارة

الإرسال التي تحدد حالة الجهاز:

assign waitrequest = sending;

حسنًا ، وعند الكتابة إلى العنوان 1 (أذكر ، هنا لدينا العنوان بكلمة 32 بت) ، نجمع البيانات في سجل الإزاحة ، ونفقد العدادات ونبدأ عملية النقل:

if (write) //... 2'h01: begin bit_cnt <= 0; clk_div <= 0; sending <= 1; shifter <= writedata [7:0]; end default:; endcase end

سأقدم الآن جميع الأجزاء الموصوفة كنص واحد: module CrazySerial ( input clk, input reset, input [1:0] address, input write, input [31:0] writedata, output waitrequest, output reg [1:0] cs, output reg sck, output sdo ); reg sending = 0; reg [2:0] bit_cnt = 0; reg [3:0] clk_div = 0; reg [7:0] shifter = 0; always @(posedge clk, posedge reset) begin if (reset == 1) begin cs <= 0; sck <= 0; sending <= 0; end else begin if (sending) begin case (clk_div) 4: begin sck <= 1; clk_div <= clk_div + 1; end 9: begin clk_div <= 0; shifter <= {shifter[6:0],1'b0}; sck <= 0; if (bit_cnt == 7) begin sending <= 0; end else begin bit_cnt <= bit_cnt + 1; end end default: clk_div <= clk_div + 1; endcase end else if (write) case (address) 2'h00: cs <= writedata [1:0]; 2'h01: begin bit_cnt <= 0; clk_div <= 0; sending <= 1; shifter <= writedata [7:0]; end default:; endcase end end assign sdo = shifter [7]; assign waitrequest = sending; endmodule

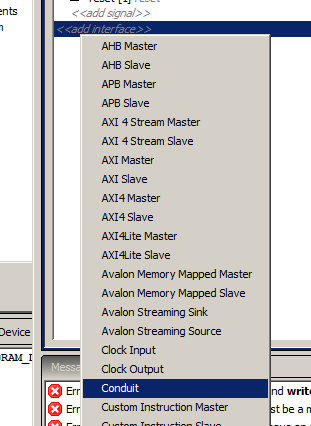

نبدأ في إدخال رمز جديد في النظام. في الواقع ، المسار هو نفسه عند إنشاء المكون ، ولكن يمكن بالفعل حذف بعض الخطوات. الآن سنتعرف فقط على عملية التحسين. انتقل إلى

مصمم النظام الأساسي . إذا قمنا بتغيير رمز verilog فقط ، فسيكون من السهل إجراء عملية

إنشاء HDL للنظام النهائي. ولكن بما أن الوحدة تحتوي على خطوط جديدة (أي ، الواجهة قد تغيرت) ، فيجب إعادة بنائها. للقيام بذلك ، حدده في الشجرة ، واضغط على زر الماوس الأيمن وحدد

تحرير .

نحن نقوم بتحرير النظام الحالي. لذا انتقل إلى علامة التبويب "

الملفات" وانقر فوق "

تحليل ملفات Sinthesis" :

من المتوقع حدوث أخطاء. لكننا نعرف بالفعل أن الخطوط الخاطئة هي المسؤولة. لذلك ، نذهب إلى علامة التبويب

Signals & Interfaces ، اسحب

sck و

sdo على طول نفس السطر من واجهة

avalon_slave_0 إلى واجهة

conduit_end :

أيضا إعادة تسمية حقول

نوع الإشارة لهم. يجب أن تكون النتيجة كما يلي:

في الواقع ، هذا كل شيء. انقر فوق "

إنهاء" ،

واتصل بإنشاء ملف HDL لنظام المعالج ، وصياغة المشروع في Quartus ، وتعيين أرجل جديدة:

هذه هي جهات الاتصال A21 و A22 لموصل الواجهة ، ونقوم بعمل التجميع النهائي ، وملء "البرامج الثابتة" في FPGA.

تحديث الحديد. الآن البرنامج. دعنا نذهب إلى الكسوف. ماذا نتذكر أن نفعل هناك؟ هذا صحيح ، لا تنسَ اختيار

إنشاء BSP .

في الواقع ، هذا كل شيء. يبقى لإضافة وظيفة إلى البرنامج. دعنا ننقل زوجًا من البايتات إلى المنفذ التسلسلي ، لكننا سنرسل البايت الأول إلى الجهاز المحدد بواسطة السطر

cs [0] ، والثاني -

cs [1] .

IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x01); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE+4,0x12); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x02); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE+4,0x34); IOWR_ALTERA_AVALON_PIO_DATA (CRAZYSERIAL_0_BASE,0x00);

يرجى ملاحظة أنه لا توجد اختبارات توفر هناك. الطرود تذهب واحدة تلو الأخرى. ومع ذلك ، على كل شيء الذبذبات تحولت تماما باستمرار

الأشعة الصفراء

cs [0] ،

الشعاع الأخضر

sdo ،

الأشعة البنفسجية هي

sck ،

والأشعة الزرقاء

cs [1] . يمكن أن نرى أن رمز 0x12 ذهب إلى الجهاز الأول ، 0x34 إلى الثاني.

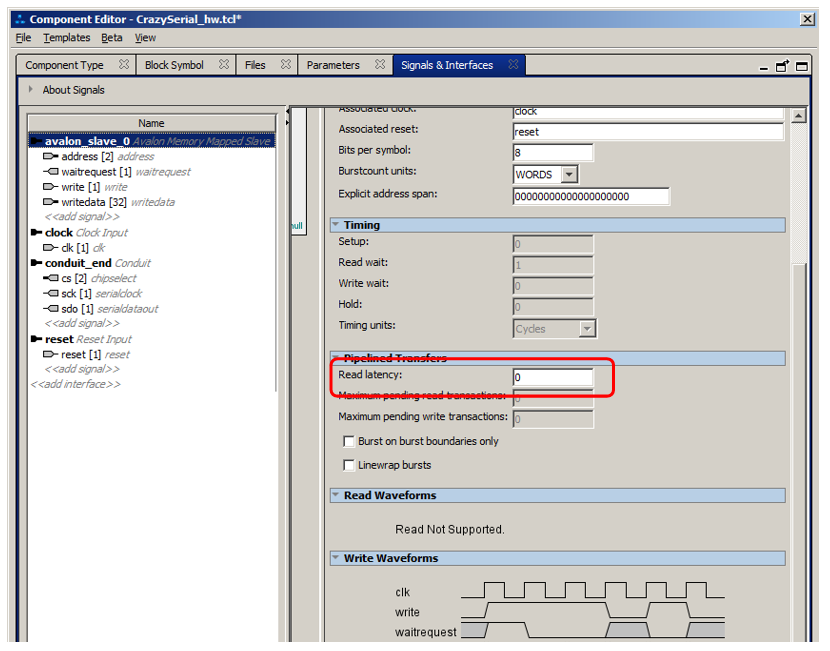

تتم القراءة بشكل مشابه ، لكن لا يمكنني الخروج بأي مثال جميل ، باستثناء القراءة العادية لمحتويات قدم الموصل. لكن هذا المثال يتدهور لدرجة أنه ليس من المثير للاهتمام القيام به. ولكن تجدر الإشارة هنا إلى أنه عند قراءة إعداد الحافلة هذا يمكن أن يكون في غاية الأهمية:

إذا كان هناك خط

قراءة ، فسيظهر مخطط توقيت للقراءة في مربع حوار الإعدادات. وسوف تظهر تأثير هذه المعلمة. عند قراءة أرجل الموصل ، لن يظل ذلك ملحوظًا ، ولكن عند القراءة من نفس FIFO أو RAM - تمامًا. يمكن تكوين ذاكرة الوصول العشوائي لإصدار البيانات مباشرة بعد إرسال العنوان ، أو يمكن إصدارها بشكل متزامن. في الحالة الثانية ، يتم إضافة الكمون. بعد كل شيء ، تعيين الحافلة العنوان ، تعيين القوية ... ولكن لا توجد بيانات على أقرب حافة إشارة الساعة. سوف تظهر بعد هذه الواجهة ... أي أن النظام لديه زمن انتقال زمن واحد. ويجب فقط أخذها في الاعتبار من خلال تحديد هذه المعلمة. باختصار ، إذا كنت لا تقرأ ما هو متوقع ، فعليك أولاً التحقق مما إذا كنت بحاجة إلى تكوين زمن انتقال. الباقي - القراءة لا تختلف عن الكتابة.

حسنًا ، دعني أذكرك مرة أخرى أنه من الأفضل عدم إزالة استعداد الحافلة للعمليات طويلة الأجل ، وإلا فمن الممكن تمامًا تقليل أداء النظام بشكل كبير. إشارة جاهزة جيدة لإجراء المعاملة لبضع دورات على مدار الساعة ، وليس ما يصل إلى 80 دورة على مدار الساعة ، كما في المثال الخاص بي. لكن أولاً ، سيكون أي مثال آخر غير مريح لهذه المقالة ، وثانياً ، بالنسبة لنواة اليوم الواحد ، هذا مقبول تمامًا. ستكون مدركًا تمامًا لأفعالك وستتجنب المواقف عند حظر الحافلة. صحيح ، إذا نجا القلب من الوقت المخصص له ، فإن مثل هذا الافتراض يمكن أن يفسد الحياة في المستقبل ، عندما ينسى الجميع ذلك ، ويبطئ كل شيء. ولكن سيكون في وقت لاحق.

ومع ذلك ، تعلمنا أن نجعل المعالج يتحكم في قلبنا. كل شيء واضح مع العالم الذي يعالج ، لقد حان الوقت للتعامل مع عالم البث. لكننا سنفعل ذلك في المقالة التالية ، وربما حتى عدة مقالات.

استنتاج

يوضح المقال كيف يمكن توصيل نواة Verilog التعسفية للتحكم في نظام معالج Nios II. يتم عرض الخيارات الخاصة بأبسط اتصال بحافلة Avalon ، وكذلك الاتصال الذي يمكن أن يكون الحافلة في حالة مزدحمة. يتم توفير روابط إلى المؤلفات ، والتي يمكنك من خلالها معرفة أوضاع التشغيل الأخرى لحافلة Avalon في وضع Memory Mapped.

المشروع الناتج يمكن تحميله من

هنا .