نحن نعتبر المعالج المركزي "العقل" للكمبيوتر ، ولكن ماذا يعني ذلك حقًا؟ ماذا يحدث بالضبط داخل مليارات الترانزستورات التي تجعل الكمبيوتر يعمل؟ في سلسلتنا المصغرة الجديدة المكونة من أربعة مقالات ، سننظر في عملية إنشاء بنية أجهزة الكمبيوتر والتحدث عن مبادئ تشغيلها.

في هذه السلسلة سوف نتحدث عن هندسة الكمبيوتر وتصميم لوحات المعالجات و VLSI (التكامل واسع النطاق للغاية) وتصنيع الرقاقات والاتجاهات المستقبلية في مجال تكنولوجيا الكمبيوتر. إذا كنت مهتمًا بفهم تفاصيل المعالجات ، فمن الأفضل أن تبدأ الدراسة بمجموعة المقالات هذه.

سنبدأ بشرح رفيع المستوى لما يقوم به المعالج وكيف تتصل كتل البناء بهيكل يعمل. على وجه الخصوص ، سنأخذ في الاعتبار نوى المعالجات ، والتسلسل الهرمي للذاكرة ، والتنبؤ بالفرع ، والمزيد. أولاً ، نحتاج إلى تقديم تعريف بسيط لما تقوم به وحدة المعالجة المركزية. أبسط تفسير: يتبع المعالج مجموعة من التعليمات لإجراء عملية معينة على الكثير من البيانات الواردة. على سبيل المثال ، يمكن قراءة قيمة من الذاكرة ، ثم إضافتها إلى قيمة أخرى ، وأخيراً حفظ النتيجة في الذاكرة في عنوان مختلف. قد يكون الأمر أكثر تعقيدًا ، على سبيل المثال ، تقسيم رقمين ، إذا كانت نتيجة الحساب السابق أكبر من الصفر.

تعد البرامج ، مثل نظام التشغيل أو اللعبة ، تسلسلًا من التعليمات التي يجب أن تنفذها وحدة المعالجة المركزية. يتم تحميل هذه التعليمات من الذاكرة وتنفيذها في معالج بسيط واحد تلو الآخر حتى انتهاء البرنامج. يقوم مطورو البرامج بكتابة البرامج بلغات عالية المستوى ، مثل C ++ أو Python ، لكن المعالج لا يستطيع فهمها. إنه يفهم فقط الأصفار والأصفار فقط ، لذلك نحتاج إلى تمثيل الرمز بطريقة ما في هذا التنسيق.

يتم تصنيف البرامج في مجموعة من الإرشادات منخفضة المستوى تسمى

لغة التجميع ، والتي تعد جزءًا من بنية مجموعة التعليمات (ISA). هذه مجموعة من الإرشادات التي يجب على وحدة المعالجة المركزية فهمها وتنفيذها. بعض من المعايير الدولية لتدقيق الحسابات الأكثر شيوعًا هي x86 و MIPS و ARM و RISC-V و PowerPC. بنفس الطريقة التي يختلف بها بناء الجملة لكتابة دالة في C ++ عن الوظيفة التي تؤدي نفس الإجراء في Python ، فإن كل ISA له بناء جملة مختلف خاص به.

يمكن تقسيم هذه المعايير الدولية إلى فئتين رئيسيتين: طول ثابت ومتغير. يستخدم ISA RISC-V إرشادات ذات طول ثابت ، مما يعني أن عددًا محددًا مسبقًا من وحدات البت في كل تعليمة يحدد نوع التعليمة. في x86 ، كل شيء مختلف ، ويستخدم تعليمات متغيرة الطول. في x86 ، يمكن تشفير التعليمات بطرق مختلفة مع أعداد مختلفة من البتات لأجزاء مختلفة. بسبب هذا التعقيد ، عادةً ما تكون وحدة فك ترميز التعليمات على معالج x86 الجزء الأكثر تعقيدًا من الجهاز بأكمله.

توفر الإرشادات ذات الطول الثابت فك ترميز بسيط نظرًا لوجود بنية ثابتة ، ولكنها تحد من إجمالي عدد الإرشادات التي يمكن أن تدعمها ISA. على الرغم من أن الإصدارات الشائعة من بنية RISC-V تحتوي على ما يقرب من 100 تعليمات وكلها مفتوحة المصدر ، فإن بنية x86 هي ملكية خاصة ولا أحد يعرف عدد التعليمات الموجودة فيها. من المعتقد بشكل عام أن هناك عدة آلاف من تعليمات x86 ، ولكن لا أحد ينشر العدد الدقيق. على الرغم من الاختلافات بين المعايير الدولية للتدقيق ، في الواقع لديهم جميعًا نفس الوظائف الأساسية.

مثال على بعض تعليمات RISC-V. شفرة التشغيل على اليمين بطول 7 بتات وتحدد نوع التعليمات. بالإضافة إلى ذلك ، يحتوي كل تعليمة على وحدات بت تحدد السجلات المستخدمة والوظائف التي يتم تنفيذها. بحيث يتم تقسيم تعليمات المجمّع إلى رمز ثنائي بحيث يفهمها المعالج.نحن الآن على استعداد لتشغيل الكمبيوتر وبدء تنفيذ البرامج. يحتوي تنفيذ التعليمات على عدة أجزاء أساسية ، والتي تنقسم إلى عدة مراحل من المعالج.

المرحلة الأولى هي نقل التعليمات من الذاكرة إلى المعالج لبدء التنفيذ. في الخطوة الثانية ، يتم فك تشفير التعليمات بحيث يمكن لوحدة المعالجة المركزية فهم نوع التعليمات التي هي عليها. هناك العديد من الأنواع ، بما في ذلك الإرشادات الحسابية والتعليمات الفرعية وإرشادات الذاكرة. بعد أن تكتشف وحدة المعالجة المركزية نوع التعليمات التي تنفذها ، يتم أخذ معاملات التعليمات من الذاكرة أو سجلات وحدة المعالجة المركزية الداخلية. إذا كنت تريد إضافة الرقم A والرقم B ، فلن تتمكن من إضافة حتى تعرف قيم A و B. معظم المعالجات الحديثة هي 64 بت ، أي أن حجم كل قيمة بيانات هو 64 بت.

64 بت هو عرض سجل المعالج و / أو قناة البيانات و / أو عنوان الذاكرة. بالنسبة إلى المستخدمين العاديين ، فإن هذا يعني مقدار المعلومات التي يمكن لجهاز الكمبيوتر معالجتها في وقت واحد ، وهذا هو أفضل ما يمكن فهمه بالمقارنة مع أحد الأقربين للعمارة الأصغر - معالج 32 بت. يمكن للهندسة 64 بت معالجة ضعف عدد البتات من المعلومات في وقت واحد (64 بت مقابل 32).بعد تلقي معاملات التعليمات ، يقوم المعالج بنقلها إلى مرحلة التنفيذ ، حيث يتم تنفيذ العملية على البيانات الواردة. يمكن أن يكون ذلك إضافة أرقام أو إجراء عمليات معالجة منطقية بأرقام أو ببساطة تمرير أرقام دون تغييرها. بعد حساب النتيجة ، قد يكون الوصول إلى الذاكرة مطلوبًا لتخزينه ، أو قد يقوم المعالج ببساطة بتخزين القيمة في أحد سجلاته الداخلية. بعد حفظ النتيجة ، تقوم وحدة المعالجة المركزية بتحديث حالة العناصر المختلفة وتنتقل إلى التعليمات التالية.

هذا التفسير ، بطبيعة الحال ، مبسط إلى حد كبير ، ومعظم المعالجات الحديثة تقسم هذه المراحل العديدة إلى 20 أو أكثر من المراحل الصغيرة لزيادة الكفاءة. هذا يعني أنه على الرغم من أن المعالج يبدأ وينتهي بعدد من الإرشادات في كل دورة ، فقد يستغرق الأمر 20 دورة أو أكثر لتنفيذ تعليمة واحدة من البداية إلى النهاية. عادة ما يطلق على هذا النموذج خط أنابيب ("خط أنابيب" ، يُترجم عادة إلى الروسية كـ "ناقل") ، لأنه يستغرق بعض الوقت لملء خط الأنابيب بسائل وإكماله ، ولكن بعد ملء التدفق (إخراج البيانات) سيكون ثابتًا.

مثال على ناقل ذو 4 مراحل. تشير المستطيلات متعددة الألوان إلى إرشادات مستقلة عن بعضها البعض.الدورة بأكملها التي تمر بها التعليمات هي عملية منسقة بعناية ، ولكن لا يمكن إكمال جميع التعليمات في نفس الوقت. على سبيل المثال ، تكون الإضافة سريعة جدًا ، ويمكن أن يستغرق تقسيم أو تحميل الذاكرة آلاف الدورات. بدلاً من إيقاف المعالج بالكامل حتى الانتهاء من تعليمة بطيئة واحدة ، يقوم معظم المعالجات الحديثة بتنفيذها بتغيير. أي أنهم يحددون أيًا من الإرشادات هي الأكثر فائدة للتنفيذ في الوقت الحالي وتخزين الإرشادات المؤقتة الأخرى التي ليست جاهزة بعد. إذا لم تكن التعليمة الحالية جاهزة بعد ، يمكن للمعالج القفز للأمام في الكود لمعرفة ما إذا كان هناك شيء آخر جاهزًا.

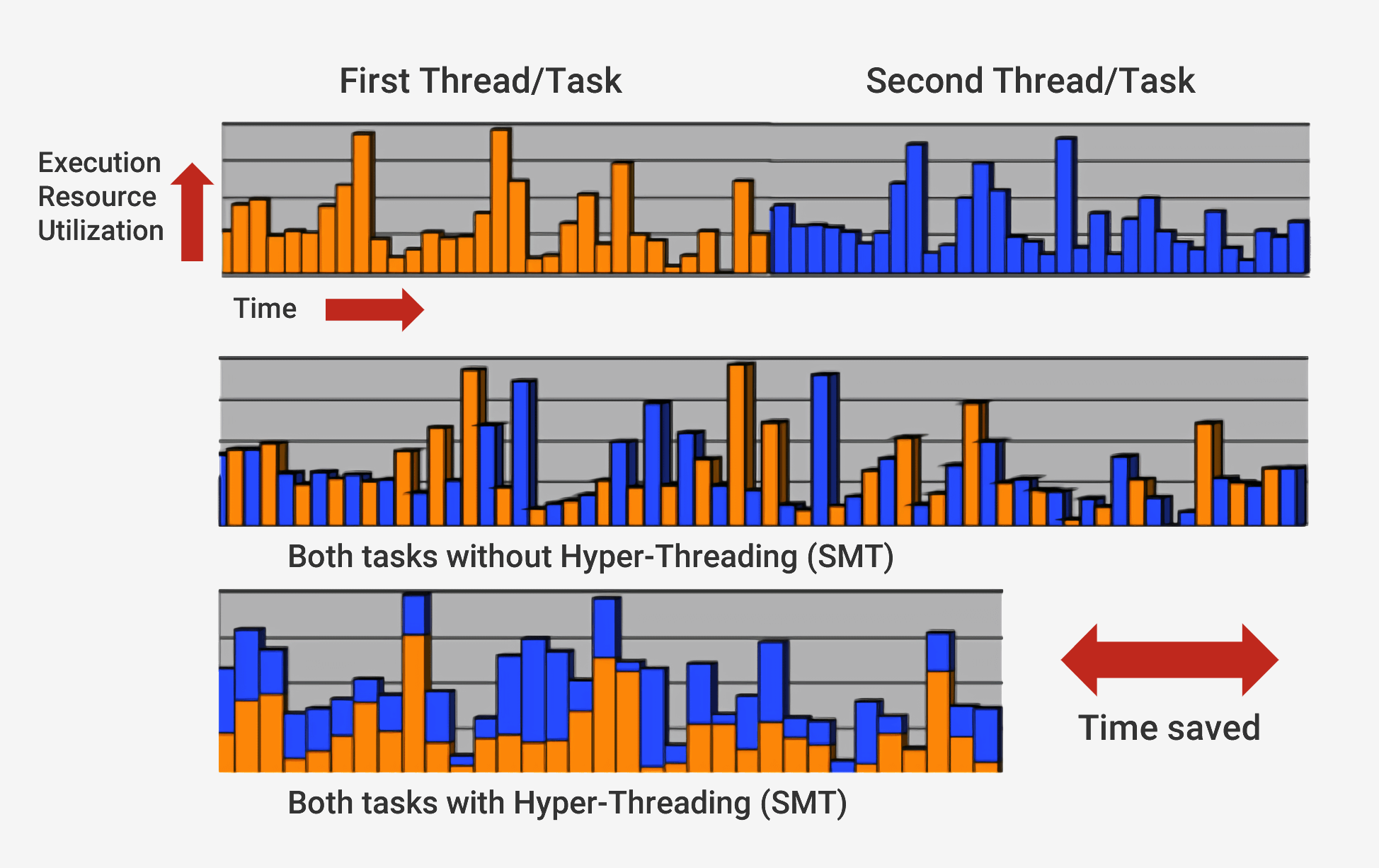

بالإضافة إلى التنفيذ مع سلسلة من التغييرات ، تستخدم المعالجات الحديثة تقنية تسمى

هندسة superscalar . هذا يعني أنه في أي وقت ، ينفذ المعالج في وقت واحد الكثير من التعليمات في كل مرحلة من مراحل خط الأنابيب. يمكن أن يتوقع أيضًا بدء المئات من التنفيذ ، ولكي يتمكن من تنفيذ العديد من التعليمات في وقت واحد داخل المعالجات ، هناك عدة نسخ من كل مرحلة من مراحل خط الأنابيب. إذا رأى المعالج أن هناك تعلمتين جاهزتين للتنفيذ ، ولا توجد تبعية بينهما ، فلا ينتظر حتى يكتمل كل منهما على حدة ، لكن يتم تنفيذهما في وقت واحد. أحد التطبيقات الشائعة لهذه البنية يسمى التعدد المتزامن (SMT) ويُعرف أيضًا باسم Hyper-Threading. تدعم معالجات Intel و AMD الآن SMT على الوجهين ، بينما طورت شركة IBM رقائق تدعم ما يصل إلى ثمانية SMTs.

لإكمال هذا التنفيذ المنسق بعناية ، يحتوي المعالج ، بالإضافة إلى الأساس الأساسي ، على العديد من العناصر الإضافية. يحتوي المعالج على المئات من الوحدات النمطية المنفصلة ، ولكل منها وظيفة محددة ، لكننا سننظر فقط في الأساسيات. الأكثر أهمية ومربحة هي ذاكرة التخزين المؤقت والتنبؤ من التحولات. هناك هياكل إضافية أخرى لن نأخذها في الاعتبار: إعادة ترتيب المخازن المؤقتة ، وإعادة تسجيل جداول إعادة التسمية ، ومحطات النسخ الاحتياطي.

قد تكون الحاجة إلى التخزين المؤقت مربكة في بعض الأحيان ، لأنها تخزن البيانات ، مثل RAM أو SSD. لكن المخابئ تختلف في زمن الوصول وسرعة الوصول. على الرغم من أن ذاكرة الوصول العشوائي (RAM) سريعة للغاية ، إلا أن حجمها أبطأ مما يحتاجه المعالج. قد تكون هناك حاجة إلى مئات الدورات للاستجابة بنقل بيانات ذاكرة الوصول العشوائي ، ولن يكون للمعالج أي شيء في هذا الوقت. وفي حالة عدم وجود بيانات في ذاكرة الوصول العشوائي ، فقد يستغرق الأمر عشرات الآلاف من الدورات للوصول إليها من SSD. بدون مخابئ ، ستتوقف المعالجات باستمرار.

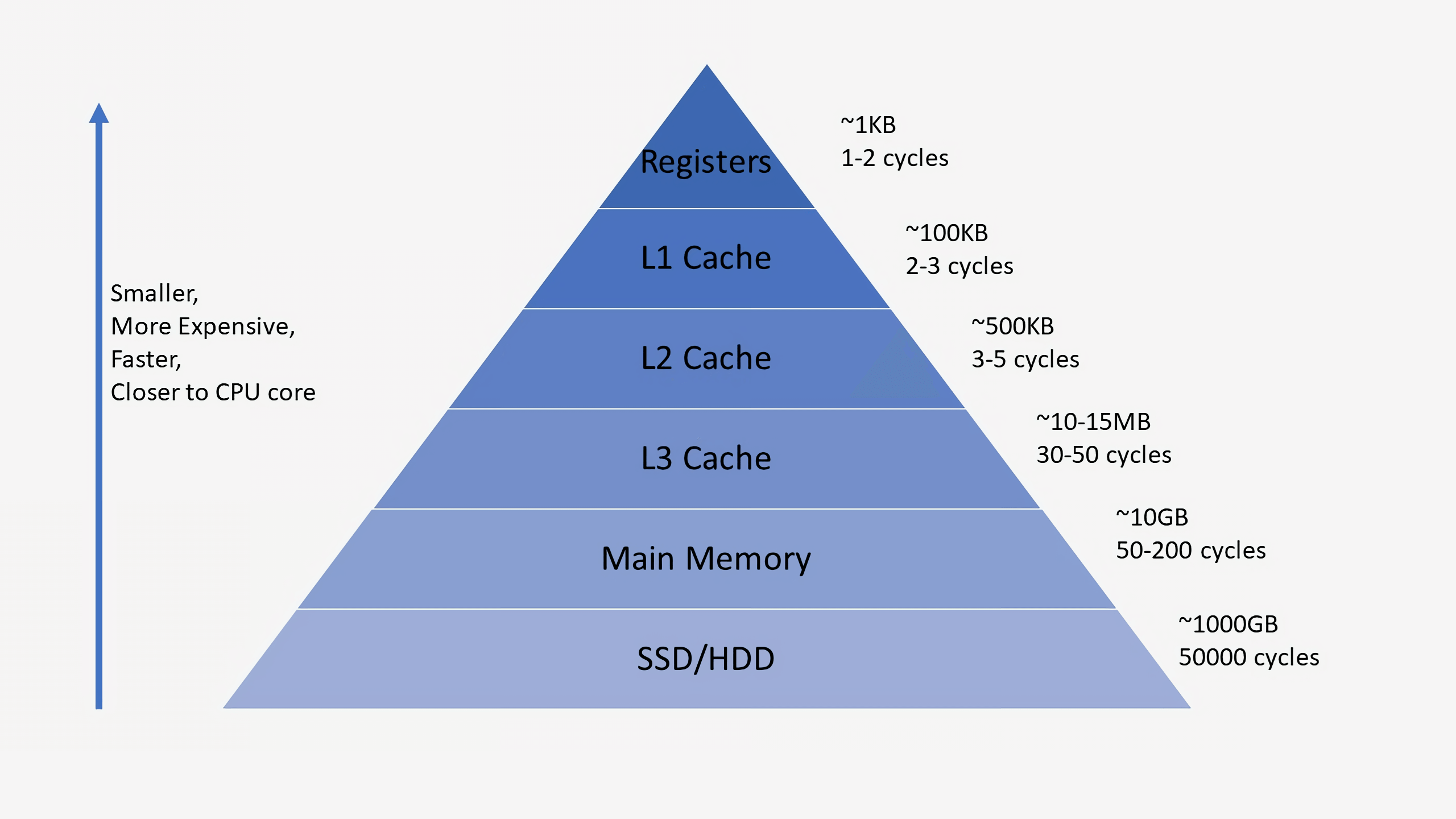

عادةً ما تحتوي المعالجات على ثلاثة مستويات من ذاكرة التخزين المؤقت تشكل

التسلسل الهرمي للذاكرة . L1 هي أصغر وأسرع ذاكرة التخزين المؤقت ، L2 في الوسط ، و L3 هي الأكبر والأبطأ في جميع ذاكرات التخزين المؤقت. أعلى المخازن المؤقتة في التسلسل الهرمي توجد سجلات صغيرة تخزن قيمة البيانات الوحيدة أثناء العمليات الحسابية. من حيث الحجم ، تعد هذه السجلات هي أسرع أجهزة التخزين في النظام. عندما يقوم المحول البرمجي بتحويل برنامج عالي المستوى إلى لغة التجميع ، فإنه يحدد أفضل طريقة لاستخدام هذه السجلات.

عندما تطلب وحدة المعالجة المركزية البيانات من الذاكرة ، تتحقق أولاً مما إذا كانت هذه البيانات مخزنة بالفعل في ذاكرة التخزين المؤقت L1. إذا كان الأمر كذلك ، فيمكنك الوصول إليها في بضع دورات فقط. إذا لم تكن هناك ، فسيقوم المعالج بفحص L2 ، ثم ذاكرة التخزين المؤقت L3. يتم تنفيذ ذاكرات التخزين المؤقت بطريقة تجعلها شفافة بشكل عام للنواة. تطلب النواة ببساطة البيانات على عنوان الذاكرة المحدد ، والمستوى في التسلسل الهرمي الذي يوجد به يجيب عليه. عند الانتقال إلى المستويات اللاحقة في التسلسل الهرمي للذاكرة ، يزداد الحجم والتأخير عادةً بأعداد كبيرة. في النهاية ، إذا لم تعثر وحدة المعالجة المركزية على بيانات في أي من ذاكرات التخزين المؤقت ، فإنها تصل إلى الذاكرة الرئيسية (RAM).

في كل معالج منتظم ، يحتوي كل نواة على مخبأين L1: واحد للبيانات والآخر للإرشادات. عادةً ما تبلغ سعة التخزين المؤقت L1 حوالي 100 كيلو بايت ويتنوع الحجم اعتمادًا كبيرًا على تكوين الشريحة والمعالج. بالإضافة إلى ذلك ، عادة ما يكون لكل نواة ذاكرة التخزين المؤقت L2 الخاصة به ، على الرغم من أنه في بعض البنى قد يكون من الشائع بين نواة. مخابئ L2 هي عادة عدة مئات من الكيلوبايت في الحجم. أخيرًا ، هناك ذاكرة تخزين مؤقت L3 واحدة مشتركة بين جميع النوى ، مع حجم ترتيب عشرات الميجابايت.

عندما ينفذ المعالج الرمز ، يتم تخزين الإرشادات وقيم البيانات الأكثر استخدامًا في ذاكرة التخزين المؤقت. يؤدي هذا إلى زيادة سرعة التنفيذ ، لأن المعالج لا يحتاج إلى الانتقال المستمر إلى الذاكرة الرئيسية للحصول على البيانات اللازمة. في الجزءين الثاني والثالث من السلسلة ، سنتحدث أكثر عن كيفية تنفيذ أنظمة الذاكرة هذه.

بالإضافة إلى ذاكرات التخزين المؤقت ، فإن أحد أهم العناصر الأساسية للمعالج الحديث هو

تنبؤ دقيق

بالانتقال . تتشابه إرشادات النقل (المتفرعة) مع التعليمات البرمجية if للمعالج. يتم تنفيذ مجموعة واحدة من التعليمات إذا كان الشرط صحيحًا ، والآخر إذا كان خاطئًا. على سبيل المثال ، نحتاج إلى مقارنة رقمين ، وإذا كانا متساويين ، فقم بأداء وظيفة واحدة ، وإذا لم تكن متساوية ، فقم بإجراء رقم آخر. هذه التعليمات الفرعية شائعة للغاية ويمكن أن تشكل حوالي 20 ٪ من جميع التعليمات في البرنامج.

للوهلة الأولى ، يبدو أن هذه التعليمات المتفرعة يجب ألا تتسبب في حدوث مشكلات ، لكن تنفيذها الصحيح قد يكون صعبًا للغاية على المعالج. في أي وقت ، قد يكون المعالج قيد التنفيذ في وقت واحد عشرة أو عشرين تعليمات ، لذلك من المهم للغاية معرفة الإرشادات

التي يجب تنفيذها. قد يستغرق الأمر 5 دورات لتحديد أن التعليمات الحالية هي عملية انتقال ، و 10 دورات أخرى لتحديد ما إذا كانت الحالة صحيحة. في هذا الوقت ، يمكن أن يبدأ المعالج بالفعل في تنفيذ العشرات من التعليمات الإضافية ، دون حتى معرفة ما إذا كانت هذه التعليمات مناسبة حقًا للتنفيذ.

للتغلب على هذه المشكلة ، تستخدم جميع المعالجات الحديثة عالية الأداء تقنية تسمى المضاربة. هذا يعني أن المعالج يتتبع تعليمات الفرع ويتساءل عما إذا كان سيتم تنفيذ الفرع الشرطي أم لا. إذا كان التنبؤ صحيحًا ، فقد بدأ المعالج بالفعل في تنفيذ الإرشادات التالية ، وهذا يوفر زيادة في الأداء. إذا كان التنبؤ غير صحيح ، فإن المعالج يتوقف عن التنفيذ ، ويحذف جميع الإرشادات غير الصحيحة التي بدأ تنفيذها ، ويبدأ من جديد من النقطة الصحيحة.

تعتبر تنبؤات الفروع هذه من أبسط أنواع التعلم الآلي لأن المتنبئ يدرس سلوك الفروع أثناء التنفيذ. إذا تنبأ بشكل غير صحيح في كثير من الأحيان ، يبدأ في تعلم السلوك الصحيح. لقد أسفرت عقود من البحث في تقنيات التنبؤ بالانتقال عن دقة التنبؤ بأكثر من 90٪ في المعالجات الحديثة.

على الرغم من أن التوقع يوفر زيادة كبيرة في الأداء ، لأن المعالج يمكنه تنفيذ الإرشادات الجاهزة بالفعل ، بدلاً من الانتظار في قائمة الانتظار حتى يتم الانتهاء ، فإنه يخلق أيضًا ثغرات أمنية. هجوم سبيكتر الشهير يستغل الأخطاء في توقع التحولات وتوقعها. يستخدم المهاجم التعليمات البرمجية المحددة خصيصًا لإجبار المعالج على تنفيذ التعليمات البرمجية بشكل استباقي ، مما يؤدي إلى تسرب قيم من الذاكرة. لمنع تسرب البيانات ، كان من الضروري إعادة تصميم بعض جوانب الترقب ، مما أدى إلى انخفاض طفيف في الأداء.

على مدى العقود الماضية ، قطعت الهندسة المعمارية المستخدمة في المعالجات الحديثة شوطا طويلا. أدى الابتكار وتطوير بنية مدروسة إلى زيادة الإنتاجية والاستخدام الأمثل للأجهزة. ومع ذلك ، فإن مطوري المعالجات المركزية يحافظون بعناية على أسرار تكنولوجياتهم ، لذلك لا يمكننا معرفة ما يحدث داخلها بالضبط. ومع ذلك ، يتم توحيد المبادئ الأساسية للمعالجات لجميع الهياكل والنماذج. يمكن أن تضيف Intel مكوناتها السرية لزيادة نسبة الزيارات إلى ذاكرة التخزين المؤقت ، ويمكن أن تضيف AMD مؤشر تنبؤات محسن ، لكن معالجات كلتا الشركتين تؤدي المهمة نفسها.

في هذه النظرة الأولى والمراجعة ، غطينا أساسيات كيفية عمل المعالجات. في الجزء التالي ، سوف نخبرك بكيفية تطوير المكونات التي تتكون منها المعالجات ، والحديث عن العناصر المنطقية ، وترددات الساعة ، وإدارة الطاقة ، والدوائر ، والمزيد.

القراءة الموصى بها