قررت أن أكتب هذه المذكرة عن حبري بالروسية والإنجليزية من أجل توزيع رابط إليها في منتديات ومجموعات اللغة الإنجليزية واللغة الروسية. النص الروسي ليس ترجمة للغة الإنجليزية والعكس - لقد كتبت ملاحظة مرتين (أكره الترجمة). يتم إرسال الأشخاص الذين يريدون انتقاد لغتي الإنجليزية فورًا إلى نهاية المنشور ، حيث سيصابون بالصدمة من لهجتي في شريط فيديو مدته ساعة طويلة. لا أركز على تأكيدي على أنه خطأ ، ولكن كميزة. نعلم جميعًا أن العديد من الأمريكيين يجدون ، على سبيل المثال ، لهجة بريطانية بلعومية جذابة. لقد حان الوقت لإعطاء نفس المكانة لهجة روسية شديدة. للقيام بذلك ، يحتاج أكبر عدد ممكن من الروس إلى إلقاء الخطب في مختلف الأحداث الدولية. كلمة المرور الخاصة بنا هي "سنوات ميل تتحدث من ماي هارت".

ولكن أولا عن المعرض.

يشاهد الملايين من مستهلكي الأدوات في جميع أنحاء العالم معرض الإلكترونيات الاستهلاكية (CES) ، الذي سيقام في لاس فيجاس في يناير. إنهم ، الذين لم يعرفوا مطلقًا معنى D-trigger ، يجادلون بأهمية أن أربعة جيجاهيرتز أفضل من ثلاثة في أحدث المعالجات من AMD و Qualcomm. ولكن هناك معرض لا يركز على المستهلكين ، ولكن على مطوري الإلكترونيات. يُطلق على هذا المعرض مؤتمر أتمتة التصميم (DAC) ، وفي بعض السنوات يتم عقده أيضًا في لاس فيجاس ، ولكن ليس في ديسمبر ، ولكن في يونيو.

يشاهد الملايين من عشاق الأدوات كل عام معرض الإلكترونيات الاستهلاكية (CES) الذي يقام في لاس فيجاس في يناير. هؤلاء الناس ، الذين لم يتعلموا أبدًا وظيفة D-flip-flop وكيف يتم حساب التوقيت الثابت ، يناقشون ترددات جيجاهيرتز بعد قراءة أحدث المقالات في مجلة Wired التي يرون أنها منشور فني. ومع ذلك ، هناك مؤتمر آخر ، ليس للمستهلكين ، ولكن لمنشئي الإلكترونيات. يُطلق على هذا المؤتمر مؤتمر أتمتة التصميم (DAC) ، كما يتم عقده في لاس فيجاس ، وإن لم يكن كل عام ، وليس في يناير ، ولكن في يونيو.

صناعة أتمتة التصميم الإلكتروني (EDA) تصنع برامج لمصممي الأجهزة. يتم التحكم في جمعية الإمارات للغوص من خلال ثلاث شركات كبيرة: سينوبسيس ، وكادينس ومنتور جرافيكس (أصبحت الآن جزءًا من سيمنس). يحتوي كل من سينوبسيس و Cadence على مجموعة كاملة من المنتجات اللازمة لتصميم رقاقة رقمية ومحاكاة على مستويات متعددة. يبدأ تدفق التصميم ، المسمى RTL2GDSII ، من تحديد وترميز سلوك دورة الدائرة بلغة وصف الأجهزة (Verilog أو VHDL) ، ويستمر في تجميع هذا الوصف في رسم بياني للعناصر المنطقية (netlist) ، ثم يستمر في وضع netlist في قائمة مادية مخطط للرقاقة وتوجيه الأسلاك على رقاقة لربط الخلايا القياسية ، اللبنات الأساسية لل ASICs (الدوائر المتكاملة التطبيق محددة).

تهيمن ثلاث شركات كبيرة على صناعة أتمتة تصميم الإلكترونيات: سينوبسيس ، وكادينس ومنتور جرافيكس (التي اشترتها شركة سيمنز قبل عامين). قامت سينوبسيس و Cadence بإنشاء برنامج يغطي مسار تصميم RTL2GDSII بأكمله. وصفت هذا المسار بإيجاز في مقالتي

السابقة في DAC قبل أربع سنوات:

على مدار 25 إلى 30 عامًا ، غالبًا ما يتم كتابة تصميم الدائرة الدقيقة بلغة وصف المعدات Verilog (في أوروبا وبين الجيش - VHDL) ، وبعد ذلك يقوم برنامج خاص (التوليف المنطقي) بتحويل التصميم إلى رسم بياني للأسلاك والأولويات المنطقية ، وبرنامج آخر (تحليل التوقيت الثابت) يخبر المصمم ما إذا كان يتناسب مع ميزانية السرعة ، والبرنامج الثالث (المكان والمسار) يحدد هذا التصميم على موقع الشريحة.

عندما يمر التصميم بجميع المراحل: الترميز على veril ، وتصحيح الأخطاء ، والتحقق ، والتوليف ، وتحليل توقيت ثابت ، وتخطيط الأرضية ، وتحديد المكان ، واستخراج parasitics ، الخ - يظهر ملف يسمى GDSII ، والذي يتم إرساله إلى المصنع ، ويخبز المصنع رقائق البطاطس. تعود ملكية المصانع الأكثر شهرة من هذا النوع إلى شركة Taiwan Semiconductor Manufacturing Company أو TSMC.

جون سانجوينيتي ، وهو مدرس فيريلوج منذ الثمانينات. كان جون مؤسس شركة تدعى Chronologic Simulation ، والتي في التسعينات من القرن الماضي ، أنشأت VCS ، محاكي كود فيريلوج مترجم. هذه المحاكاة هي الآن ملكية لشركة سينوبسيس. يستخدم VCS من قبل غالبية الشركات الإلكترونية الكبيرة. جلب VCS إلى سينوبسيس مليار دولار في الإيرادات.

إلى جانب صالة العرض ، يوجد جون سانجوينتي ، وهو معلم فيروولوجي مبكر من ثمانينيات القرن الماضي ومؤسس محاكاة كرونولوجيك. لقد منحت هذه الشركة العالم محاكي Simil (VCS) المحاكي السريع لـ Verilog ، والذي أصبح الآن ملكًا لشركة Synopsys. يتم استخدام هذا المحاكاة بواسطة معظم مطوري الشرائح الرئيسيين. VCS تجلب سينوبسيس مليارات الدولارات:

Mentor Graphics هي الآن جزء من Siemens ، ثالث أكبر شركة EDA. بخلاف Synopsys و Cadence ، لا يوجد لدى Mentor Graphics مجموعة كاملة من أدوات RTL2GDSII. تأتي أكثر تدفقات الإيرادات المعترف بها من Caliber ، وهي مجموعة من أدوات التحقق من التصميم الفعلي ، و Veloce ، محاكي الأجهزة. يتضمن Caliber على سبيل المثال أداة تتحقق من قواعد التصميم الهندسي (العرض ، المسافات ، العلبة) على "المخططات" النهائية للرقاقة. يستخدم Veloce رقائقًا تشبه FPGA

تحاكي محاكاة تصاميم Verilog بسرعة كبيرة.

أصبحت Mentor Graphics ، ثالث أكبر شركة في صناعة EDA ، في نهاية عام 2016 جزءًا من Siemens. على عكس Synopsis و Keydens ، لا يوجد لدى Mentor سلسلة كاملة من البرامج التي تغطي مسار RTL2GDSII. هناك مصدران رئيسيان لدخل Mentor هما حزمة برامج Caliber ، التي تقوم بالتحقق في المرحلة النهائية من تصميم رقاقة ، ومحاكي Veloce (واضح Velochi). مثال على التحقق في Caliber هو الحد الأدنى للمسافة بين المسارات على الرقاقة

بحيث لا توجد تأثيرات للهوائي .

محدث: تصحيح على أساس تعليق amartology : الهوائي هو حول آخر عموما. يحدث ذلك عندما يصبح مسار واحد كبيرًا للغاية بحيث يبدأ في العمل مثل الهوائي ، ويستقبل إشارة على تردد ذبذبات البلازما للحفر أثناء الإنتاج.ويستخدم محاكي Veloce ASIC على شكل FPGA

لمحاكاة بسرعة

محاكاة محاكاة الدوائر الموصوفة على المستوى المنطقي ، أي في الحقيقة.

بالإضافة إلى مشاريع Caliber و Veloce المربحة للغاية ، كان لدى Mentor دائمًا عدد كبير من المشاريع والمنتجات والخدمات والتدريبات والبرامج التعليمية الأخرى. على سبيل المثال تقوم Mentor بتطوير مجال التحقق الوظيفي ، وهو جزء مهم للغاية من سير عمل التصميم الرقمي.

بالإضافة إلى مشاريع مربحة للغاية مثل Caliber و Veloce ، لدى Mentor العديد من المشاريع والمنتجات والخدمات والمشاريع البحثية والبرامج التعليمية. على سبيل المثال ، في Mentor ، يشاركون في التحقق الوظيفي ، وهو جزء هام من عملية الإنتاج:

يقوم عدد من الشركات الصغيرة ، بما في ذلك Doulos و Willamette HDL و Sunburst Design ، ببيع التدريب على التحقق من الأجهزة لشركات إلكترونية كبيرة ومتوسطة الحجم. يوجد مثل هذا التخصص لأن الجامعات لا تقوم بتدريس فن التحقق الوظيفي بشكل صحيح ولا تعتمد تقنيات جديدة ، مثل System Verilog و UVM والتحقق الرسمي باستخدام التأكيدات المتزامنة والمحمول المحمول وغيرها في مناهجها الدراسية لعقود. حتى جامعة ستانفورد ليس لديها في مناهجها بقدر ما أعرف من التحدث مع خريجيها.

يغذي التحقق الوظيفي العديد من الشركات الصغيرة التي تبيع التدريبات SystemVerilog و UVM للشركات الكبيرة بأسعار مرتفعة منعشة ، مثل بضعة آلاف من الدولارات للشخص الواحد. وتشمل هذه Doulos ، Willamette HDL ، Sunburst Design وغيرها:

شركة صغيرة أخرى تسمى Verific. لديهم فقط حفنة من الناس لكنهم ناجحون للغاية في مكانهم. تبيع Verific موزعي SystemVerilog المعتمدين من قبل شركات EDA الهامة ، الكبيرة والصغيرة.

هنا شركة صغيرة أخرى ، فقط عدد قليل من الأشخاص ، لكنها شركة ناجحة من نوعها تدعى Verific. تبيع محلل Verilog ، والذي تستخدمه العديد من شركات EDA:

يقدم مؤسس Verific مقابلة مع موقع EDA شعبي يسمى EDA Cafe. هناك العديد من مواقع الويب الشائعة الأخرى الخاصة بـ EDA ، بما في ذلك موقع John Cooley's deepchip.com ، لكنني لم أقابل John Cooley في قاعة DAC هذه المرة.

إليك مؤسس Verific الذي أجرى مقابلة مع EDA Cafe ، وهو موقع شهير في هذا المجال:

الآن دعنا نتحدث عن FPGA.

الآن دعنا نتحدث عن FPGAs ، فهي PPVM (سوف يصححني الآن) ، فهي FPGA.

ما هو عليه ، كما وصفت بإيجاز في مقالتي

السابقة DAC قبل أربع سنوات:

في أبسط إصدار ، يتكون FPGA من مصفوفة من الخلايا المتجانسة ، يمكن تغيير كل منها إلى وظيفة باستخدام معددات متعددة متصلة بتات ذاكرة التهيئة. يمكن أن تصبح خلية واحدة بوابة AND مع أربعة مدخلات ومخرج واحد ، وآخر - سجل بت واحد ، إلخ. نقوم بتحميل سلسلة من البتات من الذاكرة إلى ذاكرة التهيئة - ويتم تشكيل الدائرة الإلكترونية المحددة في FPGA ، والتي يمكن أن تكون معالجًا ، ووحدة تحكم في العرض ، إلخ.

FPGAs / FPGAs ليست معالجات ؛ من خلال "برمجة" FPGAs (ملء ذاكرة تكوين FPGAs) تقوم بإنشاء دائرة إلكترونية (الأجهزة) ، بينما عند برمجة معالج (أجهزة ثابتة) ، تنزلق سلسلة من تعليمات البرنامج التسلسلي المكتوبة فيه (البرمجيات).

أكبر منتجي FPGA هما Xilinx و Altera ، وهما الآن جزء من Intel.

أكبر شركتين تنتج FPGAs هما Xilinx و Altera ، وهما الآن جزء من Intel:

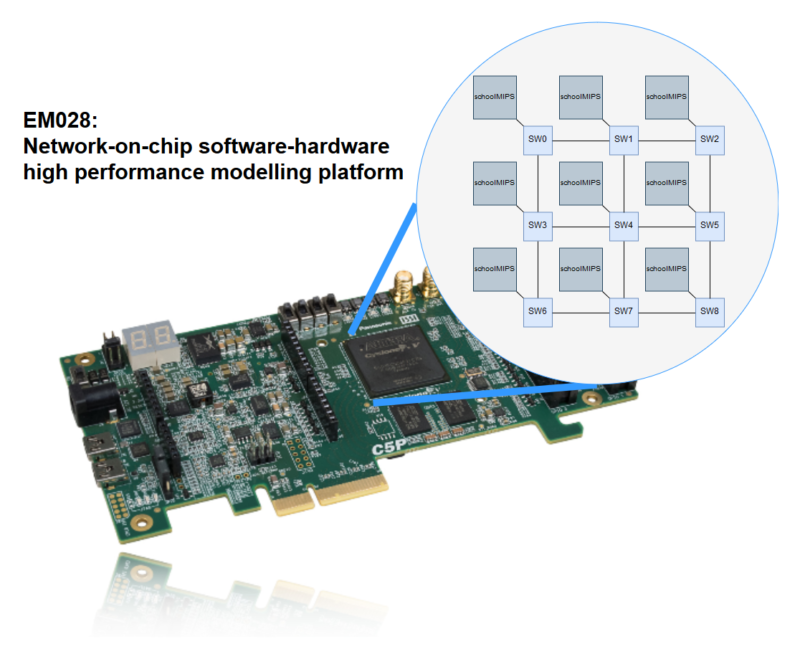

تجمع Intel هذا الأسبوع الأصوات للجولة الأولى من مسابقة Innovate FPGA. يستخدم أحد الإدخالات الروسية شبكة من نوى المعالج schoolMIPS الصغيرة. تنفذ

schoolMIPS مجموعة فرعية من هندسة MIPS. إنه موجود في العديد من المتغيرات ، بما في ذلك دورة واحدة مع عدم وجود ذاكرة البيانات (أبسط واحد) ، إصدار مع المقاطعات ، إصدار خط أنابيب ، إلخ:

بالمناسبة ، ستصوت إنتل هذا الأسبوع في مسابقة Innovate FPGA ، التي تشارك فيها

الفرق الروسية أيضًا . أحد المشاريع هو

النموذج الأولي لنظام المعالجة المتعددة المستندة إلى NoC . هذه شبكة نموذجية على شريحة تحتوي على عدد كبير من العقد استنادًا إلى معالجات بقلم Stanislav Zhelnio

sparf (استنادًا إلى كتاب Harris & Harris "التوليف الرقمي وهندسة الكمبيوتر")

https://github.com/MIPSfpga/schoolMIPS . يجعل طالبًا لمدة 4 سنوات في MIEM NRU HSE:

لا يقتصر عالم FPGAs على Xilinx و Altera / Intel. هناك العديد من البائعين الأصغر بكثير ، مثل Lattice و Microsemi / Actel ، وحتى الشركات الصغيرة التي لا تصمم شرائح النهاية نفسها ترخص تصميم كتل خلايا FPGA لشركات ASIC. قد يكون التطبيق المفيد هو إنشاء معالج ثانوي قابل لإعادة التكوين ومتصل بنواة CPU عالية التردد ثابتة. تطبيق آخر هو الأمن: تريد بعض الشركات إخفاء أسرارها في منطق قابل لإعادة التشكيل بدلاً من إظهار تصميم منطقها الثابت لباحث متحمس له مجهر إلكتروني وكثير من الوقت.

ولكن هناك عدد أقل من اللاعبين في عالم FPGA ، على سبيل المثال ، إليك شركتان ترخصان لتصميم كتل FPGA التي يمكن دمجها في دوائر ثابتة متعددة التشغيل لمنحها المرونة.

يحتوي كل DAC على العديد من بائعي لوحة FPGA. ليس بائعو لوحات الطلاب الرخيصة مثل Digilent و Terasic ، والتي تبدأ من 55 دولارًا ، ولكن لوحات FPGA لنماذج ASIC التي يمكن أن تكلف 30،000 دولار أو 100000 دولار أو أكثر.

يحضر DAC تقليديا من قبل الشركات المصنعة للوحات FPGA. إنهم لا يبيعون بطاقات طلابية رخيصة مقابل 55 دولارًا ، ولكن لوحات FPGA خطيرة مقابل 55 دولارًا - ألف دولار وأكثر. موكلهم ليس طالبًا ، ولكن فريق تطوير ASIC شديد يستخدم مجالس كبيرة للنماذج الأولية.

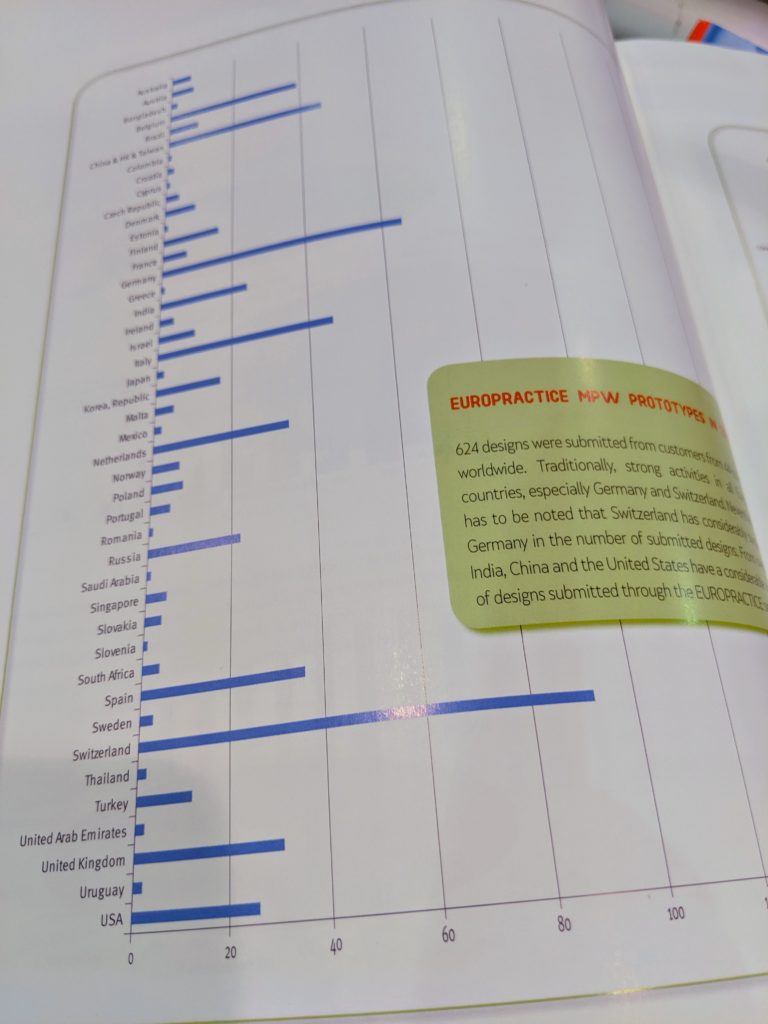

ماذا لو قام أحد الباحثين ببعض الأدلة على المفهوم باستخدام FPGA ويريد الآن تصنيع ASIC الخاص به؟ يتطلب الأمر التجاري النموذجي لتصنيع ASIC الدفع المبدئي من 300 ألف دولار إلى 3000،000 دولار تقريبًا اعتمادًا على تقنية العملية. ومع ذلك ، هناك شركات متخصصة ، Europractice في أوروبا و MOSIS في الولايات المتحدة ، التي تبيع خدمات "مكوكية" صغيرة الحجم ، أو خدمات بسكويت الويفر متعدد المشروعات ، ابتداءً من 3000 دولار فقط لتكنولوجيا 180nm أو عشرات الآلاف من الدولارات مقابل شيء عصري ، مثل 28nm.

ولكن ماذا لو أراد طالب أو شركة قاسية إنشاء ASIC حقيقي في مصنع ، وهناك القليل أو القليل من المال؟ أو ، إن لم يكن آسف ، هل هي شريحة اختبار أم مجموعة صغيرة جدًا؟ للقيام بذلك ، يوجد في أمريكا شركة MOSIS ، وفي أوروبا - Europractice. بضعة آلاف من الدولارات - وكان لديك في أيديكم الشريحة التي صممتها للتكنولوجيا مثل 180 نانومتر. بضع عشرات من الآلاف - لديك بين يديك رقاقة على أحدث التقنيات ، على سبيل المثال 28 نانومتر ، مثل iPhone الخامس. ألاحظ أنه بالنسبة للإنتاج التجاري الضخم ، فإن الدفعة الأولى للمصنع تتراوح من مئات الآلاف من الدولارات للتكنولوجيات القديمة إلى مليوني أو ثلاثة ملايين للتكنولوجيات الجديدة.

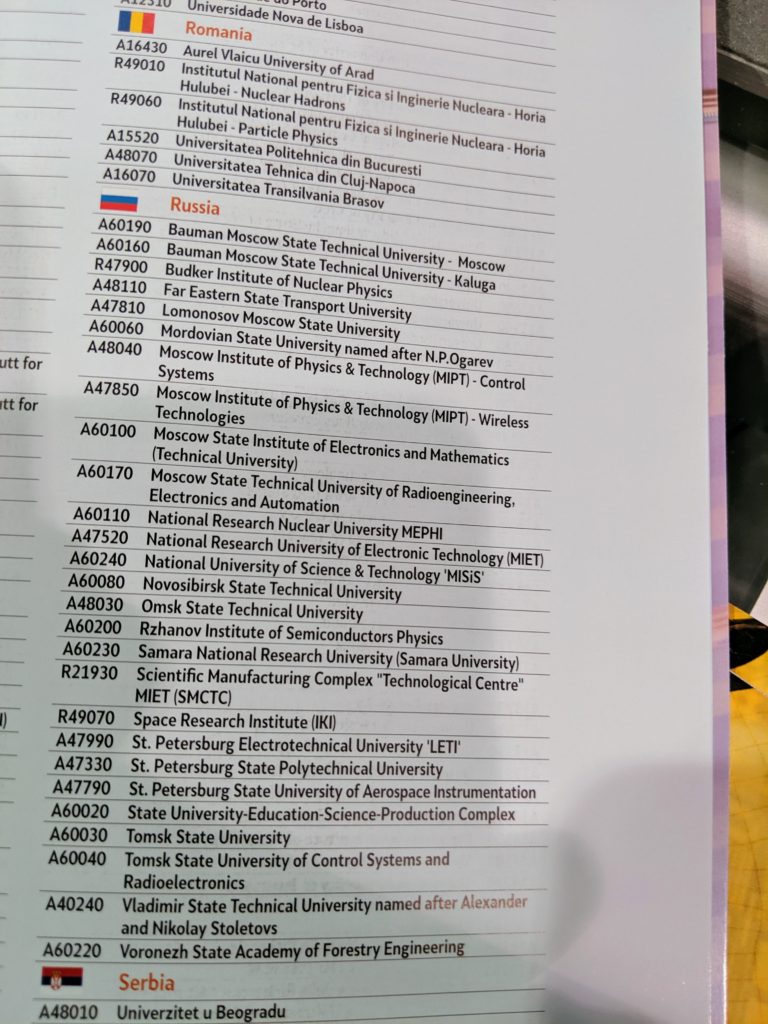

من المثير للاهتمام أن لدى Europractice عملاء في روسيا ، حتى في أومسك. اعترف الذي يصمم ASICs في أومسك.

Europractice لديها عدد من الشركات الروسية ، بما في ذلك شخص ما في أومسك:

هناك شركات لها نماذج أعمال غامضة بعض الشيء بالنسبة لي. على سبيل المثال ، أنا لا أفهم كيف يمكن لهذه الشركة أدناه أن تعيش على مكوّن إضافي Eclipse. أعتقد أنهم يحصلون على معظم الإيرادات يبيعون بعض الخدمات الاستشارية.

هناك شركات لا أفهم كيف يكسبون. على سبيل المثال ، هذا واحد هو بيع البرنامج المساعد Eclipse المتخصصة جدا. بالتأكيد لا يعيشون عليه ، ولكن على نوع من الاستشارات.

شركة أخرى متخصصة مع نموذج عمل غير واضح. يقومون بترجمة وصف للسجلات المرئية للبرامج إلى منطق الغراء Verilog وملفات الواجهة الأخرى. أعتقد أن هذه الشركة قد يكون لديها بعض العملاء الكبار من نوع Cisco الذين كانوا مدمنين على التكنولوجيا الخاصة بهم منذ وقت طويل ودفع لهم منذ ذلك الحين.

شركة أخرى متخصصة مع نموذج عمل غير واضح. أنها تترجم وصف السجلات المتاحة للمبرمج في فيريلوج وملفات الواجهة. من المحتمل أن يكون لديهم بعض العملاء الرئيسيين مثل Cisco ، التي كانت تحبهم أدواتهم منذ عدة سنوات ، ومنذ ذلك الحين كانت تدفع منذ أن كان من المشاغبين استئجار عميل لإدارة مهندسهم.

وصف رجل مهذب من شركة Huawei إنجازاتهم في رقائق الشبكات. من الواضح أن Huawei تعتمد على أدوات EDA الأمريكية ، أكثر من اعتمادها على أسواق Android و ARM CPU. إنهم يمثلون مبلغًا من المال ، كما أن عدد الخبراء التقنيين اللازمين لتطوير مكافئ برنامج التحويل البرمجي IC من سينوبسيس أكبر بكثير ، في رأيي ، من الموارد اللازمة لتصميم منافس متقدم لنوى ARM.

كما جلس ممثل لشركة Huawei في المعرض معربًا عن حزنه المشرق على وجهه. وألاحظ أنه إذا كانت الحكومة الأمريكية تجبر شركات EDA الأمريكية على حظر الصينيين ، فسيكون الوضع الصيني أسوأ بكثير مما هو عليه الآن ، لأنه من الصعب تقنياً استنساخ سينوبسيس IC Compiler من نوى ARM و Android Market.

كان لكل DAC منذ عام 1998 شركة واحدة على الأقل تقوم بتطوير مترجم C-to-Verilog آخر. مرة أخرى في عام 1998 كان

بدء التشغيل الخاص بي . هذا العام هو شخص آخر:

منذ عام 1998 ، كانت هناك شركة واحدة على الأقل في DAC تقوم بتجميع C في Verilog. في عام 1998 ، كان مثل هذه الشركة بدء التشغيل الخاص بي. هذا العام شخص آخر:

هذا الرجل المحترم يكسب رزقه من خلال بيع الحلول التي تعارض ما يسمى "Zakladki" (مصطلح روسي ، بصيغة الجمع لـ "Zakladka"). شرحت له معنى المصطلح ووافق على أن هذا ما يبيعه.

إليك رفيقًا يصنع إشارات مرجعية للمحللين الأحياء في المعالجات:

أحضرت إلى DAC ابنتي الطلابية حتى تتمكن من معرفة كيف يكسب أبي العيش:

أحضرت ابنتي إلى لاس فيغاس حتى تتمكن من رؤية كيف يكسب الناس المال في العالم الصناعي القاسي في الصناعة الإلكترونية وأدركت أن أموال أبيها لم تنمو على الأشجار:

الحفلة بعد المعرض:

في الحفلة بعد المعرض:

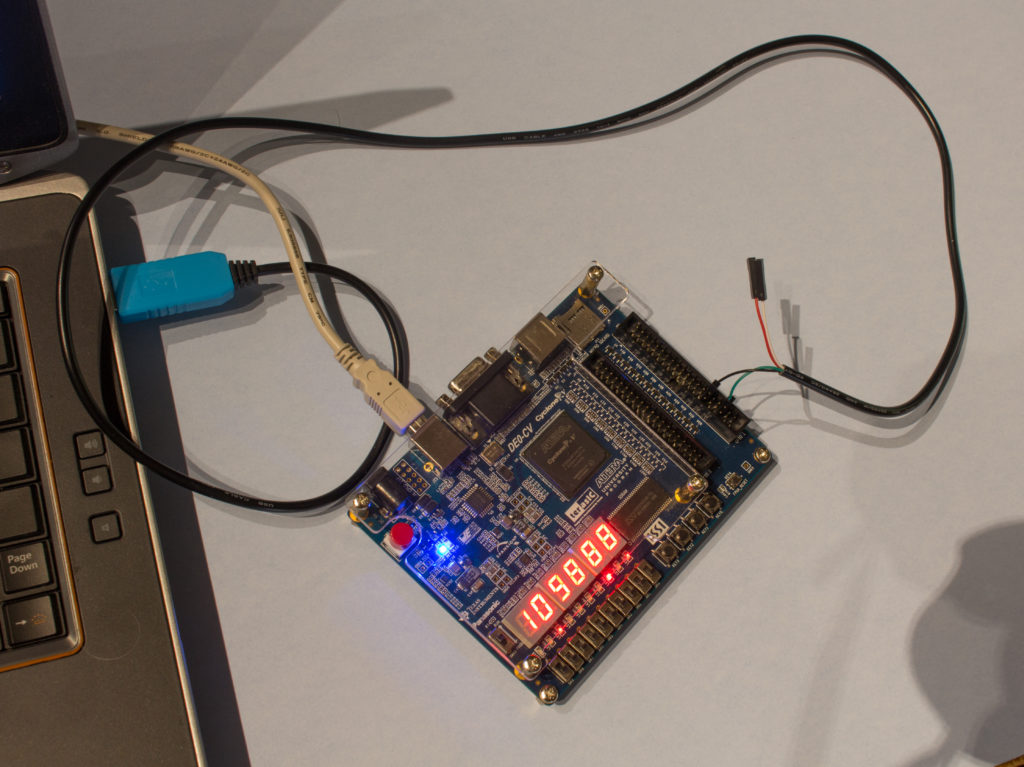

بعد المعرض ، قمت ببرنامج MIPS Open Developer Day مع زملائي من Wave Comnputing. حصلنا على عدد من الأشخاص من بعض الشركات المذكورة أعلاه + أصدقائي الروس من

VivEng ، خدمات تصميم الإشارة المختلطة في سيليكون فالي في كاليفورنيا والتي كان لها أيضًا بعض العملاء في Zelenograd ، وادي السيليكون الروسي. أولاً قدمنا

عرضًا تقديميًا ، ثم قام المشاركون ببعض التمارين على لوحات Digilent Nexys4 DDR و Terasic DE10-Lite FPGA.

ثم ، مع زملائي ، قمت بإجراء الندوة المفتوحة لبرنامج MIPS. وقد حضره رفاق من بعض الشركات الموصوفة ، بما في ذلك تلك التي ترخص أدوات FPGA و EDA المضمنة ، وتبيع الخدمات للإنتاج ، وتجري التدريب على التحقق ، كما تصنع الرقائق أيضًا. وكذلك أصدقائي القدامى من الشركة الروسية

VivEng . عرضت أنا وزملائي

هذه الشرائح ، وبعدها جرب المشاركون أمثلة على FPGAs Digilent Nexys4 DDR و Terasic DE10-Lite.

لتكرار النتائج ، يمكنك تنزيل ودمج حزمتين:

إذا كنت ترغب في إعادة إنتاج النتائج ، يمكنك القيام بما يلي:

- انتقل إلى https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started- Guide .

- قم بتنزيل الحزمة 2.0 MIPSfpga القياسية.

- انتقل إلى https://github.com/MIPSfpga/mipsfpga-plus .

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- انسخ ملفات RTL الأساسية من حزمة MIPS افتح حزمة FPGA إلى دليل فرعي أساسي لحزمة MIPSfpga + - انظر التعليمات الواردة في https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

يجب تثبيت Intel FPGA Quartus Prime Lite Edition أو Xilinx Vivado ، بالإضافة إلى Codescape GCC Bare Metal Toolchain على جهاز الكمبيوتر الخاص بك. بعد ذلك ، يمكنك اتباع التعليمات من الشرائح:

أنت بحاجة إلى تثبيت Intel FPGA Quartus Prime Lite Edition أو Xilinx Vivado على نظامك ، وكذلك Codescape GCC Bare Metal Toolchain. بعد ذلك ، يمكنك اتباع التعليمات من الشرائح:

- cd your_git_directory / boards / board_directory (على سبيل المثال de10_lite أو nexys4_ddr)

- جعل كل الحمل

- اضغط على إعادة التعيين (أو KEY 0 في بعض اللوحات) لإعادة ضبط المعالج.

- يجب أن يبدأ البرنامج hardcoded الافتراضي في العمل.

- cd your_git_directory / program / 00_counter (أو برنامج آخر)

- جعل البرنامج srecord uart

- إذا كان الكمبيوتر يستخدم اتصالًا تسلسليًا غير ttyUSB0 (الافتراضي) ، فقم بما يلي:

- جعل البرنامج srecord uart UART = 1 (أو 2 ، 3 ، إلخ)

- البرنامج الذي تم تحميله عبر USB إلى UART قيد التشغيل الآن.

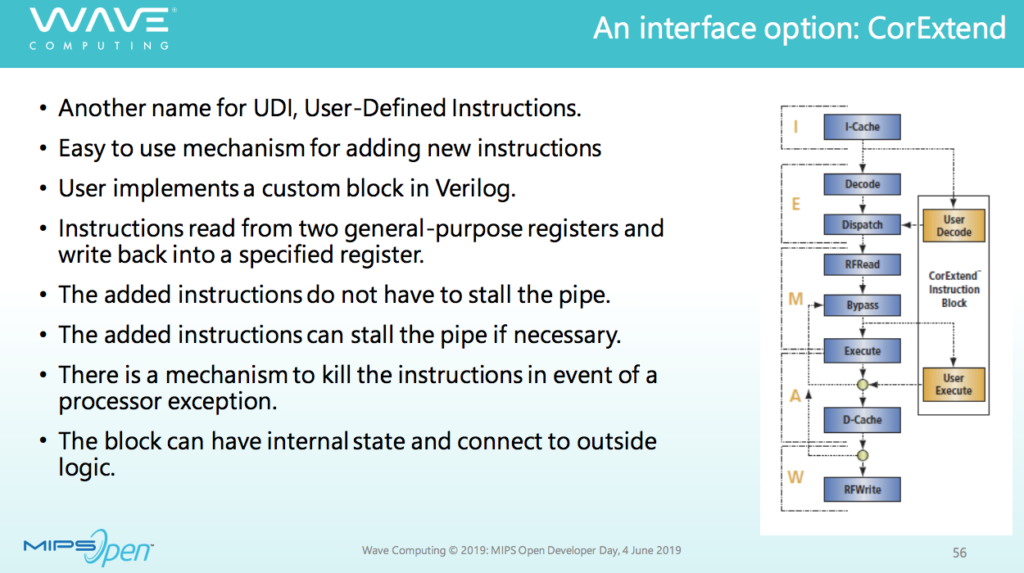

في العرض التقديمي ، أوضحت كيفية تضمين كتلة في المعالج تقوم بفك تشفير وتنفيذ التعليمات الإضافية للنظام الرئيسي للأوامر التي يمكن أن يحددها مصمم النظام على شريحة. يمكن تصنيع الكتلة وتصبح جزءًا من الدائرة الصغيرة أو تكوينها في FPGA / FPGA.

تعليمات إضافية تتحرك على طول خط أنابيب المعالج جنبا إلى جنب مع الرئيسية. تلقي البيانات من السجلات العامة مرئية للمبرمج ويمكن إرجاع النتيجة إلى السجل. يمكن لهذه الإرشادات أيضًا حفظ بعض الحالات في المعالج الثانوي. يمكن قتلهم عن طريق استثناءات في حالة حدوث استثناء ، على سبيل المثال ، في خط الأنابيب باتباع هذه التعليمات:

يحتوي العرض التقديمي على شرح مفصل ، كيفية إضافة إرشادات المعالجات المعرفة من قبل المستخدم إلى MIPS microAptiv UP core core وتوليفها مع بعض SoC البسيطة للوحة FPGA:

مقتطف شفرة Verilog للأجهزة من نص العينة. ينفذ هذا الرمز ، على مستوى نقل السجل (RTL) ، تعليمة متخصصة لحساب شبكة عصبية تلافيفية:

جزء من وحدة نمطية CorExtend مخصصة تنفذ تعليمات معرفة من قبل المستخدم (UDI) لحالة خاصة من حساب net العصبي:

غداً ، أسافر إلى روسيا للمساعدة في ندوة أخرى ، ليس للمهنيين الإلكترونيين وموظفي جمعية الإمارات للغوص ، ولكن للأطفال المهتمين باستكشاف مهن في التصميم الرقمي الإلكتروني الصغير. في هذه الرحلة ، قمتُ بإنشاء معالج فيديو بسيط ثنائي الأبعاد مدمج مع MIPS Open FPGA core ، بالإضافة إلى مثال على لعبة الأجهزة فقط (بدون وحدة المعالجة المركزية (CPU) أو البرامج) لنظام VGA. يحب الأطفال الألعاب وسأستخدم تصميم اللعبة لتعليمهم أساسيات منهجية RTL:

وفي يوم الاثنين القادم

، 8 يوليو ، سوف أدرس أساسيات تطوير الدوائر الرقمية لأطفال المدارس في زيلينوغراد .

بالنسبة له ، كتبت أمثلة على تنفيذ رسومات العفريت البسيطة على FPGA. دائرة توليفها من verilogue توجه العفاريت على شاشة VGA.

فيما يلي مثال عملي في جهاز نظيف (

أكواد المصدر على جيثب ). نوع من القتال البحري ، حيث يبحث قمر صناعي طوربيد أحمر عن صليب أزرق معاد:

وهنا مثال على مزيج من الأجهزة والبرامج - تحية من العفاريت.

جزء الأجهزة والجزء البرمجيات :

نعم ، وعدت بإلقاء خطبي في لاس فيجاس. هنا قطعة:

منظر لقطاع لاس فيجاس عند حلول الظلام ، لكن لا توجد حشود حتى الآن:

ومنظر الشارع على الشريط ، عندما يكون المساء بالفعل ، ولكن لا توجد حشود حتى الآن:

خلال يومين في لاس فيجاس ، لم تتح لي فرصة للمقامرة ، لذا لعبت بمبلغ دولار واحد عندما كانت طائرتنا العائدة إلى سان خوسيه على متن طائرة في مطار لاس فيجاس:

طوال هذا الوقت ، لم ألعب أبداً في لاس فيجاس ، لأنني تجولت في المعرض وتحدثت عن مواضيع إلكترونية ، ثم عقدت ندوة. ولكن أثناء ركوب الطائرة ، لاحظت مع ذلك خسارة دولار واحد: