توضح هذه المقالة تثبيت واستخدام البرامج المجانية لنمذجة الدوائر المنطقية الرقمية في فيريلوج كبديل للمنتجات التجارية Incisve من Cadense و ModelSim من MentorGraphics. مقارنة بين المحاكاة في ModelSim و Verilator. كما سيتم النظر في منهجية التحقق العالمية ، UVM.

SystemC UVM تثبيت البرامج

1. المزيل

إحدى لغات وصف الأجهزة هي فيريلوج. يمكنك كتابة وحدة نمطية بهذه اللغة.

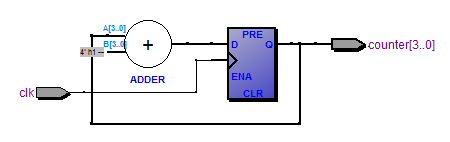

على سبيل المثال ، هناك مخطط العداد:

سيبدو الرمز الخاص به كما يلي:

reg [3:0]counter; always @(posedge clk or posedge reset) if(reset) counter <= 4'd0; else counter <= counter + 1'd1;

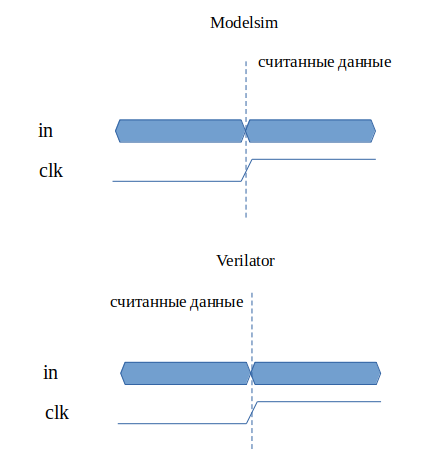

بعد المحاكاة ، نحصل على الطول الموجي:

يمكن ملاحظة أن القيمة التالية ، أكثر من القيمة السابقة ، سيتم كتابتها إلى سجلات العدادات على طول جبهة تردد الساعة.

يمكن أن تحتوي الوحدة النمطية المكتوبة على بنية أكثر تعقيدًا ، وسيكون من الصعب التحقق يدويًا من جميع حالات. سنحتاج الاختبار الآلي. لهذا ، من الضروري تطوير بيئة اختبار بإحدى لغات البرمجة. ستمنحنا بيئة الاختبار الفرصة لإجراء فحص وظيفي كامل للجهاز.

لاختبار رمز المشروع ، بالإضافة إلى لغات مثل Verilog و SystemVerilog و Python (لنماذج الكتابة) ، يمكنك استخدام لغة

SystemC . SystemC هي لغة تصميم وتحقق على مستوى النظام للنماذج على مستوى النظام يتم تنفيذها كمكتبة مفتوحة المصدر لـ C ++.

إحدى طرق التحقق من وحدات Verilog باستخدام SystemC هي ترجمة ملفات verilog إلى C ++. ساعدنا في هذا Verilator.

Verilator هو أسرع جهاز محاكاة Verilog HDL والذي يتجاوز معظم أجهزة المحاكاة التجارية. يقوم Verilator بتجميع SystemVerilog الذي تم توليفه (عادة لا يكون هذا رمز اختبار) ، وكذلك بعض عبارات SystemVerilog و Synthesis في كود C ++ أو SystemC واحد أو متعدد الخيوط. تم تصميم Verilator للمشاريع الكبيرة التي يكون فيها أداء المحاكاة أمرًا بالغ الأهمية وهو مناسب بشكل خاص لإنشاء نماذج للمعالجات القابلة للتنفيذ لفرق تطوير البرامج المدمجة. يستخدم Verilator لمحاكاة العديد من تصميمات العبّارات الكبيرة للغاية والتي تقدر بعدة ملايين من الدولارات مع الآلاف من الوحدات ، ويدعمه العديد من مزودي تقنية IP ، بما في ذلك IP from Arm وجميع مزودي خدمة RISC-V IP الشهير.

قد لا يكون Verilator هو الخيار الأفضل إذا كنت تتوقع استبدالًا كامل الميزات لـ NC-Verilog أو VCS أو محاكي Verilog تجاري آخر أو محاكي سلوكيات Verilog لمشروع صغير جدًا. ومع ذلك ، إذا كنت تبحث عن طريقة لمنفذ Verilog إلى C ++ أو SystemC ، وكان فريقك حرًا في كتابة رمز C ++ فقط ، فهذا مترجم Verilog مجاني لك.

لتثبيت أحدث إصدار على أوبونتو: قم بتنزيل الأرشيف

من الرابط من الموقع الرسمي .

تعيين:

2. موجة GTK

GTKWave هو عارض شكل كامل الميزات ويسمح لك أيضًا بتحويل الملفات من تنسيق vcd إلى fst ، وهو أكثر ملاءمة وأسرع.

تعيين:

sudo apt-get install gtkwave

3. النظام

لغة لتصميم نماذج على مستوى النظام والتحقق منها يتم تنفيذها في شكل مكتبة C ++ مفتوحة المصدر.

كما ذكرنا سابقًا ، يدعم verilator systemc ، لذلك تحتاج إلى إنشاء مشروع يتم فيه وصف معيار الاختبار على systemc ، والملفات المصدر على verilog المركب. للقيام بذلك ، نحتاج إلى مكتبات مترجم g ++ التي تقدمها Accelera. Accellera Systems Initiative هي منظمة مستقلة غير ربحية مكرسة لإنشاء ودعم وتعزيز وترويج معايير التصميم على مستوى النظام والمحاكاة والتحقق للاستخدام في صناعة الإلكترونيات العالمية.

قم بتنزيل الأرشيف:

http://accellera.org/images/downloads/standards/systemc/systemc-2.3.1a.tar.gzتعيين:

tar -xvf systemc-2.3.1a.tar.gz cd systemc-2.3.1a mkdir objdir sudo ./configure --prefix=/usr/local/systemc-2.3.1a/ sudo make sudo make install cd ../

4. UVM ل SYSTEMC

ستستعرض هذه المقالة مشروعًا يقوم بتنفيذ أدوات التحقق من UVM. التحقق هو تأكيد لمطابقة المنتج النهائي مع المتطلبات المرجعية المحددة مسبقًا. يمكن أن تكون إحدى أدوات التحقق الخاصة بها بمثابة اختبارات. لتشغيل تسلسلات الاختبار على نماذج من الأجهزة الحقيقية على مستوى أوصاف RTL ، من الضروري تطوير بيئة اختبار.

UVM - (منهجية التحقق العالمي) هي منهجية تحقق عالمية ، وهي معيار يتيح التطوير وإعادة الاستخدام الفعال لبيئات التحقق من صحة كتلة IP. UVM هي منهجية تحقق تشمل مهامها تنظيم بيئة فعالة حول الوحدة قيد الاختبار. مزاياه:

- هيكل واضح في شكل كتل مخصصة تحديد محددة

- الأهداف؛

- القدرة على إعادة استخدام الكتل في المشاريع اللاحقة ؛

- أقصى أتمتة ممكنة للتحقق ؛

- معلومات الإبلاغ الأكثر اكتمالا التي تسمح ، عند حدوث خطأ ، بتحديد أسبابها بأسرع ما يمكن وبدقة واقتراح الحلول.

تتكون منهجيات UVM من جزأين: مجموعة من القواعد لبناء بيئة اختبار ومكتبة للفراغات الكتلية للتحقق منها ، على سبيل المثال ، مولد نص ، جامع إحصائيات ، إلخ. تتمثل الميزة الرئيسية لـ UVM في تعدد الاستخدامات والتوافق مع بيئات الجهات الخارجية.

نظرًا لأن systemc يدعم منهجية UVM ، دعنا ننتقل إلى تثبيت المكتبات اللازمة.

قم بتنزيل الأرشيف:

https://www.accellera.org/images/downloads/drafts-review/uvm-systemc-1.0-beta2.tar.gzتعيين:

tar -xvf uvm-systemc-1.0-beta2.tar.gz cd uvm-systemc-1.0-beta2/ mkdir objdir sudo ./configure --prefix=/usr/local/systemc_uvm/ --with-systemc=/usr/local/systemc-2.3.1a sudo make sudo make install

نخلق تحالفًا:

sudo mkdir /usr/local/uvm_systemc_aliance

انسخ محتويات المجلدين / usr / local / uvm_systemc_aliance / و /usr/local/systemc-2.3.1/ إلى هذا المجلد

قم بتنزيل المشروع النهائي على الرابط:

https://github.com/paprikun/SYSTEMC/افتح المجلد أمثلة verilator.

يحتوي مجلد rtl على وصف للجهاز. في هذا المثال ، إنه جهاز تحكم PWM.

في ملف sim مجلد makefile لبناء المشروع.

في مجلد السل هو رمز المدقق. يحتوي المجلد tb / uvm على مثال لبيئة uvm. الملف الرئيسي هو نقطة دخول في الاختبار ؛ فهو يربط الجهاز قيد الاختبار ببيئة uvm.

نحن نحاول إنشاء المشروع من مجلد sim باستخدام الأمر make all. نرى خطأ:

/usr/local/uvm_systemc_aliance//include/systemc.h:120:16: error: 'std::gets' has not been declared using std::gets;

نقوم بإصلاحه عن طريق استبدال السطر 120:

#if defined(__cplusplus) && (__cplusplus < 201103L) using std::gets; #endif

مرة أخرى ، نحاول تشغيل testbench وتعثر عند التحذير:

/usr/local/uvm_systemc_aliance//include/sysc/packages/boost/get_pointer.hpp:21:40: warning: 'template<class> class std::auto_ptr' is deprecated [-Wdeprecated-declarations] template<class T> T * get_pointer(std::auto_ptr<T> const& p)

تغيير auto_ptr إلى unique_ptr.

مشروع التجميع والمحاكاة

الآن بعد أن تم تثبيت المكتبات وتشغيلها ، نقوم ببناء المشروع: اجعل الكل. يجب أن يظهر الملف القابل للتنفيذ simu في مجلد sim. هذا كائن تم إنشاؤه بواسطة برنامج التحويل البرمجي. نبدأ ذلك مع فريق ./simu. يجب أن يظهر التالي:

SystemC 2.3.1-Accellera --- Jun 28 2019 11:39:29 Copyright (c) 1996-2014 by all Contributors, ALL RIGHTS RESERVED Universal Verification Methodology for SystemC (UVM-SystemC) Version: 1.0-beta2 Date: 2018-10-24 Copyright (c) 2006 - 2018 by all Contributors See NOTICE file for all Contributors ALL RIGHTS RESERVED Licensed under the Apache License, Version 2.0 UVM_INFO @ 0 s: reporter [RNTST] Running test ... simulation real time = 9 sec UVM_INFO uvm_default_report_server.cpp(666) @ 179490249010 ps: reporter [UVM/REPORT/SERVER] --- UVM Report Summary --- ** Report counts by severity UVM_INFO : 1 UVM_WARNING : 0 UVM_ERROR : 0 UVM_FATAL : 0 ** Report counts by id [RNTST] 1 UVM_INFO @ 179490249010 ps: reporter [FINISH] UVM-SystemC phasing completed; simulation finished

عند انتهاء المحاكاة ، ينتهي تسجيل wafeform. يمكن فتح ملف simu.vcd باستخدام gtkwave:

لعرض الإشارات على اليسار ، حدد SystemC ، ثم اضغط على مفتاح Shift وحدد أي إشارات ، وانقر فوق "إلحاق". تظهر تلميحات الأدوات على شريط الأدوات عند التمرير. التمرير الماوس يعمل ، تحتاج إلى الاستمرار في التحول أو cntrl.

هناك أيضًا طرق لتحويل هذا الملف إلى ملف أصغر آخر.

إذا كان هناك modelsim سوف تفعل التحويل. في المحطة ، أدخل أمر vsim. في الموديلات الطرفية:

vcd2wlf simu.vcd simu.wlf

أو باستخدام gtkwave في محطة لينكس:

vcd2lxt simu.vcd simu.lxt vcd2lxt2 simu.vcd simu.lxt2

لمقارنة وقت المحاكاة ، تم إنشاء مشروع مماثل ، ولكن بالفعل من أجل

Modelsim . نماذج المجلدim_example. بالمثل خلق بيئة UVM. بناء الجملة يشبه على الرغم من أن لغات مختلفة. إذا قمت بتثبيت Modelsim بدعم uvm ، يمكنك تشغيل الأمر make all.

بالإضافة إلى البيئة في كلا المشروعين ، تم إجراء محاكاة في الوقت الفعلي للقياسات.

بمرور الوقت ، ظهر الفرق:

كما ترون من الجدول ، فإن ميزة التحقق هي ميزة. يتم تقديم البيانات لجهاز الكمبيوتر مع 8GB من ذاكرة الوصول العشوائي ، معالج 8 النواة ، 800 ميغاهيرتز ، وتحميل جوهر واحد.

مقارنة حجم الملف:

هنا تفقد أداة التحقق ، ولكن يمكنك تجربة إنشاء أشكال موجية وعمق التتبع ، فترة التسجيل (يمكن تبديل بداية ونهاية تسجيل الموجي). الملف الذي يجب العمل به يرجع إليك.

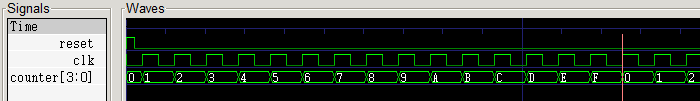

أثناء الاختبار ، بالإضافة إلى وقت المحاكاة نفسها ، تم العثور على تباين في قراءة بيانات الإدخال من الناقل في. إذا تغيرت البيانات من الحافلة في أثناء clk الأمامية ، وقراءة Modelsim البيانات بعد الجبهة ، verilator قبل:

input clk; input [7:0] in; reg [7:0] in_last_ ; ... always @(posedge clk) begin ... in_last_ <= in; ... end

أثناء الاختبار ، يجب أخذ هذه النقطة في الاعتبار ، لأن جزءًا من بيئة الاختبار لمحاكاة مختلفة سيعمل بشكل مختلف.

أيضًا ، لا يأخذ verilator في الاعتبار الحالة "x" للإشارة ويترجم كل شيء إلى "0" ؛

اختبار الأشعة فوق البنفسجية

النظر في بيئة الاختبار ، المجلد tb / uvm.

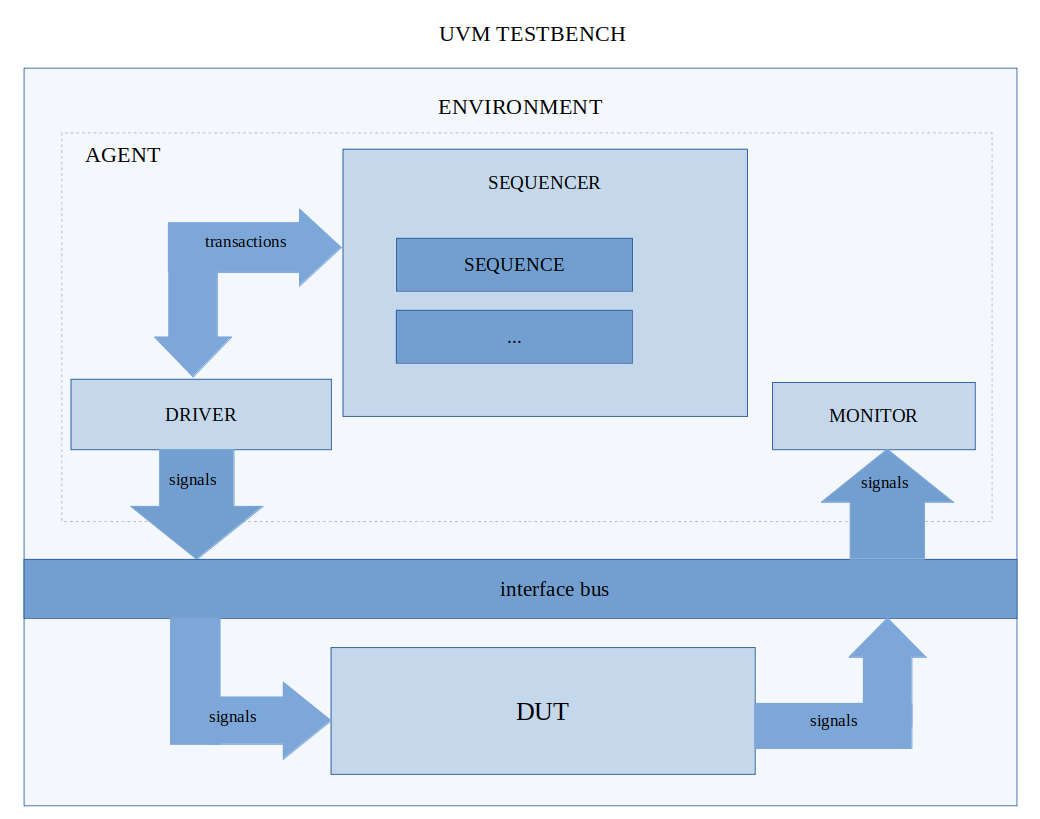

UVM testbench هي البيئة فوق الجهاز. في هذا المثال ، يكون الجهاز وحدة تحكم PWM. مخطط بيئة UVM:

كما ترون في المخطط ، يتكون UVM من كتل (فئات). كل كتلة تؤدي وظائفها. يوضح المثال أحد المخططات المحتملة لبيئة الاختبار. يتوافق اسم ووظائف كل فئة مع الفصل الذي ورثته منه. دعونا نفكر في كل فصل بمزيد من التفصيل.

بيئة ملف env.h أو env.svh. هذه فئة يمكن أن تحتوي على فئة أو أكثر من فئات الوكلاء ، حيث يتم توصيل ثلاث فئات: جهاز التسلسل ، برنامج التشغيل ، جهاز العرض. لا يوجد أي وكيل في المثال ، لكن وظيفته مطبقة في فئة env. للاختبار نحتاج إلى كتابة بعض تسلسل الإجراءات - التسلسل.

دعنا ننتقل إلى رمز بدء التسلسل:

sequence_[n]->start(sqr, NULL);

Sequencer (sequencer) - ملف sequncer.h. في فيريلوج النظام ، اتضح لاستخدام جهاز التسلسل الافتراضي. فئة تحتوي على تسلسل واحد أو أكثر (تسلسل) (ملفات sequence_a.h ، sequence_a.svh). كل تسلسل هو سلسلة من الإجراءات. قد يكون أحد هذه الإجراءات إرسال معاملة. المعاملة - نقل البيانات من فئة إلى أخرى. الفئة التي يتم وصف المعاملات بها هي bus_trans. فيما يلي وصف لفئتين ، لكل منها أيديولوجيًا وظائفها الخاصة: برنامج التشغيل والشاشة.

سائق - ملف drv.h ، drv.svh. فئة تتلقى معاملات من جهاز تسلسل وترجمتها إلى إشارات. يعمل السائق كمساعد جهاز التسلسل بمستوى أقل. النظر في إرسال حزمة واحدة.

يفتح Sequence نافذة معاملة ، ويكتشف برنامج التشغيل هذا الحدث ويبدأ في تلقي البيانات. التسلسل ينتظر استجابة من السائق. يحاكي برنامج التشغيل إشارات الجهاز ، ثم يشير إلى جهاز التسلسل بأنه يمكن إغلاق النافذة. الفكرة هي أن جهاز التسلسل يعمل على مستوى عالٍ ، وأن السائق في مستوى أدنى.

يتم توصيل الإشارات عبر ناقل واجهة الجهاز. يتم وصف الواجهة في الملفات vip_if.h ، vip_if.svh.

بعد ذلك ، تحتاج إلى التحقق مما إذا كانت إشارات الإخراج تتطابق مع الإشارات المتوقعة. هناك حلان:

- كتابة نموذج للجهاز

- التحقق من إشارة من خلال وكيل UVM

في المثال ، يعتبر الخيار الثاني. لاختبار الجهاز على المستوى الوظيفي ، من الضروري مقارنة الإخراج مع المتوقع. كان متطلب الجهاز هو صحة دورة واجب الإشارة المحددة وفترة الإشارة. لمراقبة إشارات الإخراج ، تتم كتابة فئة جديدة - مراقب (ملف monitor.h ، monitor.svh). عادة ، في بيئة اختبار ، تقوم الشاشة بنقل الإشارات في المعاملة (إلى مستوى أعلى) ويتم إرسالها إلى لوحة المقارنة من فئة المقارنة.

في هذا المثال ، يتم فحص الإشارات على الفور. في حالة وجود تعارض بين القيمة المتوقعة والقياس ، يتوقف الاختبار.