التين. مأخوذة من www.extremetech.com/wp-content/uploads/2016/07/MegaProcessor-Feature.jpg

التين. مأخوذة من www.extremetech.com/wp-content/uploads/2016/07/MegaProcessor-Feature.jpgصحة جيدة للجميع!

في مقالة سابقة ، درست مسألة الوصول إلى سجلات متحكم مع كورتيكسم كور في سي + + وأظهرت حلولاً بسيطة لبعض المشاكل.

أريد اليوم أن أوضح فكرة عن كيفية جعل الوصول إلى السجل وحقوله آمنًا دون التضحية بالكفاءة ، وذلك باستخدام فئات C ++ التي تم إنشاؤها من ملفات SVD.

كل من يهمك الأمر ، مرحبا بكم في القط. سيكون هناك الكثير من التعليمات البرمجية.

مقدمة

في مقالة

C ++ Hardware Access Access Redux ، أوضح كين سميث كيفية العمل بأمان وكفاءة مع السجلات ، وحتى أظهرها مع

github.com/kensmith/cppmmio كمثال.

ثم طور العديد من الأشخاص هذه الفكرة ، على سبيل المثال ، قام

Niklas Hauser بإجراء مراجعة رائعة واقترح عدة طرق أخرى للوصول إلى السجلات بأمان.

لقد تم بالفعل تنفيذ بعض هذه الأفكار في مكتبات مختلفة ، وخاصة في

المودم . من أجل الخير ، يمكنك استخدام كل هذه الجمل في الحياة الحقيقية. ولكن في وقت تطوير هذه المكتبات ، بدأت توحد الأوصاف الطرفية والسجلات لتوحيدها ، وبالتالي تم القيام ببعض الأشياء بهدف أن يكون العمل الرئيسي في وصف السجلات مع المبرمج. أيضا ، بعض الحلول ليست فعالة من حيث الكود وموارد متحكم.

اليوم ، توفر كل شركة تصنيع متحكم ARM وصفًا لجميع السجلات بتنسيق SVD. يمكن إنشاء ملفات الرأس من هذه الأوصاف ؛ لذلك ، لا يمكن إنشاء وصف بسيط للسجلات ، بل وصف أكثر تعقيدًا ، ولكن في نفس الوقت ، مما سيزيد من موثوقية الكود. ومن الرائع أن يكون ملف الإخراج بأي لغة أو لغة C أو C ++ أو حتى

Dلكن لنأخذ الأمر بترتيب الوصول الآمن إلى السجلات ، ولماذا يعد ضروريًا على الإطلاق. يمكن عرض التفسير على أمثلة اصطناعية بسيطة ، على الأرجح غير محتملة ، ولكن من الممكن حدوثها تمامًا:

int main(void) {

كل هذه الحالات ممكنة في الممارسة العملية ، وأنا بالتأكيد شاهدت شيئًا كهذا من طلابي. سيكون أمرا رائعا إذا أمكنك أن تمنع ارتكاب مثل هذه الأخطاء.

يبدو لي أيضًا أنه أكثر متعة عندما يبدو الرمز أنيقًا ولا يحتاج إلى تعليقات. على سبيل المثال ، حتى لو كنت تعرف متحكم STM32F411 جيدًا ، فليس من الممكن دائمًا فهم ما يحدث في هذا الرمز:

int main() { uint32 temp = GPIOA->OSPEEDR ; temp &=~ GPIO_OSPEEDR_OSPEED0_Msk ; temp = (GPIO_OSPEEDR_OSPEED0_0 | GPIO_OSPEEDR_OSPEED0_1) ; GPIOA->OSPEEDR = temp; }

لا تعليق هنا لا يمكن القيام به. يعين الرمز تردد تشغيل منفذ GPIOA.0 إلى الحد الأقصى (توضيح من

mctMaks : في الواقع ، تؤثر هذه المعلمة على وقت صعود المقدمة (بمعنى ، درجة انحدارها) ، وتعني أنه يمكن للمنفذ معالجة إشارة رقمية بشكل طبيعي عند إشارة معينة (VeryLow \ Low \ Medium \ عالية) التردد).

دعونا نحاول التخلص من هذه العيوب.

سجل التجريد

بادئ ذي بدء ، تحتاج إلى معرفة ما هو السجل من وجهة نظر المبرمج والبرنامج.

يحتوي السجل على عنوان أو طول أو حجم وطريقة وصول: يمكن كتابة بعض السجلات والبعض الآخر يمكن قراءتها فقط ويمكن قراءة معظمها وكتابتها.

بالإضافة إلى ذلك ، يمكن تمثيل السجل كمجموعة من الحقول. يمكن أن يتكون الحقل من بت واحد أو عدة بتات ويقع في أي مكان في السجل.

لذلك ، فإن خصائص الحقل التالية مهمة بالنسبة لنا: الطول أو الحجم (

العرض أو

الحجم ) ، الإزاحة من بداية التسجيل (

الإزاحة ) ، والقيمة.

قيم الحقول هي مساحة لكل الكميات الممكنة التي يمكن أن يأخذها الحقل ويعتمد ذلك على طول الحقل. أي إذا كان الحقل بطول 2 ، فهناك 4 قيم حقل ممكنة (0،1،2،3). مثل السجل ، تحتوي الحقول وقيم الحقل على وضع وصول (قراءة وكتابة وقراءة وكتابة)

لجعلها أكثر وضوحًا ، دعنا نأخذ سجل TIM1 CR1 من متحكم STM32F411. بشكل تخطيطي ، يبدو كما يلي:

- بت 0 CEN: تمكين عداد

0: تمكين العداد: تعطيل

1: عداد: تمكين

- UDIS بت 1: تمكين / تعطيل حدث UEV

0: تم تمكين حدث UEV: تمكين

1: حدث خارج UEV: تعطيل

- بت URS 2: حدد مصادر توليد أحداث UEV

0: يتم إنشاء UEV عندما تفيض أو عند تعيين UG: أي بت

1: يتم إنشاء UEV فقط على تجاوز السعة : تجاوز السعة

- بت 3 OPM: تشغيل مرة واحدة

0: يستمر الموقت في الاعتماد أكثر بعد الحدث UEV: ContinueAfterUEV

1: توقف الموقت بعد الحدث UEV : StopAfterUEV

- بت 4 DIR: اتجاه العد

0: الحساب المباشر: Upcounter

1: العد التنازلي : Downcounter

- بت 6: 5 سم: وضع المحاذاة

0: وضع المحاذاة 0: CenterAlignedMode0

1: وضع المحاذاة 1: CenterAlignedMode1

2: وضع المحاذاة 2: CenterAlignedMode2

3: وضع المحاذاة 3: CenterAlignedMode3

- بت 7 APRE: وضع التحميل المسبق لتسجيل ARR

0: لا يتم تخزين سجل TIMx_ARR مؤقتًا: ARRNotBuffered

1: لا يتم تخزين سجل TIMx_ARR مؤقتًا: ARRBuffered

- بت 8: 9 كد: مقسم الساعة

0: tDTS = tCK_INT: ClockDevidedBy1

1: tDTS = 2 * tCK_INT: ClockDevidedBy2

2: tDTS = 4 * tCK_INT: ClockDevidedBy4

3: محفوظة: محفوظة

هنا ، على سبيل المثال ، CEN هو حقل 1 بت مع إزاحة 0 نسبة إلى بداية التسجيل. و

Enable (1) و

Disable (0) هما قيمتهما الممكنة.

لن نركز على ما يتحمله كل حقل في هذا السجل بشكل خاص ، من المهم بالنسبة لنا أن يكون لكل حقل وحقل قيمة اسم يحمل معنى دلاليًا ويمكن من خلاله فهم ما يقوم به من حيث المبدأ.

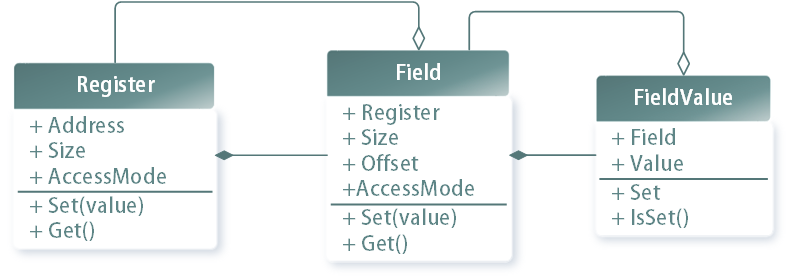

يجب أن يكون لدينا حق الوصول إلى كل من السجل والميدان وقيمته. لذلك ، في شكل تقريبي للغاية ، يمكن تمثيل تجريد السجل بالفئات التالية:

بالإضافة إلى الفصول الدراسية ، من المهم أيضًا أن يكون للسجلات والحقول الفردية خصائص معينة أو أن السجل له عنوان أو حجم أو وضع وصول (للقراءة فقط أو للكتابة فقط أو كلاهما).

يحتوي الحقل على الحجم والإزاحة ووضع الوصول أيضًا. بالإضافة إلى ذلك ، يجب أن يحتوي الحقل على رابط إلى السجل الذي ينتمي إليه.

يجب أن تحتوي قيمة الحقل على ارتباط إلى الحقل وسمة إضافية - القيمة.

لذلك ، في إصدار أكثر تفصيلاً ، سيبدو التجريد لدينا كما يلي:

بالإضافة إلى السمات ، يجب أن يكون لدينا التجريد أساليب التعديل والوصول. للبساطة ، نحن نقتصر على طرق التثبيت / الكتابة والقراءة.

عندما قررنا تجريد الحالة ، نحتاج إلى التحقق من توافق هذا التجريد مع ما هو موصوف في ملف SVD.

عرض وصف النظام (SVD) ملف

تنسيق وصف العرض التقديمي لنظام CMSIS (CMSIS-SVD) هو وصف رسمي لسجلات متحكم يعتمد على معالج ARM Cortex-M. المعلومات الواردة في أوصاف تمثيل النظام ، يتوافق عمليا مع البيانات الموجودة في الأدلة المرجعية للأجهزة. يمكن أن يحتوي وصف السجلات في مثل هذا الملف على معلومات رفيعة المستوى والغرض من جزء واحد فقط من الحقل في السجل.

من الناحية التخطيطية ، يمكن وصف مستويات تفاصيل المعلومات في مثل هذا الملف من خلال المخطط التالي ، الذي تم

اتخاذه على موقع Keil :

يتم توفير ملفات SVD الوصف من قبل الشركات المصنعة ويتم استخدامها أثناء تصحيح الأخطاء لعرض معلومات حول متحكم وسجلات. على سبيل المثال ، يستخدمهم IAR لعرض المعلومات في لوحة View-> Registers. الملفات نفسها موجودة في المجلد Program Files (x86) \ IAR Systems \ Embedded Workbench 8.3 \ arm \ config \ debugger.

يستخدم Clion من JetBrains أيضًا ملفات svd لعرض معلومات التسجيل أثناء تصحيح الأخطاء.

يمكنك دائمًا تنزيل الأوصاف من مواقع الشركة المصنعة.

هنا يمكنك أن تأخذ ملف SVD للتحكم الدقيق STM32F411بشكل عام ، تنسيق SVD هو المعيار الذي تدعمه الشركات المصنعة. دعونا نرى ما هي مستويات الوصف في SVD.

في المجموع ، يتم تمييز 5 مستويات ، ومستوى الجهاز ، ومستوى متحكم ، ومستوى التسجيل ، ومستوى الحقل ، ومستوى القيم المذكورة.

- مستوى الجهاز : وصف المستوى العلوي لعرض النظام هو الجهاز. في هذا المستوى ، يتم توضيح الخصائص المتعلقة بالجهاز ككل. على سبيل المثال ، اسم الجهاز أو الوصف أو الإصدار. وحدة الحد الأدنى عنونة ، وكذلك عمق بت ناقل البيانات. يمكن تعيين القيم الافتراضية لسمات السجل ، مثل حجم التسجيل ، وقيمة إعادة التعيين ، وأذونات الوصول ، للجهاز بأكمله في هذا المستوى ، وتكون موروثة ضمنياً بمستويات منخفضة من الوصف.

- مستوى متحكم: يصف قسم وحدة المعالجة المركزية جوهر متحكم وميزاته. هذا القسم مطلوب إذا تم استخدام ملف SVD لإنشاء ملف رأس الجهاز.

- الطبقة المحيطية : الجهاز المحيطي عبارة عن مجموعة مسماة من السجلات. يتم تعيين الجهاز المحيطي إلى عنوان أساسي محدد في مساحة عنوان الجهاز.

- مستوى التسجيل : السجل هو مورد قابل للبرمجة مسمى ينتمي إلى جهاز طرفي. يتم تعيين السجلات إلى عنوان محدد في مساحة عنوان الجهاز. العنوان مرتبط بالعنوان المحيطي الأساسي. أيضا ، للسجل ، يشار إلى وضع الوصول (القراءة / الكتابة).

- مستوى الحقل : كما ذكر أعلاه ، يمكن تقسيم السجلات إلى أجزاء من وظائف مختلفة - الحقول. يحتوي هذا المستوى على أسماء الحقول الفريدة في نفس السجل ، وحجمها ، والإزاحات المتعلقة ببداية السجل ، وكذلك وضع الوصول.

- مستوى قيم الحقول التي تم تعدادها : في الواقع ، يتم تسمية هذه القيم بقيم الحقل التي يمكن استخدامها للراحة في C و C ++ و D وما إلى ذلك.

في الواقع ، ملفات SVD هي ملفات xml عادية مع وصف كامل للنظام. هناك محولات ملفات svd إلى رمز C ، على سبيل المثال

هنا ، والتي تولد رؤوس وهياكل ملائمة لـ C لكل محيط وتسجيل.

يوجد أيضًا محلل

cmsis-svd لملفات SVD مكتوب بلغة Phyton ، وهو يقوم بشيء ما مثل إلغاء تسلسل البيانات من ملف إلى كائنات فئة في Phython ، والتي يتم استخدامها بعد ذلك في برنامج إنشاء الشفرة.

يمكن الاطلاع على مثال لوصف سجل متحكم STM32F411 تحت المفسد:

مثال سجل مؤقت CR1 TIM1 <peripheral> <name>TIM1</name> <description>Advanced-timers</description> <groupName>TIM</groupName> <baseAddress>0x40010000</baseAddress> <addressBlock> <offset>0x0</offset> <size>0x400</size> <usage>registers</usage> </addressBlock> <registers> <register> <name>CR1</name> <displayName>CR1</displayName> <description>control register 1</description> <addressOffset>0x0</addressOffset> <size>0x20</size> <access>read-write</access> <resetValue>0x0000</resetValue> <fields> <field> <name>CKD</name> <description>Clock division</description> <bitOffset>8</bitOffset> <bitWidth>2</bitWidth> </field> <field> <name>ARPE</name> <description>Auto-reload preload enable</description> <bitOffset>7</bitOffset> <bitWidth>1</bitWidth> </field> <field> <name>CMS</name> <description>Center-aligned mode selection</description> <bitOffset>5</bitOffset> <bitWidth>2</bitWidth> </field> <field> <name>DIR</name> <description>Direction</description> <bitOffset>4</bitOffset> <bitWidth>1</bitWidth> </field> <field> <name>OPM</name> <description>One-pulse mode</description> <bitOffset>3</bitOffset> <bitWidth>1</bitWidth> </field> <field> <name>URS</name> <description>Update request source</description> <bitOffset>2</bitOffset> <bitWidth>1</bitWidth> </field> <field> <name>UDIS</name> <description>Update disable</description> <bitOffset>1</bitOffset> <bitWidth>1</bitWidth> </field> <field> <name>CEN</name> <description>Counter enable</description> <bitOffset>0</bitOffset> <bitWidth>1</bitWidth> </field> </fields> </register> <register>

كما ترون ، هناك كل المعلومات اللازمة لتجريدنا ، باستثناء وصف قيم البتات المحددة للحقول.

لا يرغب جميع المصنّعين في قضاء بعض الوقت في وصف كامل لنظامهم ، لذا كما ترى ، لم ترغب ST في وصف قيم الحقول ونقل هذا العبء إلى مبرمجي العملاء. لكن TI تهتم بعملائها وتصف النظام بالكامل ، بما في ذلك أوصاف قيم الحقول.

ما ورد أعلاه يوضح أن تنسيق وصف SVD متوافق جدًا مع تجريد قضيتنا. يحتوي الملف على جميع المعلومات اللازمة من أجل وصف السجل بالكامل.

تطبيق

تسجيل

الآن وبعد أن قمنا بالتجريد من السجل ولدينا وصف للسجلات في شكل ملف svd من الشركات المصنعة التي تتناسب بشكل مثالي مع هذا التجريد ، يمكننا الانتقال مباشرة إلى التنفيذ.

يجب أن يكون تنفيذنا فعالًا مثل رمز C وسهل الاستخدام. أرغب في أن يكون الوصول إلى السجلات واضحًا قدر الإمكان ، على سبيل المثال ، مثل هذا:

if (TIM1::CR1::CKD::DividedBy2::IsSet()) { TIM1::ARR::Set(10_ms) ; TIM1::CR1::CEN::Enable::Set() ; }

تذكر أنه من أجل الوصول إلى عنوان التسجيل الصحيح ، تحتاج إلى استخدام reinterpret_cast:

*reinterpret_cast<volatile uint32_t *>(0x40010000) = (1U << 5U) ;

تم بالفعل وصف فئة السجل أعلاه ، ويجب أن يكون لها عنوان وحجم ووضع وصول ، بالإضافة إلى طريقتين

Get() و

Set() :

نقوم بتمرير العنوان وطول التسجيل ووضع الوصول إلى معلمات القالب (هذه أيضًا فئة). باستخدام آلية

SFINAE ، وهي

enable_if enable_if ، سنقوم بـ "التخلص" من وظائف الوصول

Set() أو

Get() للسجلات التي لا ينبغي أن تدعمها. على سبيل المثال ، إذا كان السجل للقراءة فقط ، فسنقوم

ReadMode نوع

ReadMode إلى معلمة القالب ، وسوف يقوم

enable_if بالتحقق مما إذا كان الوصول هو خليفة

ReadMode وإذا لم يكن الأمر كذلك ، فسيؤدي ذلك إلى إنشاء خطأ محكوم عليه (لن يتم عرض النوع T) ، ولن يتضمن المترجم طريقة

Set() لمثل هذا السجل. الشيء نفسه ينطبق على سجل مخصص للكتابة فقط.

للتحكم في الوصول ، سوف نستخدم الفصول الدراسية:

تأتي السجلات بأحجام مختلفة: 8 ، 16 ، 32 ، 64 بت. لكل منها ، نضع نوعنا:

نوع السجلات حسب الحجم template <uint32_t size> struct RegisterType {} ; template<> struct RegisterType<8> { using Type = uint8_t ; } ; template<> struct RegisterType<16> { using Type = uint16_t ; } ; template<> struct RegisterType<32> { using Type = uint32_t ; } ; template<> struct RegisterType<64> { using Type = uint64_t ; } ;

بعد ذلك ، بالنسبة إلى TIM1 المؤقت ، يمكنك تحديد سجل CR1 ، وعلى سبيل المثال ، سجل EGR بهذه الطريقة:

struct TIM1 { struct CR1 : public RegisterBase<0x40010000, 32, ReadWriteMode> { } struct EGR : public RegisterBase<0x40010014, 32, WriteMode> { } } int main() { TIM1::CR1::Set(10) ; auto reg = TIM1::CR1::Get() ;

نظرًا لأن المحول البرمجي يعرض أسلوب

Get() فقط

ReadMode يتم فيها توريث وضع الوصول من

ReadMode ، وطرق

Set() الخاصة

WriteMode يتم فيها توريث وضع الوصول من

WriteMode ، في حالة الاستخدام غير الصحيح لأساليب الوصول ، ستتلقى خطأ في مرحلة

WriteMode . وإذا كنت تستخدم أدوات التطوير الحديثة ، مثل Clion ، حتى في مرحلة الترميز ، سترى تحذيرًا من محلل الشفرة:

حسنًا ، أصبح الوصول إلى السجلات الآن أكثر أمانًا ، ولا يسمح لك رمزنا بالقيام بأشياء غير مقبولة لهذا السجل ، لكننا نريد المضي قدمًا والإشارة إلى السجل بأكمله ، ولكن إلى حقوله.

الحقول

يحتوي الحقل بدلاً من العنوان على قيمة تحويل نسبة إلى بداية السجل. بالإضافة إلى ذلك ، من أجل معرفة العنوان أو النوع الذي يجب تقديم قيمة الحقل إليه ، يجب أن يكون لديه رابط إلى السجل:

بعد ذلك ، من الممكن بالفعل القيام بالأمور التالية:

struct TIM1 { struct CR1 : public RegisterBase<0x40010000, 32, ReadWriteMode> { using CKD = RegisterField<TIM1::CR1, 8, 2, ReadWriteMode> ; using ARPE = RegisterField<TIM1::CR1, 7, 1, ReadWriteMode> ; using CMS = RegisterField<TIM1::CR1, 5, 2, ReadWriteMode> ; using DIR = RegisterField<TIM1::CR1, 4, 1, ReadWriteMode> ; using OPM = RegisterField<TIM1::CR1, 3, 1, ReadWriteMode> ; using URS = RegisterField<TIM1::CR1, 2, 1, ReadWriteMode> ; using UDIS = RegisterField<TIM1::CR1, 1, 1, ReadWriteMode> ; using CEN = RegisterField<TIM1::CR1, 0, 1, ReadWriteMode> ; } } int main() {

على الرغم من أن كل شيء يبدو جيدًا بشكل عام ، إلا أنه لا يزال غير واضح تمامًا ماذا

TIM1::CR1::CKD::Set(2) ، ماذا يعني

TIM1::CR1::CKD::Set(2) اللذين تم تمريرهما إلى وظيفة

Set() ؟ وماذا يعني الرقم المرتجع بواسطة طريقة

TIM1::CR1::CEN::Get() ؟

الانتقال بسلاسة إلى قيم الحقل.

قيمة الحقل

يعد تجريد قيمة الحقل حقلًا أساسيًا أيضًا ، ولكنه قادر على قبول حالة واحدة فقط. تتم إضافة السمات إلى تجريد الحقل - القيمة الفعلية ورابط إلى الحقل. طريقة

Set() قيمة الحقل مطابقة لطريقة

Set() الحقل ، باستثناء أن القيمة نفسها لا تحتاج إلى أن تنتقل إلى هذه الطريقة ، فهي معروفة مقدمًا ، تحتاج فقط إلى ضبط. لكن أسلوب

Get() لا معنى له ؛ وبدلاً من ذلك ، من الأفضل التحقق مما إذا كانت هذه القيمة محددة أم لا ،

IsSet() هذه الطريقة بأسلوب

IsSet() .

يمكن الآن وصف حقل السجل بمجموعة من قيمه:

تسجل قيم CR1 حقول المؤقت TIM1 template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_CKD_Values: public RegisterField<Reg, offset, size, AccessMode> { using DividedBy1 = FieldValue<TIM_CR_CKD_Values, 0U> ; using DividedBy2 = FieldValue<TIM_CR_CKD_Values, 1U> ; using DividedBy4 = FieldValue<TIM_CR_CKD_Values, 2U> ; using Reserved = FieldValue<TIM_CR_CKD_Values, 3U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_ARPE_Values: public RegisterField<Reg, offset, size, AccessMode> { using ARRNotBuffered = FieldValue<TIM_CR_ARPE_Values, 0U> ; using ARRBuffered = FieldValue<TIM_CR_ARPE_Values, 1U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_CMS_Values: public RegisterField<Reg, offset, size, AccessMode> { using CenterAlignedMode0 = FieldValue<TIM_CR_CMS_Values, 0U> ; using CenterAlignedMode1 = FieldValue<TIM_CR_CMS_Values, 1U> ; using CenterAlignedMode2 = FieldValue<TIM_CR_CMS_Values, 2U> ; using CenterAlignedMode3 = FieldValue<TIM_CR_CMS_Values, 3U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_DIR_Values: public RegisterField<Reg, offset, size, AccessMode> { using Upcounter = FieldValue<TIM_CR_DIR_Values, 0U> ; using Downcounter = FieldValue<TIM_CR_DIR_Values, 1U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_OPM_Values: public RegisterField<Reg, offset, size, AccessMode> { using ContinueAfterUEV = FieldValue<TIM_CR_OPM_Values, 0U> ; using StopAfterUEV = FieldValue<TIM_CR_OPM_Values, 1U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_URS_Values: public RegisterField<Reg, offset, size, AccessMode> { using Any = FieldValue<TIM_CR_URS_Values, 0U> ; using Overflow = FieldValue<TIM_CR_URS_Values, 1U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_UDIS_Values: public RegisterField<Reg, offset, size, AccessMode> { using Enable = FieldValue<TIM_CR_UDIS_Values, 0U> ; using Disable = FieldValue<TIM_CR_UDIS_Values, 1U> ; } ; template <typename Reg, size_t offset, size_t size, typename AccessMode> struct TIM_CR_CEN_Values: public RegisterField<Reg, offset, size, AccessMode> { using Disable = FieldValue<TIM_CR_CEN_Values, 0U> ; using Enable = FieldValue<TIM_CR_CEN_Values, 1U> ; } ;

بعد ذلك ، سيتم بالفعل وصف سجل CR1 نفسه على النحو التالي:

struct TIM1 { struct CR1 : public RegisterBase<0x40010000, 32, ReadWriteMode> { using CKD = TIM_CR1_CKD_Values<TIM1::CR1, 8, 2, ReadWriteMode> ; using ARPE = TIM_CR1_ARPE_Values<TIM1::CR1, 7, 1, ReadWriteMode> ; using CMS = TIM_CR1_CMS_Values<TIM1::CR1, 5, 2, ReadWriteMode> ; using DIR = TIM_CR1_DIR_Values<TIM1::CR1, 4, 1, ReadWriteMode> ; using OPM = TIM_CR1_OPM_Values<TIM1::CR1, 3, 1, ReadWriteMode> ; using URS = TIM_CR1_URS_Values<TIM1::CR1, 2, 1, ReadWriteMode> ; using UDIS = TIM_CR1_UDIS_Values<TIM1::CR1, 1, 1, ReadWriteMode> ; using CEN = TIM_CR1_CEN_Values<TIM1::CR1, 0, 1, ReadWriteMode> ; } ; }

الآن يمكنك تعيين وقراءة قيمة حقل التسجيل مباشرة: على سبيل المثال ، إذا كنت ترغب في تمكين المؤقت على الحساب ، ما عليك سوى الاتصال بالطريقة

Set() على

Enable قيمة الحقل CEN الخاص بالتسجيل CR1 من المؤقت TIM1:

TIM1::CR1::CEN::Enable::Set() ; . في الكود ، سيبدو كما يلي:

int main() { if (TIM1::CR1::CKD::DividedBy2::IsSet()) { TIM1::ARR::Set(100U) ; TIM1::CR1::CEN::Enable::Set() ; } }

للمقارنة ، نفس الشيء باستخدام رأس C: int main() { if((TIM1->CR1 & TIM_CR1_CKD_Msk) == TIM_CR1_CKD_0) { TIM1->ARR = 100U ; regValue = TIM1->CR1 ; regValue &=~(TIM_CR1_CEN_Msk) ; regValue |= TIM_CR1_CEN ; TIM1->CR1 = regValue ; } }

لذلك ، تم إجراء التحسينات الرئيسية ، يمكننا الوصول إلى السجل بطريقة سهلة ومفهومة ومجالاته وقيمه. , , , , .

, . , :

int main() { uint32_t regValue = TIM1->CR1 ; regValue &=~(TIM_CR1_CKD_Msk | TIM_CR1_DIR) ; regValue |= (TIM_CR1_CEN | TIM_CR1_CKD_0 | TIM_CR1_CKD_0) ; TIM1->CR1 = regValue ; }

Set(...) , , . أي :

int main() {

, , , , .

. :

, :

- , .

- .

constexpr , :

Set() IsSet() :

, :

int main() {

, - , , , ,

FieldValueBaseType . ,

FieldValueBaseType :

template<uint32_t address, size_t size, typename AccessMode, typename FieldValueBaseType, typename ...Args> class Register { private:

, SFINAE , , , , , .

CR1 TIM1, :

struct TIM1 { struct TIM1CR1Base {} ; struct CR1 : public RegisterBase<0x40010000, 32, ReadWriteMode> { using CKD = TIM_CR_CKD_Values<TIM1::CR1, 8, 2, ReadWriteMode, TIM1CR1Base> ; using ARPE = TIM_CR_ARPE_Values<TIM1::CR1, 7, 1, ReadWriteMode, TIM1CR1Base> ; using CMS = TIM_CR_CMS_Values<TIM1::CR1, 5, 2, ReadWriteMode, TIM1CR1Base> ; using DIR = TIM_CR_DIR_Values<TIM1::CR1, 4, 1, ReadWriteMode, TIM1CR1Base> ; using OPM = TIM_CR_OPM_Values<TIM1::CR1, 3, 1, ReadWriteMode, TIM1CR1Base> ; using URS = TIM_CR_URS_Values<TIM1::CR1, 2, 1, ReadWriteMode, TIM1CR1Base> ; using UDIS = TIM_CR_UDIS_Values<TIM1::CR1, 1, 1, ReadWriteMode, TIM1CR1Base> ; using CEN = TIM_CR_CEN_Values<TIM1::CR1, 0, 1, ReadWriteMode, TIM1CR1Base> ; } ; }

, , . , , , .

, :

وحاول أن تفعل الشيء نفسه مع النهج الجديد: int main(void) {

في كل حالة من هذه الحالات ، حصلنا على خطأ في مرحلة التجميع ، وهذا بالضبط ما حققناه.حسنًا ، لقد قدمنا وصولاً جميلاً وآمناً إلى السجل ومجالاته ، لكن ماذا عن السرعة؟سرعة

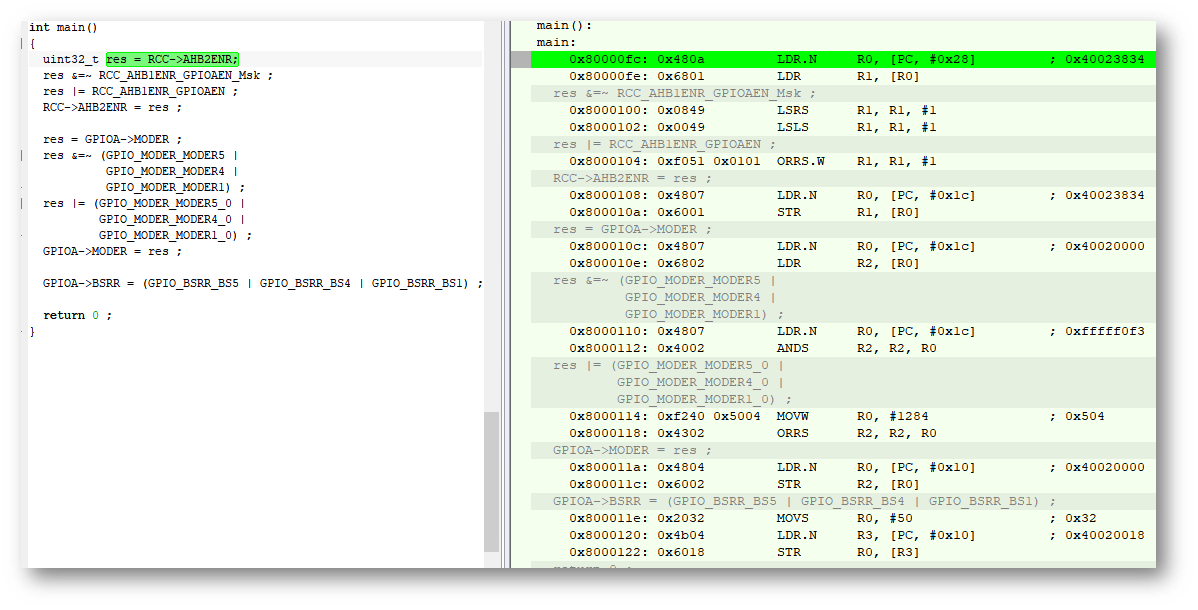

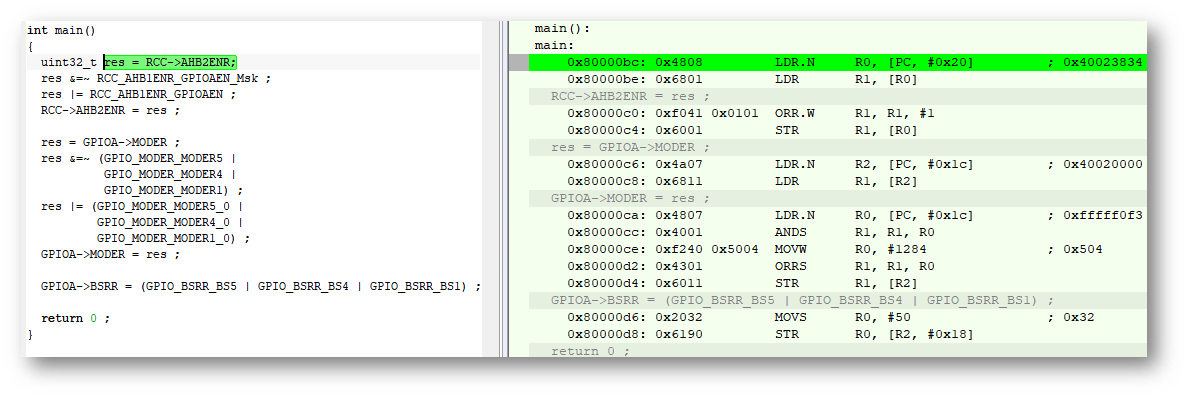

للمقارنة ، كم هو أفضل نهجنا ، سنستخدم كود C و C ++ الذي يغذي الساعة للمنفذ A ، ويضبط المنافذ الثلاثة على وضع الإخراج ، ويعين منافذ الإخراج في هذه المنافذ الثلاثة 1:رمز C: int main() { uint32_t res = RCC->AHB2ENR; res &=~ RCC_AHB1ENR_GPIOAEN_Msk ; res |= RCC_AHB1ENR_GPIOAEN ; RCC->AHB2ENR = res ; res = GPIOA->MODER ; res &=~ (GPIO_MODER_MODER5 | GPIO_MODER_MODER4 | GPIO_MODER_MODER1) ; res |= (GPIO_MODER_MODER5_0 | GPIO_MODER_MODER4_0 | GPIO_MODER_MODER1_0) ; GPIOA->MODER = res ; GPIOA->BSRR = (GPIO_BSRR_BS5 | GPIO_BSRR_BS4 | GPIO_BSRR_BS1) ; return 0 ; }

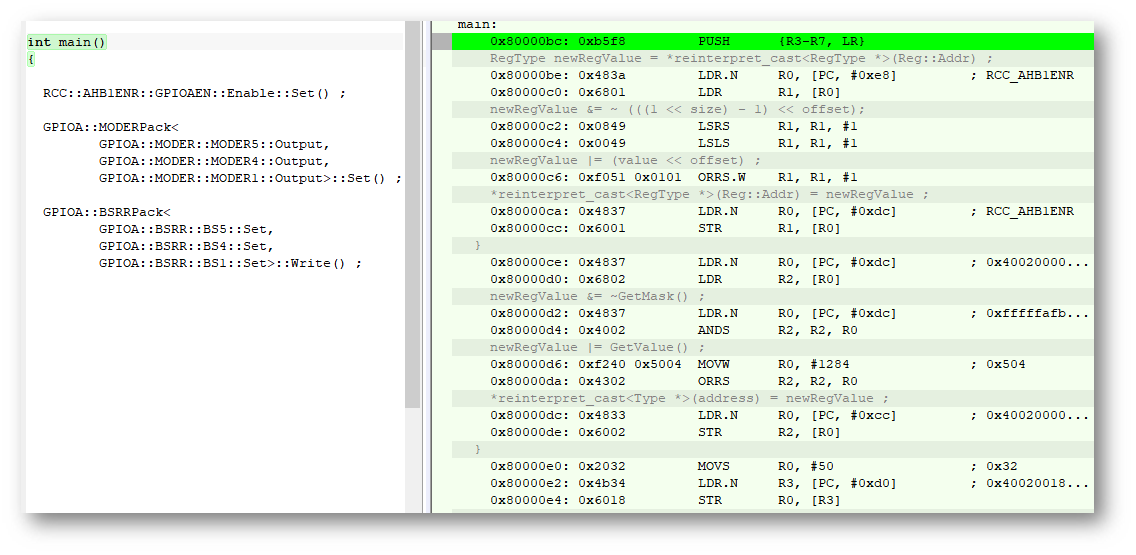

رمز C ++: int main() { RCC::AHB1ENR::GPIOAEN::Enable::Set() ; GPIOA::MODERPack< GPIOA::MODER::MODER5::Output, GPIOA::MODER::MODER4::Output, GPIOA::MODER::MODER1::Output>::Set() ; GPIOA::BSRRPack< GPIOA::BSRR::BS5::Set, GPIOA::BSRR::BS4::Set, GPIOA::BSRR::BS1::Set>::Write() ; return 0 ; }

IAR. : :

:

C++ :

18 , , .

, :

13 .

++ :

: , .

, . , ?

, , . . , . , , . , . SVD , , , .

, , , , enum, . , ,

.

يؤدي

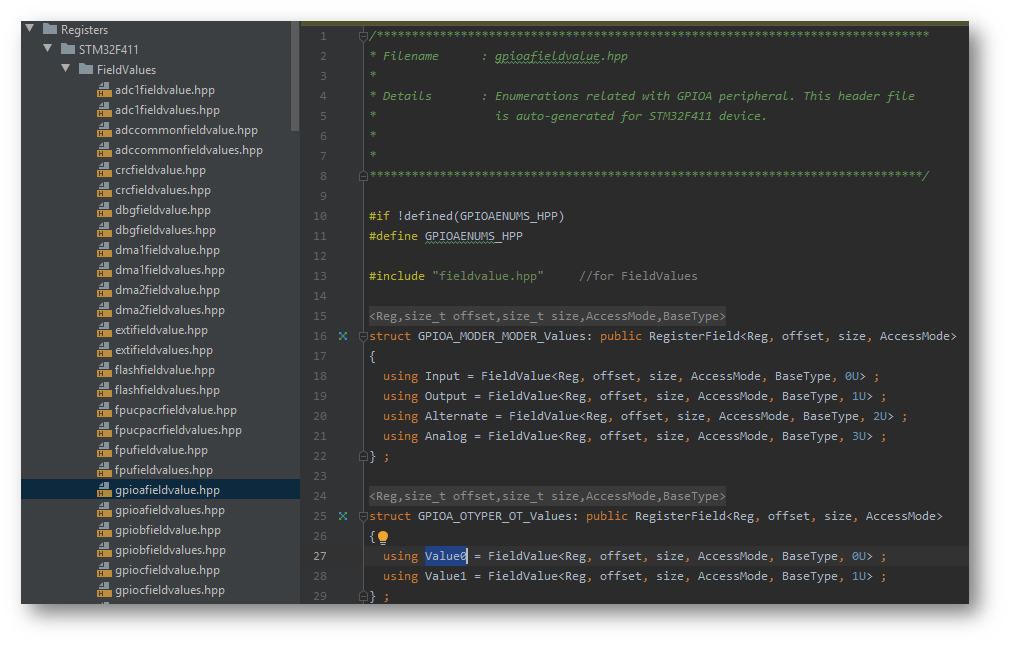

, , . , gpioa rcc, :

#include "gpioaregisters.hpp"

, SVD , , .

, , , SVD , - ST , :

template <typename Reg, size_t offset, size_t size, typename AccessMode, typename BaseType> struct GPIOA_MODER_MODER_Values: public RegisterField<Reg, offset, size, AccessMode> { using Value0 = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 0U> ; using Value1 = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 1U> ; using Value2 = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 2U> ; using Value3 = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 3U> ; } ;

, Value, - :

template <typename Reg, size_t offset, size_t size, typename AccessMode, typename BaseType> struct GPIOA_MODER_MODER_Values: public RegisterField<Reg, offset, size, AccessMode> { using Input = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 0U> ; using Output = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 1U> ; using Alternate = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 2U> ; using Analog = FieldValue<GPIOA_MODER_MODER_Values, BaseType, 3U> ; } ;

.

, ST , 0.

, , enum .

, .

IAR 8.40.1

« Online GDB»PS:

putyavka RegisterField::Get()Ryppka assert.

Typesafe Register Access in C++One Approach to Using Hardware Registers in C++SVD Description (*.svd) Format