تضيف عمليات التصنيع الوسيطة وأنواع مختلفة من الترانزستورات والعديد من الخيارات الأخرى حالة عدم اليقين إلى عملية تصنيع الإلكترونيات.

تستعد شركات تصنيع الأجهزة الإلكترونية للموجة التالية من عمليات التصنيع المتطورة ، ولكن سيتم خلط عملائها مع مجموعة من الخيارات المربكة - سواء لتطوير رقائق باستخدام تقنية معالجة 5 نانومتر ، أو الانتظار 3 نانومتر ، أو اختيار شيء بينهما.

يتم تحديد المسار إلى 5 نانومتر بشكل جيد ، على عكس 3 نانومتر. بعد ذلك ، يصبح المشهد مشوشًا حيث تضيف المصانع عمليات التصنيع الوسيطة ، مثل 6 نانومتر و 4 نانومتر. يعد التبديل إلى أي من هذه العمليات الفنية مكلفًا للغاية ، والفوائد ليست واضحة دائمًا.

سبب آخر للقلق هو تقلص قاعدة التصنيع. في حالة العمليات التقنية الأكثر تقدمًا ، يكون اختيار الشركات المصنعة صغيرًا. كان هناك العديد من الشركات الرائدة في الصناعة ، ولكن مع مرور الوقت ضاقت هذه المنطقة بسبب الزيادة الحادة في التكلفة وانخفاض قاعدة المستخدمين. بشكل عام ، كلما قل عدد المصنّعين ، قل عدد خيارات التكنولوجيا والسعر.

اليوم ، تعد كل من Samsung و TSMC هما المصنعان

الوحيدان اللذان يعملان مع العمليات التكنولوجية بمعدل 7 نانومتر أو أقل ، على الرغم من أن هذا قد يتغير. تقوم إنتل والشركة الصينية SMIC بتطوير عمليات التصنيع المتقدمة. Intel ، ليست أكبر لاعب في مجال الإنتاج التجاري ، تواجه مشكلات مع تطور تقنية معالجة 10 نانومتر. ومن غير الواضح ما إذا كانت SMIC ستتمكن من تقديم 7 نانومتر ، لأن هذا الموضوع لا يزال في مرحلة البحث والتطوير (يحدث الشيء نفسه مع شركة Intel باستخدام تقنية معالجة 10 نانومتر).

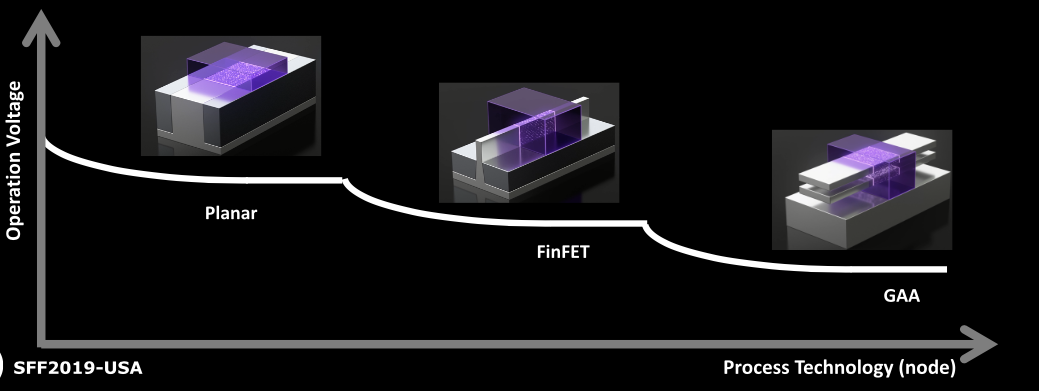

بالنسبة لعمليات التصنيع الأكثر تقدماً ، تعمل كل من Samsung و TSMC مع 7 نانومتر باستخدام ترانزستورات finFET ، وسيستمر كلا المصنّعين في ذلك عند 5 نانومتر. بخلاف الترانزستورات المستوية التقليدية ، تعتبر finFETs هياكل ثلاثية الأبعاد ذات أداء أفضل وتقليل التسرب.

بعد ذلك ، في 3 نانومتر ، تنتقل Samsung من finFET إلى بنية الترانزستور FET النانوية الجديدة ، والتي تعد بمثابة تطور لتقنية finFET. لم تكشف TSMC بعد عن خططها الخاصة بـ 3 نانومتر ، تاركة العديد من العملاء في حالة من النسيان. تزن TSMC ، وفقًا للمصادر ، مجموعة متنوعة من الخيارات ، بما في ذلك طبقات الأسلاك النانوية والأسلاك النانوية والإكراهات القسرية. تعمل Intel و TSMC وغيرها على أشكال جديدة من العبوات المتقدمة كخيارات ممكنة لتقليص الحجم.

ومع ذلك ، في 3 نانومتر حجم تكنولوجيا الترانزستور يمكن أن تذهب في اتجاهات مختلفة. لا يزال بإمكان finFET اللعب ، لكن هذه التكنولوجيا تحتاج إلى بعض الاختراقات. على ما يبدو ، سيكون على الصناعة أن تستعد للانتقال إلى البنية الجديدة لتقنية العملية 3 نانومتر ، وتكنولوجيا العملية الوسيطة التالية بسرعة 2 نانومتر ، وفقًا لخطط التطوير الخاصة بإحدى المنظمات العاملة في هذا المجال.

وقال ناوتو هوريغوتشي ، مدير البرنامج في شركة إيميك: "لا يزال 5 نانومتر في النهاية". - دعنا نقول أننا في 3 نانومتر سوف ندخل فترة انتقالية من finFET إلى أبنية أخرى. نعتقد أن هؤلاء سيكونون نانولاييرس ".

FETs Nanolayer تتعلق بهندسة الترانزستورات البوابة الشاملة (GAA). وهذا ليس هو الخيار الوحيد. إن الصناعة محافظة للغاية. سيحاول المشاركون الضغط على كل شيء بدءًا من finFET إلى الحد الأقصى. - في عملية التصنيع 3 نانومتر ، لدينا الفرصة لاستخدام finFET. لكننا سنحتاج إلى تقديم العديد من الابتكارات finFET ، وتحسينه بشكل عام. "

هل ستبقى الشركات المصنعة للرقاقة على تقنية معالجة 7 نانومتر أم ستنقل إلى 5 نانومتر أو 3 نانومتر أم إلى وسيط؟ يوفر 7 nm أداءً كافياً لجميع التطبيقات تقريبًا ، لذلك ستظل هذه العملية موجودة لفترة طويلة. يوجد في الخارج العديد من خيارات الأداء العالي ، وكلها تكلف أكثر. وسوف نرى ما إذا كانت هذه التقنيات لديها الوقت لتظهر في الوقت المحدد.

الجهد التشغيلي لعمليات التصنيع المختلفة هو الترانزستورات المستوية ، finFET و nanolayer FET.

الجهد التشغيلي لعمليات التصنيع المختلفة هو الترانزستورات المستوية ، finFET و nanolayer FET.خراب الإنتاج

تتكون الرقاقة من العديد من الترانزستورات التي تعمل كمفاتيح. على مدى عقود عديدة ، كان تقدم الدوائر المتكاملة متسقًا مع قانون مور ، حيث تتضاعف كثافة الترانزستورات على الجهاز خلال فترة تتراوح من 18 إلى 24 شهرًا.

في إيقاع مماثل ، أدخل المصنعون عمليات تكنولوجية جديدة بكثافة أعلى من الترانزستورات ، مما سمح للصناعة بتقليل تكلفة الرقائق من حيث عدد الترانزستورات. في كل عملية تصنيع ، قام المصنعون بتوسيع مواصفات الترانزستور 0.7 مرة ، مما يسمح للصناعة بزيادة الإنتاجية بنسبة 40٪ مع نفس استهلاك الطاقة وتقليل المساحة بمقدار الضعف.

اتبعت صناعة الدوائر المتكاملة هذه الصيغة وازدهرت. منذ ثمانينيات القرن العشرين ، مهدت الطريق لأجهزة الكمبيوتر الشخصية السريعة بأسعار مخفضة.

بحلول عام 2001 ، كان هناك بالفعل 18 مصنعا على الأقل مع مصانع حيث يمكنهم تصنيع الرقائق بسرعة 130 نانومتر ، والتي كانت في ذلك الوقت عملية تقنية متقدمة ، وفقًا لشركة IBS. ثم أيضًا ، ظهر عدد أكبر من المصنّعين الجدد ، مما يصنع شرائح مخصصة في مصانع الآخرين. بالإضافة إلى ذلك ، تم تصنيع تصنيع الرقاقات للمختبرات التي طورتها ، ولكن لم يكن لديها إنتاج خاص بها.

بحلول نهاية العقد ، ارتفعت تكلفة الإنتاج وعمليات التصنيع. غير قادر على التعامل مع زيادة الأسعار ، تحولت العديد من الشركات المصنعة رقاقة إلى نموذج القوات المسلحة البوروندية لايت. أنتجوا بعض الرقائق في المنزل ، والباقي تم الاستعانة بمصادر خارجية.

مع مرور الوقت ، صنع عدد أقل من الشركات المصنعة للرقاقة أجهزة متقدمة في منشآتها الخاصة. تخلص البعض تماما من الإنتاج أو ترك هذا العمل.

ومع ذلك ، في 2000s ، ظهر نموذج أعمال ورش السيليكون. تخلفت ورش العمل عن إنتل وشركات التكنولوجيا الأخرى ، لكنها سمحت لشركات التصميم بالوصول إلى العمليات المختلفة.

حدث التغيير الرئيسي التالي في المرحلة 20 نانومتر ، عندما ضربت الترانزستورات المستوية التقليدية جدار واجهت

تأثير قناة قصيرة . استجابةً لذلك ، انتقلت Intel إلى الجيل التالي من تكنولوجيا الترانزستور ، finFET ، في 22 نانومتر في عام 2011. تحولت ورش العمل إلى finFET في 16/14 نانومتر.

FinFET لديها العديد من المزايا على الترانزستورات المستوية. في هذا المخطط ، يمتد الترانزستور بأكمله عموديًا بحيث ترتفع القناة فوق الركيزة ، ويلتف الصمام حول ثلاثة جوانب من الزعنفة. تسمح منطقة التلامس المتزايدة للصمام بالتحكم بشكل أفضل في تيار التسرب ، "اكتب Matt Kogorno و Toshihiko Miyashita من Applied Materials. Kogorno هو مدير إدارة المنتجات العالمية ، و Miyashita هو كبير التكنولوجيين.

FinFET هي أيضًا أجهزة أكثر تعقيدًا ، ومن الصعب إنتاجها وتوسيع نطاقها لكل عملية تقنية لاحقة. نتيجة لذلك ، ارتفعت تكلفة البحث والتطوير إلى الجنة. لذا ، فإن إيقاع التغيير الكامل للعملية قد نما من 18 شهرًا إلى 2.5 عامًا أو أكثر.

أسعار الدوائر المتكاملة أيضا في الارتفاع. تكلفة تطوير جهاز مستوي في 28 نانومتر تتراوح بين 10 مليون دولار إلى 35 مليون دولار ، وفقا لجارتنر. للمقارنة ، فإن تكلفة تصميم نظام رقاقة واحدة (SoC) في 7 نانومتر تتراوح بين 120 مليون دولار إلى 420 مليون دولار.

وقال صمويل وين ، المحلل في شركة غارتنر: "تعتمد تكلفة التطوير بدرجة كبيرة على تعقيد شركة نفط الجنوب". - ثلثي تذهب إلى تطوير رقاقة. الباقي هو تطوير الغواصات ، وتكلفة الأقنعة وتحسين الانتاج. مع مرور الوقت ، تنخفض تكلفة التصميم أيضًا. "

ومع ذلك ، تغيرت اتجاهات الأسعار المشهد في عالم الدوائر المتكاملة. بمرور الوقت ، يمكن لعدد أقل من الشركات دفع تكاليف تصميم الرقائق لعمليات التصنيع الأكثر تقدما. يعتمد الكثير منهم على ورش عمل لقضايا الإنتاج.

أثر انخفاض عدد العملاء إلى جانب زيادة تكلفة الإنتاج على المناظر الطبيعية للورش المنتجة للرقائق المتقدمة. على سبيل المثال ، هناك خمس شركات مصنعة / ورش عمل متبقية في سوق 16/14 نانومتر: GlobalFoundries و Intel و Samsung و TSMC و UMC. تعمل SMIC أيضًا مع finFET على تقنية معالجة 14 نانومتر.

وفي 7 نانومتر حدث انتقال آخر. استمرت العمليات التكنولوجية وتكلفة الإنتاج في النمو ، وكان العائد على الاستثمار موضع تساؤل بالفعل. نتيجة لذلك ، توقفت GlobalFoundries و UMC العام الماضي عن محاولة تطوير تقنية معالجة تبلغ 7 نانومتر. تواصل الشركتان العمل في سوق 16/14 نانومتر.

في محاولة للتطوير أكثر ، تسرع Samsung و TSMC بأقصى سرعة حتى مطلع 7 نانومتر وما بعده. بعد عدة تأخيرات ، تخطط إنتل لإطلاق الإنتاج في 10 نانومتر في منتصف عام 2019 ، وفي 7 جم - بحلول عام 2021. SMIC ، وفي الوقت نفسه ، لا يعد أي مواعيد نهائية.

ولكن ليس كل عملاء الورشة يحتاجون إلى عمليات تصنيع متقدمة. هناك سوق مزدهر لرقائق 28 نانومتر. "كل هذا يتوقف على خصائص المنتج" ، قالت فين من غارتنر. - بعض المنتجات تتطلب أقصى قدر من الأداء. لا يزال بإمكان المطورين استخدام العمليات الفنية القديمة. ويمكن للرقائق المخصصة للتطبيقات التي لا تتطلب أداءً عاليًا أن تعيش على عمليتي تصنيع N-1 و N-2. "

آخرون يرددونه. "كم عدد الشركات التي يمكن أن تحمل أحدث السيليكون اليوم من وجهة نظر اقتصادية؟ عددهم يتناقص. في الأسواق التي تتطلب أداءً عاليًا للغاية ، ستكون هذه الحاجة دائمًا. لكن في سلسلة التوريد ، من حيث الكميات ، يتشكل التمزق في المنتصف. يحتاج العملاء الأكثر تطلبًا إلى عمليات تكنولوجية في 7 و 5 ، وربما في يوم من الأيام 3 نانومتر. وقال والتر اون ، نائب رئيس إدارة الأعمال في UMC: "لكن الجميع تباطأوا قليلاً".

ولكن في بعض الحالات ، هناك حاجة إلى أكثر الشرائح تقدمًا - فهذه الخوادم والهواتف الذكية. هناك أيضًا بحر من الشركات الناشئة الجديدة المرتبطة برقائق منظمة العفو الدولية. تقوم العديد من الشركات بتصميم رقائق للتعلم الآلي والتعلم العميق.

"لا أحد يجادل بأن الحاجة إلى حساب شيء أسرع بعشر مرات من اليوم ستكون دائمًا مفيدة وتنافسية تجاريًا ، حتى في الأسواق غير الفنية. كل هذه الإنجازات الفريدة لتكنولوجيا التعلم العميق دليل على ذلك. وقال أكي فوجيمورا ، مدير D2S ، إنه لا يوجد حد نهائي لطلبات زيادة الطاقة الحاسوبية.

وقال فوجيمورا: "شهدت متطلبات الطاقة الحاسوبية تحولات كبيرة - في البداية كانت وحدة معالجة الرسومات ، وتعلمًا عميقًا لاحقًا". - التعلم العميق عبارة عن تقنية ضخمة لإيجاد أنماط مناسبة ، وتدريب الشبكات العصبية هو مهمة التحسين المستمر. الآن وقد توصل العالم إلى آلية لمعالجة كمية هائلة من البيانات وتحويلها إلى معلومات مفيدة في شكل برنامج قادر على الاستنتاجات المنطقية ، يزداد عدد العمليات الحسابية اللازمة مع توفر كمية البيانات المتاحة. ونظرًا لأن حجم البيانات في جميع المجالات ينمو بشكل كبير ، فإن متطلبات القدرة الحاسوبية مضمونة في النمو بشكل كبير ، على الأقل في مجال التعلم العميق. "

ما إذا كانت رقائق AI تتطلب عمليات فنية تبلغ 5 نانومتر أو أكثر تظل غير واضحة ، ولكن هناك بالتأكيد متطلبات لزيادة قوة الحوسبة. لكن الهجرة إلى هذه العمليات التكنولوجية لا تصبح عملية أسهل أو أرخص.

5 نانومتر مقابل 3 نانومتر

وفي الوقت نفسه ، في بداية عام 2018 ، وصلت TSMC إلى معلم آخر ، لتصبح أول مصنع في العالم يستخدم تقنية معالجة 7 نانومتر. انضمت شركة Samsung لاحقًا إلى سباق 7 نانومتر تعتمد عملية تصنيع الرقائق عند 7 نانومتر بشكل أساسي على finFET ، وتتكون من رقائق التصنيع مع خطوة بوابة من 56 إلى 57 نانومتر وخطوة أدنى من وضع الموصلات المعدنية [الملعب المعدني] عند 40 نانومتر ، وفقًا للمعلومات الواردة من IC Knowledge و TEL.

في الإصدار الأول من 7 نانومتر ، استخدم تسمك 193

الطباعة الحجرية الغمر والنمذجة متعددة. هذا العام وعدت TSMC بإصدار نسخة جديدة من 7 نانومتر باستخدام الطباعة الحجرية فوق البنفسجية القصوى (EUV). تعمل EUV على تبسيط خطوات العملية ، لكنها تقنية باهظة الثمن ولديها مجموعة من الصعوبات الخاصة بها.

تستعد TSMC تكنولوجيا معالجة جديدة تبلغ 5 نانومتر لإصدارها في النصف الأول من عام 2020. ستكون التكنولوجيا الجديدة من TSMC بسرعة 5 نانومتر أسرع بنسبة 15٪ من 7 نانومتر ، وتستهلك طاقة أقل بنسبة 30٪. سيكون الإصدار الثاني من تقنية عملية 5 نانومتر ، التي ستصدر العام المقبل ، أسرع بنسبة 7 ٪. كلا الإصدارين سوف تستخدم EUV.

تسمك تكتسب بالفعل أوامر في 5 نانومتر. وقال هاندل جونز ، مدير IBS: "الطلبات الكبيرة من Apple و HiSilicon و Qualcomm". "سيكون حجم الركائز من 40.000 - 60،000 شهريًا بحلول الربع الرابع من عام 2020."

سرعة الانتقال في 5 نانومتر ل TSMC أقل من 7 نانومتر. أولاً ، 5nm هي عملية جديدة تمامًا ، مع أدوات وبراءات الاختراع المحدثة من EDA. بالإضافة إلى ذلك ، أنها أكثر تكلفة. في المتوسط ، تتراوح تكلفة تطوير الجهاز عند 5 نانومتر من 210 مليون دولار إلى 680 مليون دولار ، وفقًا لجارتنر.

بعض صانعي الرقائق يريدون الابتعاد عن 7nm دون إنفاق الكثير من المال مثل 5nm. لذلك ، أدخلت TSMC مؤخرًا تقنية جديدة تبلغ 6 نانومتر ، وهي أرخص ، ولكن مع بعض الحلول الوسط.

وقال S. S. Wei ، مدير TSMC في الاجتماع الأخير: "لا يبدو أن الأرقام N6 و N5 مختلفة ، ولكن في الواقع الفجوة كبيرة". - عند N5 ، بالمقارنة مع N7 ، تزداد الكثافة المنطقية بنسبة 80٪. N6 مقارنة مع N7 فقط 18 ٪. كما ترون ، هناك فرق كبير بين الكثافة المنطقية وكفاءة الترانزستورات. نتيجة لذلك ، يكون استهلاك الطاقة الكلي لرقاقة N5 أقل. هناك العديد من الفوائد للتحويل إلى N5. لكن N5 هي عملية فنية كاملة ، ويستغرق العملاء بعض الوقت لتطوير منتجات جديدة لها. جمال N6 هو أنه إذا كان لديهم بالفعل مشروع تحت N7 ، فسيتعين عليهم إنفاق القليل من الجهد. يمكنهم الترقية إلى N6 والحصول على فوائد معينة. واعتمادًا على خصائص المنتج والسوق ، سيقرر العملاء ما يجب القيام به. "

وفي الوقت نفسه ، طرحت شركة Samsung 5 نانومتر ، والتي ستظهر في النصف الأول من عام 2020. بالمقارنة مع 7 نانومتر ، توفر تقنية Samsung الجديدة التي تبلغ 5 نانومتر في finFET ضغط منطق يصل إلى 25٪ واستهلاك طاقة أقل بنسبة 20٪ ، أو 10٪ من سرعة العمل.

كما قدمت شركة Samsung تقنية معالجة جديدة تبلغ 6 نانومتر ، مما يوفر للعملاء خيارًا آخر. وقال ريان لي ، نائب رئيس التسويق لورش العمل في شركة Samsung: "يتمتع 6nm بميزة القابلية للتوسعة مع 7nm وإعادة استخدام الملكية الفكرية". وخطط سامسونج لديها بالفعل تطوير finFET تقنية 4 نانومتر العملية. حتى الآن ، ليس هناك عمليا أي معلومات مفتوحة عن هذه التكنولوجيا.

بعد 5 نانومتر ، يكلف عدد من عمليات التصنيع الكاملة 3 نانومتر. لكن 3 نانومتر ليس للجبناء. تتراوح تكلفة تطوير جهاز لتقنية 3 نانومتر بين 500 مليون دولار و 1.5 مليار دولار ، وفقًا لـ IBS. تتراوح تكلفة عملية التطوير من 4 مليارات دولار إلى 5 مليارات دولار ، والإنتاج - من 15 إلى 20 دولارًا. وقال جونز من IBS: "يجب أن تكون تكلفة الترانزستورات 3 نانومتر أكثر من 20 إلى 25٪ من نفس الحجم". "يمكننا أن نتوقع زيادة بنسبة 15 ٪ في الكفاءة وخفض بنسبة 25 ٪ في استهلاك الطاقة مقارنة مع 5 نانومتر finFET."

Samsung هي الشركة الوحيدة التي تعلن عن خطط لتطوير تقنية معالجة تبلغ 3 نانومتر. لهذا ، سوف تحول ورشة العمل إلى بنية الترانزستورات الدائرية ، نانولايرز. لم تكشف TSMC بعد عن الخطط ، ولهذا السبب يعتقد البعض أن الشركة متأخرة. وقال جونز: "في 3 نانومتر ، من المرجح أن تدخل شركة Samsung حجم الإنتاج في عام 2021". "TSMC تسرع التنمية من خلال محاولة مواكبة سامسونج."

في 3 نانومتر ، يفحص TSMC FETs nanolayer ، FETs nanowire ، وحتى finFETs. تتمثل إحدى الطرق لتوسيع تقنية finFET في استخدام مواد تنقل عالية في القنوات ، وهي ألمانيا. تستخدم أجهزة finFET اليوم السيليكون أو السيليكون الجرمانيوم (SiGe) في القنوات. عن طريق زيادة اختلاط الجرمانيوم ، يمكنك زيادة تنقل القناة - أي سرعة مرور الإلكترونات عبر الجهاز. وهنا تكمن المشكلة في إدارة العيوب.

تمديد التكنولوجيا finFET المنطقي. finFET في 3 نانومتر يوفر مسار انتقال من 5 نانومتر. ومع ذلك ، هناك مشاكل. من الناحية النظرية ، تعمل تقنية finFET في طريق مسدود عندما يصل عرض الزعنفة إلى 5 نانومتر ، وهو قريب من الحالة الحالية. وقال Horiguchi من Imec: "اليوم نستخدم زعانف NMOS وثلاثة PMOS في خلية قياسية". - أحد الجوانب المهمة في 3 نانومتر هو أننا بحاجة إلى التحول إلى بنية واحدة زعنفة لتصاميم الخلايا القياسية. وينبغي أن زعنفة واحدة تعمل بشكل جيد بما فيه الكفاية. لتوسيع تقنية finFET إلى N3 ، نحتاج إلى تقنية خاصة لتحسين قوة زعنفة واحدة وتقليل الظواهر الزائفة الخلفية. "

بالإضافة إلى إمكانية التنقل العالية لـ finFET ، فإن الخيار التالي هو GAA. في عام 2017 ، قدمت Samsung تقنية Multi Bridge Channel FET (MBCFET) لمدة 3 نانومتر. MBCFET - Nanolayer FET. ستتوفر نسخة MBCFET التجريبية من Samsung في عام 2020.

رقائق Nanolayer لها مزايا أكثر من finFET. في finFET ، ينحني المصراع حول الزعنفة من ثلاثة جوانب. في الطبقة النانوية ، يقع الغالق على أربعة جوانب من الزعنفة ، مما يمنح مزيدًا من التحكم في التيار.

مقارنةً بـ 5 نانومتر ، توفر FETs من الطبقة النانومترية من سامسونج زيادة بنسبة 45٪ في الكفاءة المنطقية وتقليل استهلاك الطاقة بنسبة 50٪ أو أداء أسرع بنسبة 35٪. وقال سامسونغ سامسونغ: "إن بنية finFET لها قيودها الخاصة على قابلية التوسع ، حيث لا يمكن خفض جهد التيار الكهربائي إلى ما دون 0.75 فولت. إن ابتكارنا باستخدام طبقات النانو يقلل الجهد إلى قيم أقل من 0.7 فولت".

هناك عدة أنواع من تقنيات GAA ، بما في ذلك nanolayer FET و nanowire FET. GAA نفسها هي الخطوة التالية بعد finFET. في هذا النظام ، تقع finFET على جانبها ، ثم تنقسم إلى أجزاء أفقية. قطع قنوات شكل. يلتف مصراع المواد حول كل طبقة.

بالمقارنة مع أسلاك متناهية الصغر FET ، مثل هذه الدائرة لديها قنوات أوسع ، أي إنتاجية أعلى وحركة الإثارة. وقال Imec Horiguchi: "تتميز طبقات النانو بعرض أكثر فعالية". "الأسلاك النانوية تفعل أفضل بكثير مع الكهرباء الساكنة." لكن المقطع العرضي صغير جدًا. هذا لن يعطي مزايا من حيث عرض القناة الفعال. "

GAA البنايات لديها العديد من القضايا. عادة ما تعطي زيادة صغيرة للغاية مقارنة مع finFET في 5 نانومتر. صنع رقائق باستخدام هذه التكنولوجيا أمر صعب للغاية.

وقال ريتشارد جوتشو ، نائب الرئيس والمدير الفني لشركة لام ريسيرش: " يضيف الجيل القادم من GAA بسرعة 3 نانومتر وأدناه مستوى آخر من التعقيد إلى التصنيع" . - للوهلة الأولى ، يبدو وكأنه تعديل ل finFET. ومع ذلك ، تزداد المتطلبات وتعقيد بنية GAA هذه أعلى بكثير من finFET. "في عملية إنتاج رقائق nanolayer ، فإن الخطوة الأولى هي وضع طبقات رقيقة بالتناوب من SiGe والسيليكون على الركيزة. "نحصل على كومة من السيليكون والسيليكون والجرمانيوم والسيليكون. قال نامسون كيم ، كبير مهندسي المواد التطبيقية ، في مقابلة أجريت معه مؤخراً: "نسميها الشبكة الفائقة". "وجود محتوى من الجرمانيوم ، تحتاج إلى تزويده بطبقة جيدة من العزل."كحد أدنى ، يجب أن تتكون العبوة من ثلاث طبقات من SiGe وثلاثة من السيليكون. ثم يتم تطبيق هياكل ورقة صغيرة على الحزمة. بعد ذلك ، يتم تشكيل العزل مع الأخاديد ، ثم المقسمات الداخلية.بعد ذلك ، تتم إزالة طبقات SiGe من الطبقة الفائقة ، تاركة طبقات السيليكون بمسافة خالية بينها. تشكل كل طبقة من السيليكون قاعدة الورقة أو القناة في الجهاز. ثم تحتاج إلى تطبيق مادة ذات ثابت عازل عالي لإنشاء مصراع. هناك حد أدنى للمسافة بين الأسلاك النانوية. صغير جدا المشكلة هي وضع معدن سمك العمل هناك.عملت الصناعة على مر السنين لإنشاء تكنولوجيا GAA ، ولكن لا تزال هناك بعض المشاكل. وقال كيم "أحد أهم هذه العوامل هو السعة الطفيلية". - إذا سألتني ما هي المشاكل الرئيسية لتكنولوجيا GAA ، فهناك مشكلتان. المقسمات الداخلية والعزل الركيزة. "ما التالي؟

ما هي مدة تكنولوجيا GAA أو الطبقات النانوية بما فيه الكفاية؟ "سوف تحافظ نانولاييرز على اثنين أو ثلاثة من تقنية العملية التالية. يمكن أن تجعل ورش العمل نانولايرز على N3. الجيل القادم هو بالتأكيد. وبعد ذلك ، قد تضطر إلى تغيير تكامل الطبقات النانوية أو الهندسة المعمارية. وقال هوريجوتشي من شركة إيميك: "ستظل الهندسة المعمارية النانولية".تستكشف الصناعة طرقًا لتحسين تقنيات GAA و finFET في عمليات التصنيع المتقدمة. توفر أجهزة GAA حاليًا ميزة طفيفة على تقنية finFET. على سبيل المثال ، في شريحة Imec النانوية السابقة ، كانت خطوة البوابة 42 نانومتر ، وكانت الخطوة الدنيا لوضع الموصلات المعدنية 21 نانومتر. في المقارنة ، قد يحتوي finFETs عند 5 نانومتر على بوابة بوابة تبلغ 48 نانومتر والحد الأدنى من النواقل المعدنية من 28 نانومتر.في المختبر ، أظهرت Imec قابلية تطوير جهاز أشباه الموصلات من النوع p مع كومة مزدوجة من GAA والجرمانيوم في القناة. باستخدام دائرة خالية من الامتدادات ، طورت Imec أسلاك متناهية الصغر يبلغ طول بوابةها حوالي 25 نانومتر. يمكن تكييفها للطبقة النانوية. كما هو الحال مع الإصدار السابق ، حجم السلك هو 9 نانومتر.يمكن أن تلعب الجرمانيوم دورًا في الاستمرار في استخدام finFET خارج تقنية المعالجة التي تبلغ 5 نانومتر. وأظهرت Imec قه nFinFET مع ارتفاع قياسي Gmsat / SSsat و PBTI. تم تحقيقها من خلال تحسين استبدال المواد العازلة العالية.سنرى أيضًا ما إذا كان يمكن توسيع تقنية finFET إلى 3 نانومتر. ومن غير الواضح أيضًا ما إذا كانت رقائق nanolayer ستظهر في الوقت المحدد أم لا. هناك الكثير من المجهول والشكوك في هذا المشهد المتغير ، ولا يوجد جدول زمني لتوضيح الموقف.