إذا كنت تعتقد أن "عصابة" من إنتل هي أتباع

قانون مور الأكثر ولاءً ، فمن المحتمل أنك لم تسمع كيف ينتشر فيليب وونغ حول هذا الموضوع. قدم ونج ، نائب رئيس أبحاث الشركات في Taiwan Semiconductor Manufacturing Corp (TSMC) ، عرضًا تقديميًا في مؤتمر Hot Chips مؤخرًا ، مفاده أن قانون مور ليس فقط على قيد الحياة وبصحة جيدة ، ولكن مع مجموعة متنوعة إلى حد ما من الحيل التكنولوجية ، فإنه لا يزال غير صحيح أقل من ثلاثة عقود.

"إنه لم يمت" ، كما أخبر الحاضرين في Hot Chips. "إنه لا يتباطأ ، ولا يسعل".

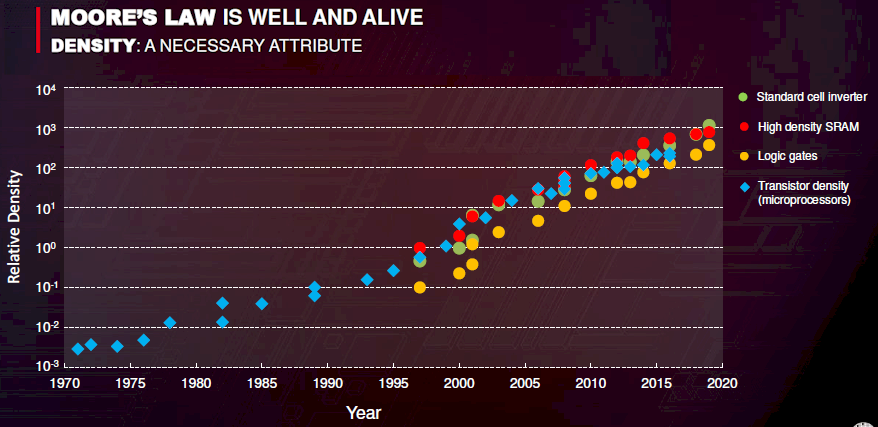

استمع إلى Wong ، وبالتالي فإن الإجراء الوحيد الضروري للحفاظ على قانون مور هو تحسين الكثافة. وعلى الرغم من أنه يعترف بأن تردد الساعة قد بلغ سقفه ، وهو ما يشير إلى نهاية

قانون التدرج الخاص بـ Dennard ، إلا أنه يقول إن كثافة الترانزستورات هي التي ستعمل على تحسين السرعة وكفاءة الطاقة.

قانون مور حي

قانون مور حيفي النهاية ، لا يهم مدى تحقيق الكثافة الأعلى. يعتقد ونج أن الشيء الرئيسي هو أن الشركات يمكنها أن تضع المزيد من الترانزستورات في حجم أصغر مع كفاءة أفضل في استخدام الطاقة. على المدى القصير ، يمكن تحقيق ذلك بالطريقة القديمة والمثبتة ، أي عن طريق تحسين تكنولوجيا التصنيع الخاصة بـ CMOS بحيث تتحول إلى إنتاج الترانزستورات بطول بوابة أقصر.

TSMC قد أتقن بالفعل تقنية عملية 7 نانومتر ويتجه نحو 5 نانومتر. قال ونج إن النظام الإيكولوجي لتطوير تكنولوجيا العملية 5 نانومتر جاهز بالفعل ، وقد بدأت الشركة بالفعل في إنتاج عينات المخاطر - أي أن تكنولوجيا العمليات وأدوات التطوير جاهزة ، ويتم إنتاج ركائز العمل. في الاجتماع الأخير للمساهمين ، أعلنت TSMC أنها تعتزم بدء الإنتاج الضخم للرقائق في الساعة 5 نانومتر في النصف الأول من عام 2020. اتضح أن خطط الشركة تشمل بالفعل تكنولوجيا عملية 3 نانومتر.

لكن كل هذه التكنولوجيا تعتمد على رقائق مستوية ، ويعترف ونج بأن هذه الطريقة ستتوقف في النهاية عن التوسع. "إذا اتبعنا طريق الزيادة ثنائية الأبعاد ، فقد وصلنا بالفعل إلى عدة مئات من الذرات ، وسرعان ما سوف تنفد جميع ذراتنا".

ولكن هذا لا يعني نهاية الزيادة في الكثافة. وأشار إلى أن بعض الابتكارات في صناعة أشباه الموصلات تدعم مخطط الكثافة التصاعدية حتى في نهاية عملية قياس دينارد. على وجه الخصوص ،

ظهرت تكنولوجيا السيليكون المتوتر

والعزل الكهربائي العالي k ، ثم تبعتها FInFet (Fin Field Effector Transistor) ، تقنية البنى ثلاثية الأبعاد. الآن ، لتجاوز 7 نانومتر ، يتم التحقيق في تقنية DTCO (التحسين المشترك لتكنولوجيا التصميم).

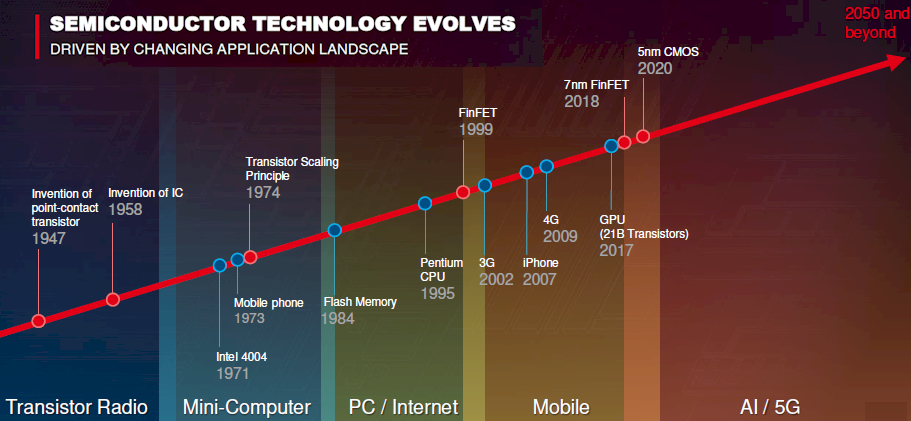

حدثت كل هذه الابتكارات لأنه كان من الضروري تطوير منصات حوسبة جديدة تتطلب أجهزة أسرع وأكثر كفاءة في استخدام الطاقة. هذا التطور ولدت أجهزة الكمبيوتر الصغيرة في 1970s ، وأجهزة الكمبيوتر في 1980s ، والإنترنت في 1990s ، واليوم ، والأجهزة المحمولة. تتطلب كل مرحلة زيادة في الكثافة من خلال تحسين تصنيع أشباه الموصلات. يعتقد ونج أن الطلبات التالية سوف تأتي من الذكاء الاصطناعي و 5 G.

تطور تكنولوجيا أشباه الموصلات

تطور تكنولوجيا أشباه الموصلاتما هي الابتكارات المطلوبة لضمان عدم توقف حزب مور القانوني؟

على المدى القصير ، ستزيد الكثافة الحسابية الكلية وكثافة الذاكرة من استخدام الشرائح المستخدمة لإنشاء حالات متعددة الشرائح من هياكل 2.5D ، حتى لو لم تصبح الرقاقات نفسها أكثر كثافة. قال ونج إن هذه العملية تجعل بالفعل تقنية العملية المحددة لشريحة صغيرة معلمة أقل أهمية من القدرة على دمج هذه المكونات في حزمة واحدة.

لدى TSMC نسختها الخاصة من الهيكل 2.5D المزوّد بتقنية Chip-on-Wafer-on-substrate (CoWoS) (جسر ربط متعدد الأجزاء مدمج ، أو EMIB من Intel ينافس هذه التكنولوجيا). يتيح لك CoWoS إنشاء حاويات متعددة الشرائح ، وتحديد شرائح الذاكرة وذاكرة مناسبة على المتدخل ، وتوصيلها باستخدام جهات اتصال TSV العمودية. يعتبر تطبيق CoWoS الأكثر إثارة للاهتمام هو مسرع وحدة معالجة الرسومات Nvidia Tesla V100 ، حيث يتم تعبئة وحدة معالجة الرسومات GV100 بذاكرة عرض النطاق الترددي العالي (HBM). يتم دمج المزيد من الشرائح بواسطة Intel و AMD و Xilinx.

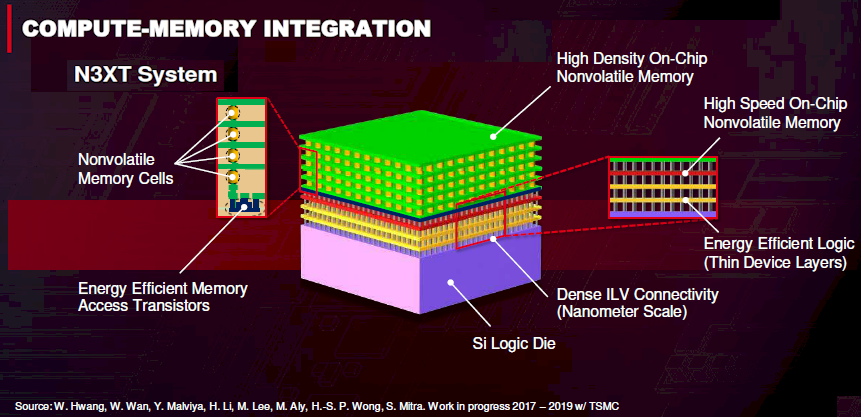

لكن إمكانيات 2.5D لزيادة الكثافة ليست محدودة. سيتطلب حل أكثر قابلية للتطوير تقنيات وضع الترانزستور ثلاثية الأبعاد حقًا. لهذا ، وفقًا لـ Wong ، فإن تقنية N3XT ثلاثية الأبعاد المتجانسة هي الأنسب استنادًا إلى المواد الجديدة والتكامل الضيق للذاكرة مع المنطق. تمت مناقشة N3XT ، وهي "تكنولوجيا هندسة النانو لأنظمة الحوسبة" ، في الأوساط الأكاديمية منذ عام 2015 ، ولكن الآن وقد بدأت شركات مثل TSMC في التعامل معها بجدية ، فإن لديها فرصة جيدة للتسويق.

أظهر ونج شرائح مع الرسوم البيانية لكيفية ظهور مثل هذا الجهاز. يتكون من طبقات من المنطق الموفر للطاقة (الأصفر) والذاكرة عالية السرعة (الأحمر) والذاكرة غير المتطايرة ذات السعة العالية (الأخضر) ، مرتبة ترتيبًا واحدًا فوق الآخر. وكل هذا يجلس على الكريستال منطق السيليكون العادي (الأرجواني).

نظام N3XT

نظام N3XTالشيء الرئيسي هنا هو الجمع بين الطبقات المختلفة من خلال ILV و Inter-Layer-Via (وصول عمودي للطبقة البينية). على عكس مقياس الميكرومتر TSV ، يمكن تشكيل ILV على مقياس نانومتر. على الرغم من أن هذا جزء مهم للغاية من تقنية N3XT ، إلا أن Wong لم يستطع أن يخبرنا به كثيرًا. ومع ذلك ، من الواضح أن TSMC تعمل عن كثب على ذلك وقد سجلت بالفعل العديد من براءات الاختراع المتعلقة به.

في الشرائح ثلاثية الأبعاد ، يعد تشذير الذاكرة والمنطق أمرًا مهمًا للغاية ، لأنه يتيح لك تقليل المسافة بينهما ، وبالتالي ضمان إنتاجية عالية وانخفاض زمن انتقال المعلومات ، مما سيكون ضروريًا للتطبيقات مثل AI و 5G. في CMOS ، لا يمكن تشذير الذاكرة والمنطق ، حيث أن حفر ترانزيستورات المنطق تتطلب درجة حرارة تصل إلى 1000 درجة مئوية ، مما يؤدي إلى تدمير الطبقات المجاورة في الإنتاج. يتطلب الأمر شيئًا يمكن تصنيعه عند درجات حرارة تصل إلى 400 درجة.

اتضح أنه في السنوات القليلة الماضية ، درس الباحثون مواد جديدة تبدو مناسبة لإنتاج الترانزستورات عالية السرعة في درجات حرارة منخفضة نسبيًا. على عكس مواد السيليكون المستخدمة في الإنتاج اليوم ، يتم استخدام أحادي الطبقة من معادن انتقالية ثنائية الهالوجين (TMD) هناك على أساس عناصر مثل الموليبدينوم والتنغستن والسيلينيوم.

تُظهر مواد TMD قابلية حركة عالية لشركات الشحن - حيث تنتقل الإلكترونات عبرها بسهولة كبيرة - مع قنوات ضيقة. ما هو مناسب ، هناك حاجة فقط إلى مثل هذه الخصائص لإنشاء الترانزستورات بحجم أقل من 2-3 نانومتر. وقال ونج إن مختبر TSMC يختبر ركائز TMD تجريبية تعتمد على ثاني كبريتيد التنغستن.

مرشح آخر للمواد النانوية هو أنابيب الكربون النانوية. وقال ونج إن الاختلافات التجريبية قد تم إجراؤها ، مما يظهر السلوك المادي الجيد كأشباه موصلات. تم بالفعل تجميع نماذج العمل المنطقية و SRAM القائمة على أنابيب الكربون النانوية ، بما في ذلك RISC-V البديل من الباحثين في معهد ماساتشوستس للتكنولوجيا.

بالنسبة للذاكرة ، وفقًا لـ Wong ، فإن المرشحين الأكثر احتمالًا للتكامل ثلاثي الأبعاد سيكونون: SST-MRAM (ذاكرة الوصول العشوائي المغنطيسية ذات الدوران العكسي المغزلي ، وذاكرة الوصول العشوائي المغنطيسية التي تستخدم نقل زخم الدوران المغنطيسي لتسجيل)

مرحلة PCM

تغيير الذاكرة .

وصول عشوائي ذاكرة مقاوم ReRAM. الذاكرة على أساس المعدن برمجة خلية CBRAM. FERAM

ذاكرة الوصول العشوائي الكهروضوئي. كل هذا هو ذاكرة غير متطايرة مع الوصول العشوائي ، والتي لا تتطلب عملية محو خلية قبل كتابة معلومات جديدة إليها. بعض الخيارات موجودة بالفعل في السوق - Everspin MRAM و Samsung MRAM و Crossbar ReRAM و Intel 3D XPoint (والتي ، وفقًا لمعظمها ، هي نوع مختلف من PCM).

أنواع جديدة من الذاكرة

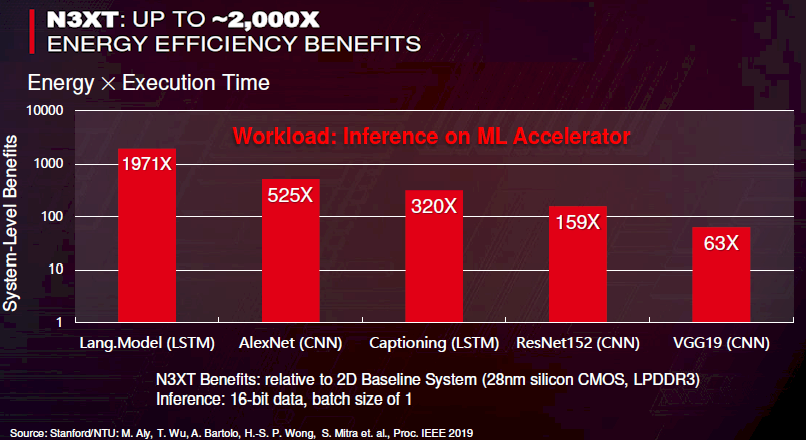

أنواع جديدة من الذاكرةقام الباحثون بمحاكاة أداء أجهزة N3XT وقارنوها بشرائح تقليدية ثنائية الأبعاد لها نفس المنطق وقدرات الذاكرة تقريبًا. وفقًا لأبحاثهم ، حيث تم استخدام طرق مختلفة لقياس سرعة خوارزميات التعلم الآلي ، فقد تبين أن أجهزة تقنية N3XT كانت أكثر كفاءة بنسبة 63-1971 مرة من الأجهزة ثنائية الأبعاد.

ميزة N3XT على الأنظمة ثنائية الأبعاد

ميزة N3XT على الأنظمة ثنائية الأبعادهذا يبدو واعدا. لكن ونج لم ينشر كيف ستتمكن هذه التقنيات بالضبط في السنوات الثلاثين القادمة من الحفاظ على سرعة تحسين التكنولوجيا اللازمة لقانون مور. على سبيل المثال ، سيمنحنا الانتقال إلى المواد النانوية الجديدة زيادة لمرة واحدة في كثافة الترانزستورات فيما يتعلق بالمكونات ثنائية الأبعاد. لكن هناك ، في النهاية ، سنواجه قيودًا ذرية.

من الناحية النظرية ، إذا كان بإمكانك مضاعفة ارتفاع الأجهزة ثلاثية الأبعاد كل 18 شهرًا ، يمكنك تحقيق زيادة في الكثافة لكل مساحة سطح مربعة. بالطبع ، بالنسبة للأجهزة المحمولة والأجهزة المدمجة ، ستصبح هذه الطريقة سريعة التعقيد ، وستستقر رقائق أجهزة الكمبيوتر في مراكز البيانات بعد سبعة إلى ثمانية أجيال في سقف يبلغ ارتفاعه 4 أمتار.

لكي يستمر كل شيء في العمل لعدة عقود ، ولكي تستمر الكثافة في التوافق مع منحنى قانون مور ، يجب تطوير ابتكارات تقنية أخرى لم يذكرها ونج. ولكن إذا أنتجت شرائح مثل TSMC ، عليك أن تقبل أن الباحثين سوف يمنحك باستمرار مرشحين جدد للتقنيات التي ستحتاج فقط إلى طلبات من مهام جديدة أكثر تطلبًا للدخول إلى السوق. وإذا كنت تتذكر القصة ، فستظهر هذه المهام بالتأكيد.