بوريس تسيرلين وألكساندر كوشنيروف

2019/10/30

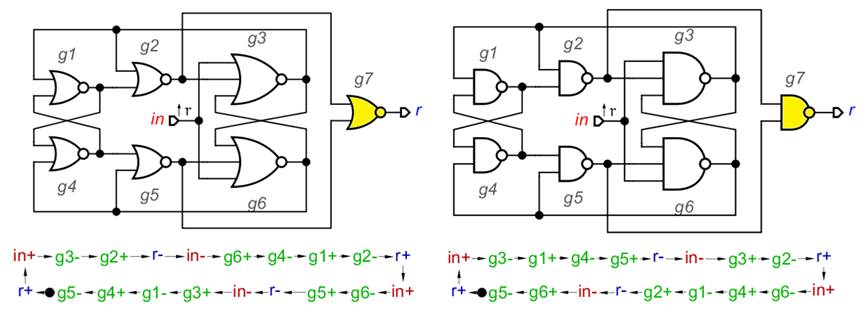

ليس من الصعب على المصمم ذي الخبرة أن يجد دائرة مألوفة ، بغض النظر عن الشكل الذي يتم رسمها به. في هذه المقالة ، نوضح أن دائرتي الترانزستور من براءات الاختراع هي البديل من مشغل العد غير المتزامن (AST). مقارنة بالدائرة القياسية ، بعض الترانزستورات مفقودة من براءات الاختراع. هذا يمكن اعتبار خلل. سنبين أنه في حالة حدوث نفس الخطأ في الدائرة القياسية ، فإنه يستمر في العمل بشكل صحيح. يُعرف AST الذي يتم تطبيقه فقط على عناصر OR-NOT [1] أو فقط على عناصر AND-NOT باسم مشغل Harvard. يظهر الشكلان المتغيران للمخططات في الشكل. 1 ، حيث g7 هو مؤشر على الانتهاء عابر. في المستقبل ، لن نفكر في ذلك. في الشكل يوضح الشكل 1 أيضًا الرسوم البيانية لنقل الإشارات (STGs) [2] المضمنة في Workcraft [3].

التين. 1. مشغل العد غير المتزامن (AST) و STG الخاص به.

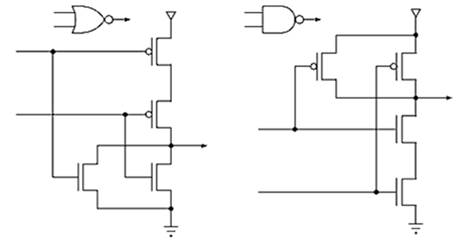

لاحظ أنه في كلا الإصدارين من AST هناك ثلاثة أزواج من العناصر (g1 ، g2) ، (g4 ، g5) و (g3 ، g6) التي لها دخل مشترك. دوائر الترانزستور للعناصر 2I-NOT و 2OR-NOT الموضحة في الشكل. 2. يتم ترتيب ثلاثة عناصر الإدخال بالمثل وتحتوي على 6 الترانزستورات.

التين. 2. دوائر الترانزستور من العناصر 2I-NOT و 2OR-NOT.

نأخذ عنصرين 2OR-NOT ونختار عند كل إدخال ، حيث يتم توصيل الترانزستور p-MOS إلى Upit. قم بتوصيل هذه المدخلات معًا والاتصال بالأرض (سجل. 0). سيتم فتح كل من الترانزستورات والجهد في المصارف سيكون مساويا لل Upit. هل هذا يكفي لتوصيل المصارف بأمان واستبدال الترانزستورات بواحد ، كما هو مبين في الشكل. 3؟ لا. تحتاج إلى التحقق مما يحدث إذا قمت بتسجيل الدخول إلى الإدخال المشترك. 1. سيتم توصيل مخرجات كلا العنصرين بالأرض ، وسيكون لدينا دائرة جسر لأربعة ترانزستورات p-MOS. بالنسبة إلى المدخلين المتبقيين ، لدينا أربع مجموعات 0 و 1. من السهل إظهار أنه لا يوجد في أي منهما دائرة قصيرة بين Upit والأرض.

التين. 3. اثنين من العناصر 2OR-NOT تقاسم المدخلات المشتركة.

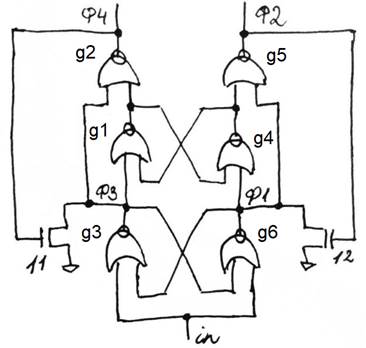

نعتبر الآن دائرة موزع النبضة [4] في الشكل. 4. باستخدام الشكل. 3 ، يمكننا إعادة رسم هذا المخطط كما هو موضح في الشكل. 5. من الممكن بالفعل التعرف على AST في الشكل. 1 ، ومع ذلك ، هناك عناصر g3 و g6 لها 3 مدخلات.

التين. 4. مخطط الموزع النبضي من [4].

التين. 5. متغير من الدائرة في الشكل. 4.

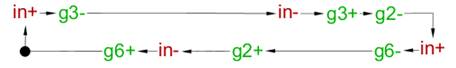

يمكن اعتبار بوابات الترانزستورات 11 و 12 مدخلات لعناصر 3OR-NOT حيث يتم اختزال ترانزستور p-MOS الثالث. هل يؤثر هذا على التشغيل الصحيح للدائرة؟ النظر في ترتيب ظهور الإشارات في ، g2 ، و g6 عند إدخال العنصر g3. للقيام بذلك ، احذف جميع الإشارات الأخرى في STG المقابلة في الشكل. 1 كما هو مبين في الشكل. 6.

التين. 6. STG لأو لا. إشارات الدخول ، g2 ، g6 و g3.

نظرًا لأن الترانزستور الثالث p-MOS قصير ، يمكن أن يحدث التبديل g3 + بعد التبديل داخل و g6- (بأي ترتيب) دون السماح بالتبديل g2-. ومع ذلك ، كما يتبين من الشكل. 6 ، في القسم من g2 + إلى g2 - يوجد فقط في + و g6 + ، وبالتالي ، لا يحدث التبديل المحظور g3 +. قبل التبديل g2 + ، يكون العنصر g3 بالفعل عند 0 ، وعند دخله g6 لا يزال 0 ، أي أول ترانزستور p-mos مفتوح. يؤدي تبديل g2 + إلى فتح الترانزستور 11 ويجب إيقاف تشغيل الترانزستور p-MOS المختزل. هذا لا يحدث ، علاوة على ذلك ، فإن التبديل داخل يفتح الترانزستور p-MOS الثاني. وهكذا ، من خلال اثنين من الترانزستورات p-MOS المفتوحة و الترانزستور المفتوح 11 ، يبدأ التيار بالتدفق من Upit إلى الأرض. يستمر هذا لفترة قصيرة حتى يغلق مفتاح g6 + التالي أول الترانزستور p-MOS. خلال هذا الوقت ، يوفر الترانزستور 11 صفر عند إخراج g3. كيف بالضبط؟ لنفترض أن مقاومات الترانزستورات المفتوحة p-MOS و n-MOS هي نفسها ومساوية لـ R ، ثم بعد التبديل في الجهد على g3 يقفز من 0 إلى (1/3) Upit ، لكن هذا في الحالة المثالية. في الممارسة العملية ، هناك بعض السعة الطفيلية بين g3 والأرض ، حيث يزيد الجهد بسلاسة وقد لا يصل إلى (1/3) Upit. بطريقة أو بأخرى ، سيكون هذا الجهد أقل من (1/2) Upit ويعني سجل. 0. بالنسبة إلى الترانزستور 12 ، كل شيء مشابه ، فهو يوفر وقتًا قصيرًا 0 عند إخراج g6. وبالتالي ، فإن التأخير في العناصر g6 و g3 يحدد فترتين من الوقت عندما يستهلك المشغل تيارًا كبيرًا يساوي تقريبًا Upit / (3R).

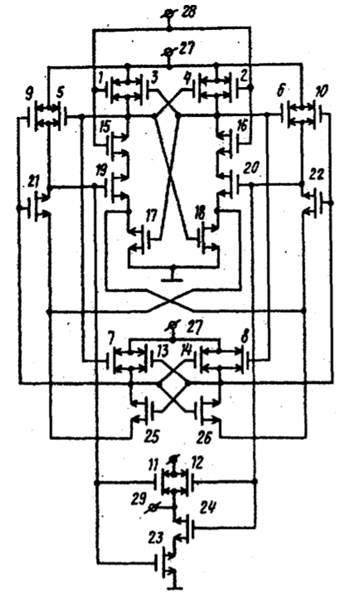

دعونا الآن نفكر في دائرة الزناد العد [5] في الشكل. 7. هنا تشكل الترانزستورات 11 و 12 و 24 و 23 العنصر 2I-NOT ، والذي ، على ما يبدو ، مؤشر على AST في الشكل. 1. يتم تكوين عنصر آخر 2I-NOT بواسطة الترانزستورات 7 و 13 و 25 و 18. دعنا ننتبه إلى حقيقة أن الترانزستور 18 متصل بالأرض وبنفس المثال في الشكل. 3 ، هو مشترك بين العناصر الثلاثة وليس. يتم تكوين العنصر الثاني 2I-NOT ، والذي يتضمن الترانزستور 18 ، بواسطة الترانزستورات 5 و 9 و 21 ، والثالث هو 3I-NOT على الترانزستورات 2 و 4 و 16 و 20. بالتوازي مع الترانزستورات 2 و 4 ، ينبغي أن يكون هناك الترانزستور p-MOS الثالث لكنه غائب. الدائرة في الشكل. 7 متماثل ، من أجل فهم أفضل ، نعيد رسمه كما هو موضح في الشكل. 8.

التين. 7. مخطط الزناد القابل للعد من [5].

التين. 8. متغير من الدائرة في الشكل. 7.

هل سيكون هناك مخرجات g3 و g6 في الشكل. 8 التبديل بشكل صحيح إذا كان الترانزستور الثالث موس بالتوازي مفقود؟ سيتم فهم هذا بعد تحليل STG في الشكل. 9 ، كما في الحالة السابقة ، يتم الحصول عليها من STG المقابلة في الشكل. 1 عن طريق إزالة جميع الإشارات باستثناء في ، g2 ، g6 ، و g3.

التين. 9. STG ل NAND. إشارات الدخول ، g2 ، g6 و g3.

عنصر g3 هو 3I-NOT ، لذلك بعد التبديل في + ، g6 + و g2 + (بأي ترتيب) ، سيتم تبديل g3 -. يجب أن يتسبب أي من مفاتيح التحويل in- أو g6- أو g2- في التبديل g3 +. ومع ذلك ، لا يمكن لـ g2- فتح الترانزستور p-MOS المفقود ، لذلك ستبقى g3 عند 0 وستنتظر حتى يتم التبديل داخل أو g6. كما يتبين من الشكل. 9 ، في القسم من g3- إلى g3 + لا يوجد تبديل g2- وليس هناك حاجة إلى الترانزستور p-MOS هنا. من ناحية أخرى ، ينبغي أن يوفر هذا الترانزستور سجل. من 1 إلى g3 عند التبديل داخل و g6 بشكل تعسفي. النظر في الشكل. القسم التاسع من g3 + إلى g2 +. التبديل g2- يغلق الترانزستور 19. بعد ذلك ، يؤدي التبديل في + إلى إغلاق الترانزستور 1 ويفتح الترانزستور 15. يبقى العنصر g6 عند 1 ، أي الترانزستور 17 مفتوح ، ويتم إغلاق الترانزستور 3. وهكذا ، في + يقطع g3 عن كل من الأرض و Upit. ومع ذلك ، يتم الاحتفاظ السجل على g3. 1 ، لأنه في الممارسة العملية ، توجد سعة طفيلية بين g3 والأرض ، وهي مشحونة حتى Upit. التبديل g6- يفتح الترانزستور 3 ويربط هذه السعة بـ Upit. للنصف الثاني من المخطط ، كل شيء مشابه. وبالتالي ، فإن التأخير في العناصر g6 و g3 يحدد الوقت الذي يتم فيه تخزين الحالة على الخزان. في الممارسة العملية ، من المهم أن يكون تيار التسرب من الترانزستورات 19 و 20 صغيرًا ، وإلا قد تفريغ السعة أدناه (1/2) Upit في الوقت المخصص.

بالمقارنة مع AST القياسية في الشكل. 1 ، في المخططات في الشكل. 5 وفي الشكل. 8 ، وظيفة الإعداد إلى 1 عنصر 3 أو لا ، وإعادة تعيين وظيفة إلى 0 من العنصر 3 أو لا التالفة. هذا يعني أن AST القياسي سيستمر في العمل بشكل صحيح ، حتى لو حدث خلل مماثل في العنصرين g6 و g3. لدائرة قياسية (بدون g7) ، هناك حاجة إلى 28 الترانزستورات. للدوائر في الشكل. 4 وفي الشكل. 7 (بدون الترانزستورات 11 و 12 و 24 و 23) تحتاج إلى 23 و 22 الترانزستورات ، على التوالي. إذا قمت بإرجاع ترانزستورات p-MOS المفقودة ، فستعمل هذه الدوائر بشكل أكثر موثوقية. الحد الأدنى لعدد الترانزستورات في الدائرة في الشكل. 7 لا يعني بالضرورة أنه أفضل من الدائرة في الشكل. 4 ودائرة أفضل في الشكل. 1. بالإضافة إلى عدد الترانزستورات والاستهلاك الحالي ، هناك معايير مهمة أخرى ، على سبيل المثال ،

- تعقيد دائرة إضافية لتحديد الحالات الأولية

- سعة الحمولة (معدل إعادة تحميل سعة الحمولة)

- معدل الخروج من حالة النقيلي

- عدد وقيم السعات الطفيلية

- عدد وقيم تيارات التسرب

تحليل مقارن لهذه المعلمات ، وكذلك مناقشة مخططات AST تنفيذها على عناصر أخرى ، هو خارج نطاق هذه المقالة.

أدب

[1] GT Osborne ، "مرحلة تسجيل عداد ثنائي غير متزامن مع انعكاس وبوابة باستخدام تعدد دوائر NOR المترابطة." براءة اختراع US3139540 ، 30 يونيو. 1964.

[2] L. Ya. Rosenblum and A. V. Yakovlev ، "على نموذج رسومي جديد لتوضيح جوهر الاختراع" ، قضايا الاختراع ، العدد 11 ، ص. 36-40 ، 1988.

[3] https://workcraft.org

[4] V. I. Goryachev، B. M. Mansurov، Ya .D Martynenko and R. G. Talibov، "موزع النبض الرباعي المراحل". شهادة حقوق التأليف والنشر SU342299 ، 06/14/1972.

[5] V. I. Varshavsky، N. M. Kravchenko، V. B. Marakhovsky and B. S. Tsirlin، "Counting trigger on CMOS transistors". شهادة حقوق التأليف والنشر SU1398069 ، 05.23.1988.