شاركت Intel هذا الأسبوع في خططها طويلة الأجل لإدخال عمليات التصنيع الجديدة. في عام 2029 تقريبًا ،

تعتزم Intel تقديم تقنية معالجة بمعايير 1.4 نانومتر. بعد 10 سنوات ، من غير المرجح أن يكون فريق إدارة الشركة كما هو اليوم. لذلك ، تذكرنا هذه الخطط بمهارة خوجة نصر الدين عن حمار خان ، ومدرّس الحيوان في شخص خوجة نفسه. بحلول الظهر ، قد لا يكون المدعى عليه هناك. ولكن هذا ليس عن ذلك. المخطط ، ثم نقبل كدليل للعمل.

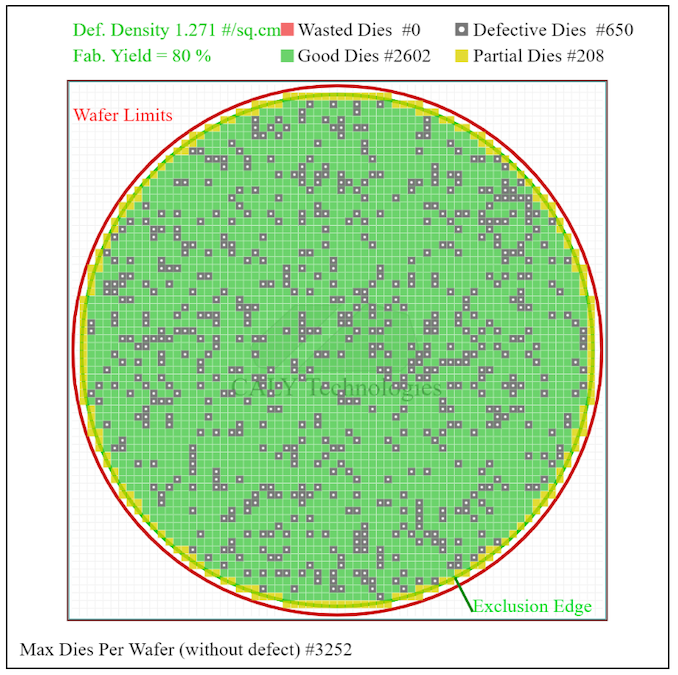

في معسكرات الشركات الرائدة في مجال تصنيع أشباه الموصلات ، هناك قدر أكبر من الوضوح ، وهو ما يؤكده الإنتاج المحفوف بالمخاطر لرقائق TSMC بمعايير 5 نانومتر (

اليوم ، يبلغ معدل الخلل 20٪ فقط بمعدل 3-8٪ للبلورات التي تبلغ مساحتها 17.92 مم

2 ، للقطع) سوف AMD Zen 2 لديها مستوى أعلى من الرفض - ما يصل إلى 60 ٪). ومع ذلك ، قبل إصدار معالجات AMD بمعايير 5 نانومتر ، سوف يمر عام ونصف على الأقل.

/ صورة من موقع AnandTech

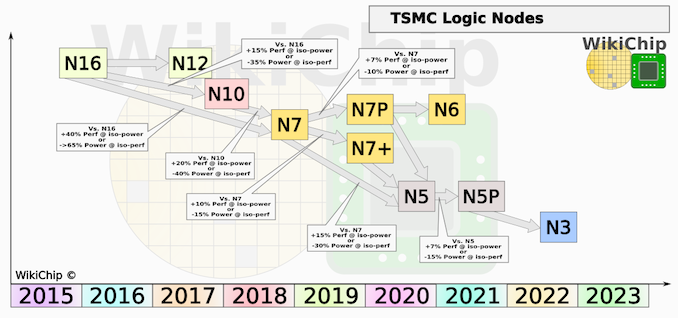

/ صورة من موقع AnandTechفي العام المقبل ، بدءًا من الربع الثاني ، سيتم استخدام تقنية معالجة TSMC مع معايير 5 نانومتر لإنتاج متسلسل لـ SoC على قلب ARM. في عام 2022 ، من الواضح أن شركة TSMC ستبدأ الإنتاج الخطير لرقائق 3 نانومتر (أيا كان معنى هذه النانومتر) ، وفي غضون عامين ، تعد الشركة ببدء إنتاج حلول ثنائية النانو. سيكون ذلك في الفترة من 2024 إلى 2025 ، أو قبل سنتين إلى ثلاث سنوات من تقديم Intel تقنية العملية نفسها.

بالنسبة إلى Samsung ، ستتمثل العمليات التي تتمتع بمعايير 5 نانومتر و 4 نانومتر في

تطور تقنية العمليات التي

تبلغ 7 نانومتر ، والتي سيتم التعبير عنها في تخفيض تدريجي صغير في خطوات المعدنة ضمن عناصر FinFET مثل القنوات والبوابات. بشكل عام ، ستبقى بنية الترانزستورات (عدد الحواف) كما هي ولن تتغير بنية خلية SRAM. ستبدأ شركة Samsung في إنتاج الرقائق باستخدام تقنية المعالجة ذات 4 نانومتر في مساحة 2021. في نفس العام ، وعدت الشركة ببدء الإنتاج المحفوف بالمخاطر باستخدام تقنية معالجة تبلغ 3 نانومتر.

وتزعم بعض المصادر الكورية الجنوبية أن هذا قد يحدث في وقت مبكر من عام 2020 ، وهو ما يبدو غير مرجح.

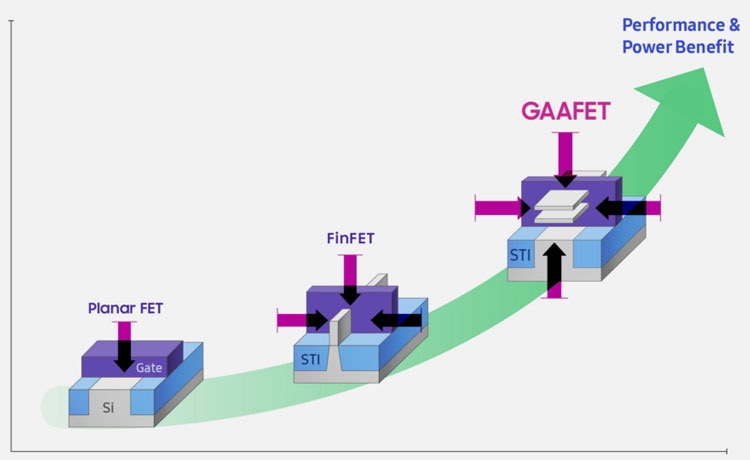

في هذا المقال ، نحن مهتمون بحقيقة أنه حتى تقنية المعالجة التي تبلغ مدتها 4 نانومتر ، ستستخدم Samsung ، ومن الواضح أن Intel و TSMC ، ترنزستورات FinFET - زعانف بوابات عالية ، يتم فيها اختراق قنوات القنوات العمودية وتثبيتها. في مثل هذه الترانزستورات ، يخترق المجال الكهرومغناطيسي للبوابة القنوات من ثلاث جهات ، وتوفر قناتان أو ثلاث قنوات في كل ترانزستور كليًا التيار اللازم لتشغيل الصمام.

/ صورة سامسونج

/ صورة سامسونجبدءاً من تقنية عملية 3nm ، ستعمل Samsung على كسر هذه الممارسة. سوف FinFET مفهوم التوقف عن العمل كما كان من قبل. ستكون بوابات الترانزستور FinFET صغيرة جدًا ولن تتمكن من تبديل الترانزستورات. إن الحاجة إلى تقليل الجهد الكهربائي لإمدادات الترانزستورات لن تؤدي إلا إلى تفاقم هذا الوضع. لذلك ، بالنسبة لتقنية المعالجة 3 نانومتر ، سيتم تقديم ترانزستور مع بوابة (محيط) حول حلقة GAA.

/ صورة سامسونج

/ صورة سامسونجأعطت سامسونج الترانزستور الجديد الاسم التجاري MBCFET (Multi Bridge Channel FET). في الممارسة العملية ، هذا هو تطور فكرة الترانزستور ، التي

تم إنشاؤها بشكل مشترك من قبل باحثين من IBM و Samsung و GlobalFoundries. كان من المفترض أن تشارك الترانزستور مماثلة في هيكل في الانتقال إلى تكنولوجيا العملية مع معايير 5 نانومتر. ولكن في الواقع ، لن يظهر هيكل الصمام هذا في الرقائق إلا مع بداية إنتاج Samsung الذي يبلغ طوله 3 نانومتر. سيتألف ترانزيستور MBCFET من قنوات مرتبة أفقياً فوق بعضها البعض في صورة نانوية ، بدلاً من التلال الرأسية ، كما في FinFET. سيتم التحكم في خصائص ترانزيستورات MBCFET بشكل ملائم من خلال تغيير عدد الصفحات الموجودة واحدة فوق الأخرى ، ومن خلال تغيير عرض الصفحة. كل صفحة هي قناة. سيحدد مجموع هذه المتغيرات الترانزستور الذي لدينا: قوة وسريعة ، أو ضعيفة ، ولكن منخفضة الطاقة. سيكون هناك أكثر من درجتين - من خمسة إلى سبعة.

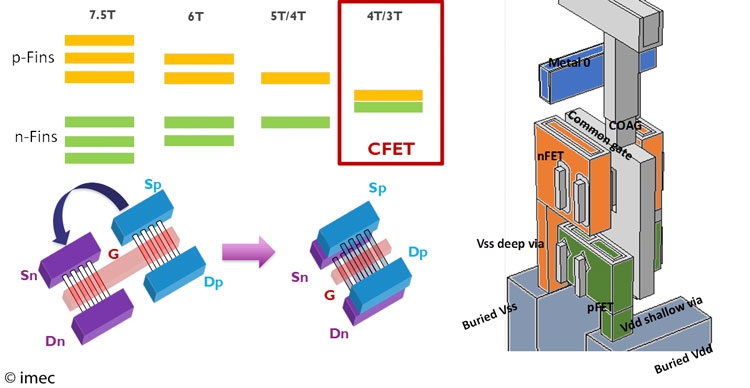

/ صورة سامسونج

/ صورة سامسونجالشيء الأكثر إثارة للاهتمام ، من أجل هذه المذكرة التي تم تصميمها ، هو أن ترانزستور MBCFET يمكن أن يظهر فقط في إطار تقنية المعالجة 3 نانومتر ، وسوف تتطلب تقنية العملية مع معايير 2 نانومتر مرة أخرى تغييرات في هيكل الترانزستور. تم اقتراح مثل هذا الترانزستور الجديد تحت اسم Forksheet من قبل مركز الأبحاث البلجيكي Imec. لأول مرة ،

تحدث ممثلو Imec بالتفصيل عن بنية الترانزستور مع صفحات منفصلة (نانو) هذا الربيع في حدث سنوي. لكن لا يمكنك إطعام العندليب مع الخرافات. كنا نشعر به. لا يمكنك الشعور به بعد ، لكن البلجيكيين أجروا محاكاة لترانزستور Forksheet على TCAD ، والذي تم

الإبلاغ عنه قبل ثلاثة أيام.

قبل النظر في البيانات ، نوضح أن الترانزستور Forksheet هو تعديل للترانزستور مع nanopages - نفس MBCFET أو Gate-All-Around ، إذا تجاهلنا المصطلحات Samsung. الزعانف العمودية في ترانزيستور Forksheet أوسع قليلاً من MBCFET ، لكن الأجزاء النانوية لقنوات الترانزستور تنقسم إلى قسمين ويفصل بينهما طبقة عازلة. في الواقع ، يتحول ترانزستور واحد MBCFET مع نقرة من المعصم إلى زوج ترانزيستور تكميلي من الترانزستورات p و n.

يدمر الهيكل المقترح حاجزًا خطيرًا في إغلاق الترانزستورات في شكل تعقيد لجعل الترانزستورات p و n أقرب ما يمكن وفي نفس الوقت يتجنب التأثير السلبي المتبادل للبوابات.

من الواضح أن النهج المقترح سيزيد من كثافة الترانزستورات على الرقاقة ، لكن النمذجة أظهرت أن الأداء واستهلاك الطاقة سوف يتحسنان أيضًا. سيؤدي التحول إلى ترانزستور ذو صفحات منفصلة إلى تقليل مساحة البلورة بنسبة تصل إلى 20٪ ، ومن خلال تقليل السعات والتسريبات الزائفة ، سيزداد أداء الأجهزة الإلكترونية بنسبة تصل إلى 10٪. إذا لم تقم بزيادة التردد ، فيمكنك تقليل استهلاك الطاقة بنسبة تصل إلى 24٪.

في المخزون ، لدى Imec

تقنية أخرى يمكنها زيادة كثافة الترانزستورات. يمكن تطبيقها على حد سواء في مرحلة إنتاج رقائق 3 نانومتر ، ومع معايير إنتاج أقل. والفكرة هي جعل زوج متكامل من الترانزستورات فوق بعضها البعض. تعد هذه العملية التي تبدو بسيطة بتقليل حجم كل من الخلية المنطقية القياسية وخلية SRAM بنسبة 50٪. متطورة واختبارها جزئيا على نماذج الأفكار تنتهي هنا.

قد يتطلب التحول إلى تقنية عملية تبلغ 1 نانومتر أيضًا بنية ترانزستور جديدة. في الوقت نفسه ، يجب أن نتذكر أن المهندسين يجدون في كثير من الأحيان أنه من الممكن تمديد سعادتهم - للوصول إلى شيء من هذا القبيل لاتخاذ خطوة أخرى إلى الأمام على العكازات القديمة.