مقال من موقع المهندس كريس فنتون المجنون

تعرف على ZedRipper ، وهو وحش من 16 نواة يعمل بسرعة 83 ميجاهرتز مدعوم من معالجات Z80 ، كما أنه سهل الحمل لأنه غير عملي. هذه هي محاولتي الأخيرة لتجميع جهاز كمبيوتر للمتعة ، وإرضاء عدة رغبات مرة واحدة:

- وأخيرا ، استخدم FPGA العملاق ، الذي كان يكذب معي الخمول.

- العب تاريخًا بديلاً لإنشاء أجهزة الكمبيوتر ، مع تناول مسألة تعدد المهام من منظور الحديد.

- قم بتجميع جهاز كمبيوتر يمكنني من خلاله كتابة برامج قصيرة مضحكة في طريقها للعمل في القطار.

- قم بتجميع منصة يمكن من خلالها إجراء تجارب بسيطة نسبيًا على هندسة الكمبيوتر.

صور براقة

إذا لم يكن لديك الوقت الكافي لقراءة ورقة نصية حول بنية الكمبيوتر غير العملية ...

إذن ما هذا الوحش؟

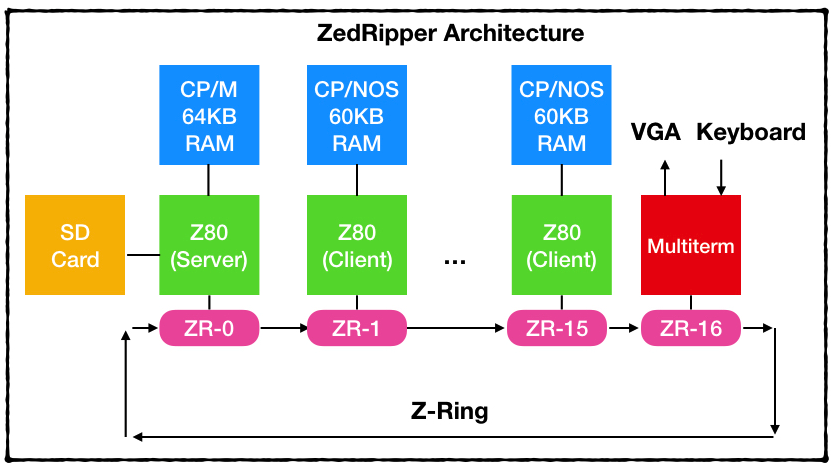

ZedRipper هو نتيجة لمحاولة إنشاء أروع جهاز كمبيوتر باستخدام CP / M 2.2:

- 16 معالجات Z80 تعمل على تردد 83.33 ميغاهيرتز.

- 64 كيلوبايت من الذاكرة المخصصة لكل Z80.

- ANSI متوافق مع مسرع المحطة مع 16 مخرجات.

- يتم توصيل جميع المعالجات والأجهزة بواسطة شبكة رنين أحادية الاتجاه متزامنة تمامًا تعمل بسرعة 83 ميجاهرتز.

- محرك أقراص سعة 128 ميجابايت على بطاقة SD (محركات أقراص مقاس 16 × 8 ميجابايت في وحدة التحكم في الصوت / التحكم).

- نواة "خادم" تصل إلى CP / M 2.2 وتقوم بتشغيل خادم ملفات CP / NET (مكتوب في Turbo Pascal 3 على الكمبيوتر نفسه!) ، والذي يوفر الوصول المشترك إلى بطاقة SD.

- 15 حبات "العميل" تطلق CP / NOS من ROM. كل عميل لديه حق الوصول إلى مستودع مشترك ، ويمكن للجميع تشغيل أي برامج CP / M 2.2 دون التنافس على الموارد مع نواة أخرى.

طريق آخر

هل هي لعبة الشطرنج و Planetfall التي تصرف انتباهي عن محرر Turbo Pascal الخاص بي؟

هل هي لعبة الشطرنج و Planetfall التي تصرف انتباهي عن محرر Turbo Pascal الخاص بي؟بعد مغامراتي مع

نقل الألعاب إلى Kaypro ، كان لدي انطباع دافئ بشكل مدهش عن نظام التشغيل البدائي هذا قبل 40 عامًا ، وكان لدي فكرة أنني قررت تطويرها: ماذا لو تحولت القصة في الاتجاه المعاكس ، وسيستمر جهاز الكمبيوتر مسارات التنمية مع وحدات المعالجة المركزية متعددة على الفور؟ حتى في الثمانينيات من القرن الماضي ، كانت المعالجات نفسها (وقريباً RAM) غير مكلفة نسبيًا ، لكن تعدد المهام في أجهزة الكمبيوتر الشخصية كان يعتمد فقط على قطع أطوال الوقت عندما تم تقسيم مورد كبير (RAM أو CPU) بين البرامج المنافسة. لم يستطع Iron التعامل مع هذا الأمر (وكان من الصعب للغاية جعل البرامج تتصرف بشكل جيد في أنظمة التشغيل مثل DOS) حتى انتقلنا إلى عصر 386s وأجهزة الكمبيوتر المزودة بأكثر من 4 ميغابايت من الذاكرة.

خلال هواياتي التاريخية مع أجهزة الكمبيوتر ، صادفتني شيئًا مثيرًا للاهتمام بالنسبة لي: في المراحل الأولى من التطوير ، دعم نظام التشغيل

CP / M OS إصدار "شبكة" يسمى CP / NET. لا يزال معظم الناس يعرفون فكرتها اليوم - وضع المكتب في واحد أو اثنين من الأجهزة "الحقيقية" مع محركات أقراص كبيرة وطابعات ، وسيتم تقاسم مواردها بين عملاء رفيعين ومحطات طرفية مع وحدة المعالجة المركزية وذاكرة الوصول العشوائي. سيعمل كل مستخدم كما لو كان لديه جهاز خاص به يشغل CP / M مع إمكانية الوصول إلى الأقراص والطابعات الكبيرة.

كما ذكرت ، وحدة المعالجة المركزية وذاكرة الوصول العشوائي (عادةً كان Z80 64 كيلو بايت من DRAM) لم تكن باهظة الثمن بشكل خاص ، ولكن جميع pribluds الخارجية اللازمة لإنشاء جهاز كمبيوتر مفيد (محركات الأقراص والطابعات والشاشات ، ..) إضافة إلى التكلفة الإجمالية. في ذلك الوقت ، بدا أن إضافة عدة وحدات المعالجة المركزية (RAM) / وحدات ذاكرة الوصول العشوائي (RAM) إلى جهاز كمبيوتر يعد طريقة منحلة إلى حد ما لتزويد مستخدم واحد بوحدات معالجة مركزية وذاكرة وصول عشوائي متعددة. حتى CP / M قد قطعت الطريق لتقسيم طول الوقت ل MP / M OS.

لقد وجدت أن Exidy قد اقتربت من ذلك - في عام 1981 ، أطلقوا جهاز Multi-NET 80 الخاص بهم ، والذي سمح بإضافة ما يصل إلى 16 بطاقة ، وكان لكل واحدة منها Z80 و RAM. ومع ذلك ، فقد تم تصميمه للعمل لما يصل إلى 16 مستخدمًا فرديًا ، وليس لعمل مستخدم واحد أطلق 16 برنامجًا في وقت واحد.

قريب جدا ...

قريب جدا ...بسرعة إلى الأمام 40 سنة - انخفضت الترانزستورات في الواقع في السعر. بعد إغلاق المختبر ، ورثت العديد من FPGAs وحشية (Stratix IV 530GX) ، وأعتقد أنه سيكون من المثير للاهتمام للغاية أن تفعل مع واحد منهم. في مرحلة ما ، صادفت مشروعًا مثيرًا للاهتمام من قِبل Grant Searle

Multi-Comp ، وكان من السهل جدًا تجميع ماكينة تعمل مع CP / M ووحدة CPU واحدة. لكنني كنت بحاجة إلى المزيد. قررت أن أعرف ما إذا كان بإمكاني إنشاء جهاز متعدد النواة على جهاز CP / M باستخدام مهام متعددة حقيقية - لا يوجد أي شيء صعب أو مجرد قوة قاسية.

نحن تكوين وتشغيل البرنامج

في هذا المشروع ، ركزت بشكل أساسي على الأجهزة ، ولم أكتب سطرًا واحدًا من التعليمات البرمجية في المجمّع. يتم تحميل CPU 0 مباشرةً من ROM ، الذي أخذته من Grant ، ويتم تحميل العقد المتبقية من 4KB CP / NOS ROM ، والتي أخذتها من محاكي Atari.

ينتظر كلا ROMs اتصالاً بمحطة طرفية تسلسلية عبر واجهة قياسية ، بينما يتوقع عملاء CP / NOS منفذ تسلسلي آخر متصل بخادم. من السهل تصميم منطقك الخاص على مثل هذه FPGAs الكبيرة. لقد قمت بتطوير منطق فك تشفير العنوان الخاص بي ، وذلك بفضل ظهور Z-Ring لكل وحدة CPU في مخطط تعيين العناوين عند الضرورة.

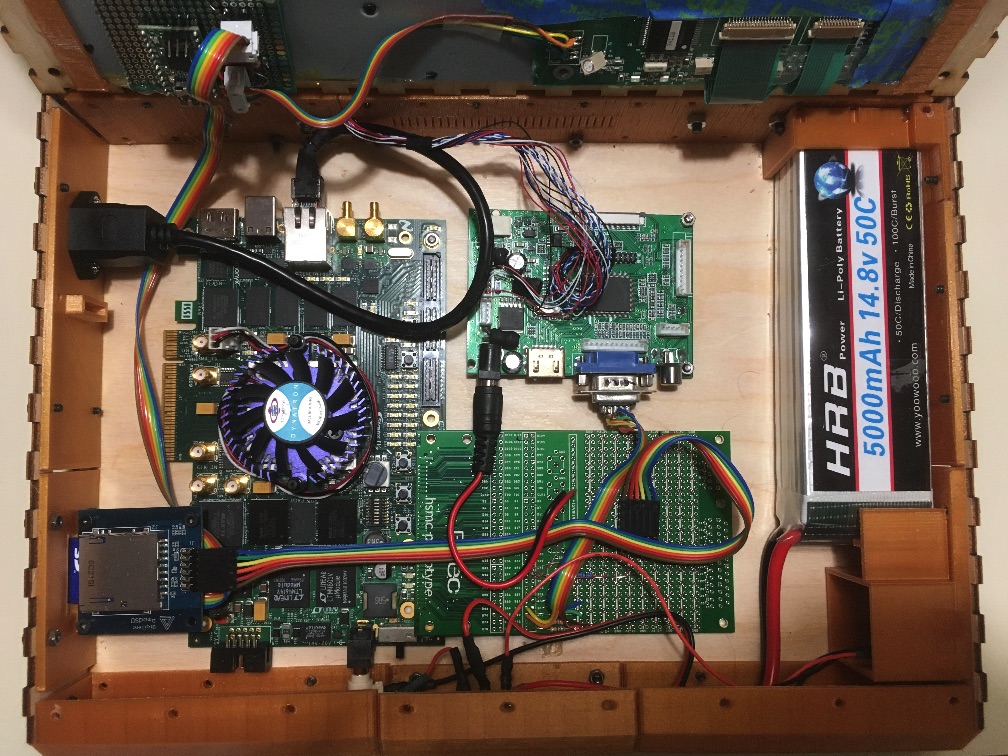

الدواخل

قلب ZedRipper هو واحد من هذه FATGA الضخمة Stratix IV 530GX. يتم استخدام بطاقة HSMC للعرض ، واستقبال البيانات من وحدة تحكم لوحة المفاتيح والاتصال ببطاقة SD. يتم استخدام Ethernet لتنزيل البرنامج الثابت ، لذلك يوجد مثل هذا المنفذ على جانب العلبة ، إلى جانب محول بطاقة SD وفتحة لمنفذ تسلسلي خارجي (لم يتم استخدامه بعد).

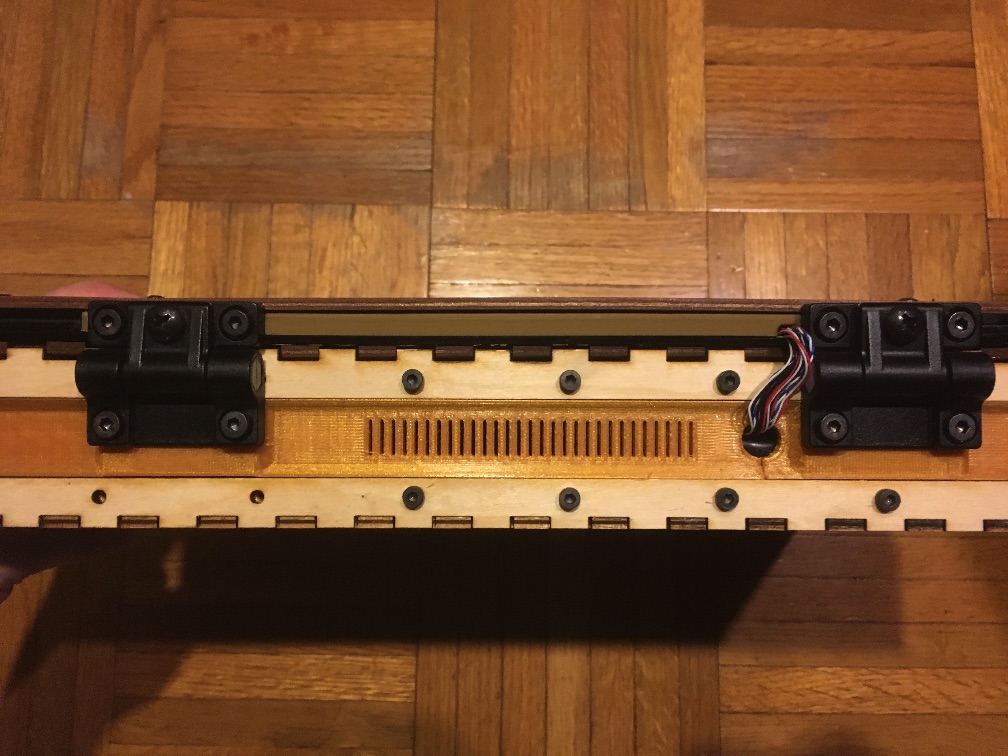

لوحة المفاتيح والتحكم

لوحة المفاتيح وثقب في المقدمة ، حيث سيتم تثبيت جهاز تحديد المواقع لاحقًا

لوحة المفاتيح وثقب في المقدمة ، حيث سيتم تثبيت جهاز تحديد المواقع لاحقًاكان لدي لوحة مفاتيح PS / 2 مدمجة (من أحد مشاريعي القديمة مع جهاز كمبيوتر محمول) ، وأردت توصيله بـ 2.5 V I / O الخاص بي في FPGA. قررت أن أذهب إلى الطريق السهل وأضف متحكم Teensy 2.0 إلى الحزمة.

تحكم الساخنة الغراء في الجزء السفلي من لوحة المفاتيح

تحكم الساخنة الغراء في الجزء السفلي من لوحة المفاتيحوقد جعل ذلك من الممكن ترجمة PS / 2 إلى ASCII ، وكذلك تمييز بعض المفاتيح الإضافية (F1-F12) بسهولة إلى تسلسلات "سحرية" للأوامر الطرفية ، لمزيد من الراحة. ثم توفر وحدة التحكم Z80 بايت لـ UART بسرعة 9600 باود (باستخدام مقسم جهد بسيط يتغير من 5 فولت إلى 2.5 فولت من أجل FPGA). بالنظر إلى أن هذا المشروع قد تم تجميعه من مختلف النفايات في ورشة العمل الخاصة بي ، فقد كان حلاً مناسبًا أظهر نفسه جيدًا في العمل.

عرض

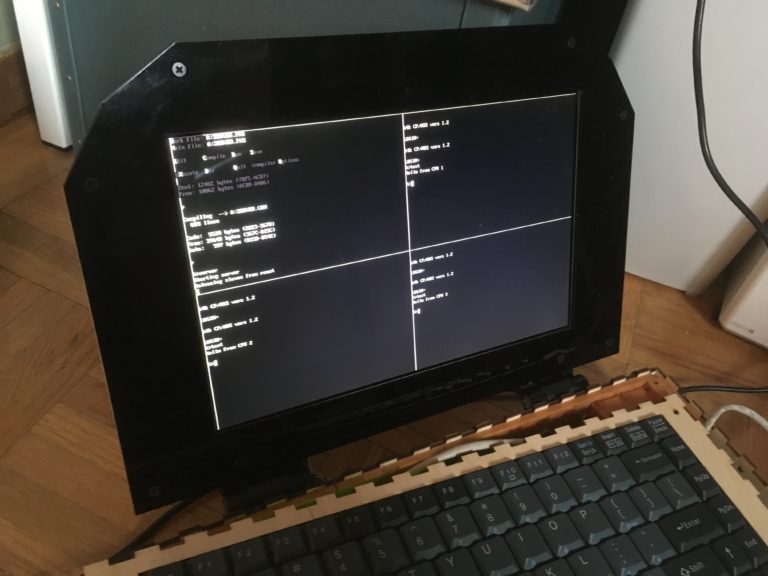

شاشة التحميل ، يعمل الخادم في الزاوية العلوية اليسرى ، وتعمل ثلاثة برامج مختلفة للمستخدم على نواة منفصلة

شاشة التحميل ، يعمل الخادم في الزاوية العلوية اليسرى ، وتعمل ثلاثة برامج مختلفة للمستخدم على نواة منفصلةميزات الشاشة: 1280 × 800 10.1 ″ ، وتفهم VGA. يستخدم FPGA شبكة بسيطة من المقاومات لتقديم ما يصل إلى 64 لونًا (R2G2B2). تتطلب الشاشة جهاز توقيت يبلغ 83.33 ميجاهرتز (1280 × 800 @ 60 هرتز) ، لذلك من أجل البساطة ، تعمل الدائرة بأكملها عند هذا التردد.

يحتوي مشروع Grant ، Multicomp ، على كود VHDL لمحطة بسيطة متوافقة مع ANSI. أعدت كتابة منطقها على Verilog ، ثم طورت وحدة تحكم فيديو تدعم 16 محطة مستقلة متصلة عبر عقدة Z-Ring. تُعد شاشة العرض 1280 × 800 عرضًا بحجم 160 × 50 حرفًا (بخط 8 × 16) ، ويعمل كل جهاز طرفية على شكل "Sprite" بحجم 80 × 25 يمكن نقله في أي مكان على الشاشة (مع قائمة أولويات ضبط تسلسل عرض المحطة الطرفية). نظرًا لأن كل محطة تعمل بشكل مستقل عن الأجهزة الأخرى ، فإن لديها جهاز الحالة الخاص بها ، مع 2 كيلوبايت من ذاكرة الوصول العشوائي للأحرف و 2 كيلوبايت من "السمات" (لتخزين معلومات الألوان). يدعم كل حرف ألوان الخلفية والحروف 4 بت. نظرًا لأن جميع المحطات الطرفية يجب أن تحتوي على أحرف المسافة البادئة نفسها ، ويمكن أن تحتوي خلية 8x16 على حرف واحد فقط ، يمكن لجميع المحطات استخدام نفس ذاكرة القراءة فقط 2 كيلو بايت التي تحتوي على خط. بشكل عام ، يستخدم منطق العرض حوالي 66 كيلو بايت من كتلة RAM.

بشكل عام ، أحصل على مدير نوافذ بسيط للغاية لمحطات CP / M الخاصة بي ، والتي تعمل بشكل كامل تقريبًا بسبب الأجهزة. يعد هذا أحد أغنى المناطق للبحث - حتى الآن ، فإن وحدة المعالجة المركزية للخادم فقط هي القادرة على إعادة ترتيب المحطات الطرفية ، لكن لدي خطط بعيدة المدى لإضافة جهاز لتحديد المواقع مثل الماوس ، والذي يسمح باستخدام أجهزة Windows فقط لسحب النوافذ وتغيير أولوية شاشات العرض.

نظرًا لأن وحدة التحكم الطرفية ليست سوى واحدة من العقد Z-Ring (وإعادة توجيه هذه الواجهة إلى أي من Z80 أمر بسيط للغاية) ، فمن بين الخطط المستقبلية ، من الممكن إضافة محطة "ملء الشاشة" 160 × 50 (ربما كخلفية ") ، وشاشة عرض حقيقية 1280 × 800 × 64 ألوان مع SRAM خارجي سريع على السبورة.

Z-الدائري

كيفية وضع مجموعة من Z80؟ في عملي ، تعلمت بحزم شيئًا واحدًا: تطوير الشبكات أمر صعب. الأهداف العامة لهذه الشبكة هي:

- تنفيذ بسيط.

- واجهة بسيطة

- التمدد التعسفي.

- الأداء الكافي.

كما ذكرت ، تتوقع Z80s الخاصة بي الاتصال بالمنافذ التسلسلية ، لذلك كانت الواجهة بسيطة جدًا للقيام بها - يجب أن يتم إخفاءها كمنفذ تسلسلي! بشكل أساسي ، Z-Ring هي شبكة رنين متزامن أحادي الاتجاه تستخدم "أرصدة" للتحكم في التدفق. تحتوي كل عقدة على مخزن مؤقت وارد 1 بايت لكل من العقد الأخرى في الشبكة. بعد إعادة التعيين ، تحتوي كل عقدة على "رصيد" واحد لكل عقد شبكة متبقية. يتم تحديد المخطط ، وبالتالي فإنه يمكن توسيعه بسهولة إلى مئات العقد مع إضافة مقدار صغير جدًا من المنطق ، ومع ذلك ، تدعم Z-Ring اليوم ما يصل إلى 32 عقدة (وبالتالي ، تحتاج كل عقدة إلى مخزن مؤقت 32 بايت).

يتكون "ناقل" نفسه من بت الصلاحية ، معرف "مصدر" ، معرف "هدف" ، وحمولة 1 بايت (19 بت). أعتقد أنه سيكون من السهل جدًا تطبيقه باستخدام منطق TTL (إذا فشل شخص ما في عام 1981 ولم يتمكن من العثور على FPGA). تحتوي كل "عقدة" على خطي أنابيب لمشغلات الحافلات - 0 و 1 مراحل - وعند إدخال رسالة ، تنتظر حتى تصبح المرحلة 0 خالية ، ثم يتم دمجها في المرحلة الأولى. يتم إدخال الرسائل على العقدة المصدر وتنتقل حول الحلبة حتى تصل إلى الهدف ، وبعد ذلك تجد نفسها في المخزن المؤقت المناسب وتحديث علامة جاهزية البيانات. عندما تقرأ العقدة المستقبِلة المخزن المؤقت ، فإنها تدخل الرسالة الأصلية ، التي تستمر في التنقل حول الحلبة حتى تصل إلى المصدر مرة أخرى ، وتعيد "الرصيد". إذا قمت بإرسال الحزمة إلى عنوان غير موجود ، فسيتم إرجاع القرض تلقائيًا بعد دائرة كاملة.

نظرًا لأن كل توقف على الحلقة يتكون من مرحلتين ناقل ، ولا يوجد ضغط خلفي ، لا تستغرق كل رسالة أكثر من 2 * (عدد العقد) دورات التسليم. يحتوي التطبيق الحالي على 17 عقدة (16 وحدة تحكم في وحدة العرض / لوحة المفاتيح + وحدة تحكم) ، ويعمل على جهاز ضبط وقت يصل إلى 12 نانوثانية ، لذلك يستغرق الأمر حوالي 400 نانو ثانية لإيصال رسالة وإرجاع قرض. يمكن لوحدة التحكم في العرض أن ترسل حركة المرور بمعدل وصول ، بحيث يكون لكل وحدة CPU نطاق ترددي يتراوح من 2 إلى 2.5 ميجا بت / ثانية إلى طرفه (يمر الحافلة بما يكفي لتوفير جميع وحدات المعالجة المركزية البالغ عددها 16 وحدة) ، وهو عدد كبير للغاية بالنسبة للأجهزة الطرفية.

في التكوين الحالي ، كل شيء يعمل بشكل جيد ، ولكن يمكنك إجراء بعض التحسينات الواضحة:

- لتعميق المخازن المؤقتة المستقبلة ، مما سيزيد من إنتاجية العقد - على FPGA هناك العديد من الكتل المجانية من 1 كيلوبايت من ذاكرة الوصول العشوائي ، والتي ستدعم 32 عقدة مع 32 ساعة معتمدة ، بحيث يمكن لكل وحدة المعالجة المركزية من الناحية النظرية تشبع الناقل.

- إضافة دعم لوضع العنوان. ستسمح إضافة عناوين 16 بت (أو أكثر) بالوصول المباشر إلى الذاكرة (DMA) (وستكون إضافة DMA إلى كل عقدة بسيطة). يحتوي FPGA على كمية كبيرة من الأجهزة الإضافية (بضع ميغا بايت من ذاكرة الوصول العشوائي الساكنة وحوالي جيجابايت من DDR3).

- إضافة التحكم في التدفق (والتخزين المؤقت) بين العقد.

ولكن كل هذا يمكن أن تنتظر حتى أوقات أفضل.

السلطة!

تتطلب لوحة تصحيح الأخطاء مع FPGA طاقة إدخال 12-20 فولت ، والشاشة تحتاج إلى 12 فولت ، ولوحة المفاتيح وجهاز التحكم يحتاجان إلى 5 فولت. من المريح أن FPGA يحتوي على وحدات تحكم 3.3 و 5 و 12 فولت ، والتي يسهل الاتصال بها ، لذلك تستقبل FPGA الطاقة مباشرة من بطارية ليثيوم بوليمر بسرعة 5000 مللي أمبير في الساعة بجهد يبلغ 14.4 فولت ، ثم تقوم بتوزيع الطاقة على جميع الأجهزة الأخرى. كانت إحدى الصعوبات هي أنني لم أرغب في تفكيك الكمبيوتر المحمول في كل مرة لشحنها ، لكن البطارية بها موصل طاقة + / طبيعي ، بالإضافة إلى موصل "موازنة" متصل بكل خلية على حدة. الحل الأمثل هو أن زر الطاقة يقوم بتبديل اتصال البطارية بين طاقة FPGA وموصل الشحن الموجود في العطلة المغلقة بواسطة غطاء منزلق. ليست مريحة للغاية ، ولكن يمكنك فقط تحريك الغطاء وسحب الموصلات من هناك لتوصيلها بالتكلفة دون استخدام مفاتيح سداسي عشرية.

شحن تبدو غريبة

شحن تبدو غريبةلم أختبر البطارية تمامًا ، ولكنها تدوم 3 ساعات على الأقل (وهو أكثر من كافٍ لتغطية ركوب القطار الخاص بي). على الأرجح ، سيستغرق حوالي 6 ساعات دون أي الأمثل للاستهلاك. لا يدعم الاستخدام في نفس الوقت مثل الشحن ، ومع ذلك ، يعمل الكمبيوتر المحمول على طاقة البطارية لفترة كافية بحيث لا يمثل ذلك مشكلة.

إسكان

حالة تصميم "الهاكر" القياسي هي مزيج من الخشب الرقائقي المقطوع بالليزر 3 مم والبلاستيك المطبوع على طابعة ثلاثية الأبعاد. لقد قمت بتحميل الشاشة على مفصلات ، لذلك في الحقيقة يبدو وكأنه جهاز كمبيوتر محمول عادي ، وإن كان بطيئًا إلى حد ما. كنت أرغب في إعطائها مظهرًا في الثمانينيات ، لذا فإن الزوايا العلوية من الشاشة تشبه إلى حد ما كراي ، ويتكون حامل الجلد المزيف تحت المعصمين. حافة الخشب الرقائقي قطع الليزر غير سارة للغاية بالنسبة لليدين ، لذلك كان هذا الموقف وظيفية بشكل مدهش.

سرعة

لم أجرب معيارًا واحدًا خاصًا بـ CP / M (أفترض أنهم يفعلون ذلك ، لكنني لم أبحث عنه بشكل خاص). منذ صنع هذا الجهاز لكتابة برامج في Turbo Pascal ، جربت العديد من الاختبارات المصغرة للسرعة. لقد تحولت إلى 15-35 كيلو بايت من عمليات الفاصلة العائمة في الثانية (باستخدام النوع الحقيقي 48 بت في TP) ، وحوالي مليون من العمليات الصحيحة في الثانية (مع نوع عدد صحيح 16 بت). ليس سيئًا بالنسبة لوحدة المعالجة المركزية 8 بت وبيئة برمجة ملائمة بدرجة كافية.

مشروع مثير للاهتمام للمستقبل قد يكون تطوير مسرع لعمليات الفاصلة العائمة.

FPGA التخلص

كل المنطق ، كما قلت سابقًا ، خفيف الوزن إلى حد ما ، ويستهلك حوالي 7٪ فقط من موارد الرقاقة (على الرغم من أن 40٪ من إجمالي ذاكرة الوصول العشوائي للكتل و 100٪ من ذاكرة الوصول العشوائي M144k).

- الدمج التجميعي 31،808 / 424،960 (7٪)

- الذاكرة تقريبًا 0 / 212،480 (0٪)

- سجلات المنطق المخصص 10،231 / 424،960 (2٪)

- استخدام المنطق 10 ٪

- مجموع السجلات 10231

- إجمالي عدد وحدات ذاكرة الكتل 9،005،056 / 21،233،664 (42٪)

- كتلة DSP عناصر 18 بت 0/1024 (0٪)

الخطط المستقبلية

في خططي المباشرة (أي أن الحديد موجود بالفعل في ورشة العمل ، فأنت تحتاج فقط إلى العثور على الوقت المناسب لحام):

- تلوين كل شيء. يتكون الكمبيوتر المحمول من الخشب الرقائقي ، وأريد حقًا تغطيته بشيء ما.

- جهاز تحديد المواقع المقود توصيله إلى وحدة تحكم لوحة المفاتيح.

- تتبع البطارية. يجعل ADC على وحدة تحكم لوحة المفاتيح من السهل تتبع البطارية ، بحيث يمكنني أن أفهم مستوى الشحن.

- WiFi - لدي ESP32 ملقاة لإطلاق Zimodem! جنبا إلى جنب مع الهاتف في وضع نقطة الوصول ، ينبغي أن يسمح لي ذلك بالاتصال بالإنترنت أثناء التنقل. هناك تطبيقات طرفية جيدة لـ CP / M ، لكن سيكون من الجيد كتابة شيء مثل عميل IRC أو متصفح ويب بسيط. سيكون أيضًا مناسبًا استخدام بروتوكول نقل الملفات Kermit إلى كمبيوتر Linux حديث.

- المنفذ التسلسلي ، الذي يمكن الوصول إليه من الخارج ، للاتصال بجهاز آخر (تمت طباعة موصل بالفعل من أجله ، يجب فقط لحامه).

- الصمام تشير إلى الوضع الحالي. بالنسبة له ، يوجد بالفعل ثقب في المقدمة - أخطط الآن لتوصيله بإشارة الوصول إلى بطاقة SD.

على المدى الطويل ، أتطلع إلى أفكار الحديد المختلفة ، والتي ستكون ممتعة لتجربة:

- كم يمكنك رفع تردد التشغيل Z80؟ تتمثل الخطوة الأولى في إلغاء سرعة المعالج من مؤقت البيكسل ، ومع ذلك سيكون من المثير للاهتمام أيضًا محاولة تطبيق تقنيات الكمبيوتر الحديثة على Z80 (خطوط الأنابيب ، إعادة تسمية السجل ، تنبؤ الانتقال ، إلخ).

- قد يكون من المثير للاهتمام إضافة مسرعات خاصة لأشياء مثل عمليات الفاصلة العائمة. هناك 1024 من كتل DSP غير المستخدمة على الرقاقة ، وأعتقد أنه لم يحاول أحد إنشاء مسرع لتنسيق Real 48 بت في TP.

- استخدام الحديد الموجودة! لا يزال لدي مجموعة من الذاكرة غير المستخدمة ، وهي:

- 512 ميجابايت DDR3 SDRAM مع ناقل بيانات 64 بت

- 128 ميغابايت DDR3 SDRAM مع ناقل بيانات 16 بت

- اثنان 4 ميغابايت QDR II + SRAMs مع ناقل بيانات 18 بت

- 64 ميجابايت فلاش

- 2 ميغابايت SSRAM

- تحسين الفيديو! تتمثل الخطوة الأولى في إضافة دعم للمحطة "ذات الشاشة الكاملة" 160 × 50 ، والقدرة على التوسع إلى محطة عادية 80 × 25 مرتين. باستخدام SSRAM خارجي سيضيف ببساطة وضع 1280 × 800 @ 6 بت.

- توسيع قدرات المحطة الحالية. أعتقد أنه يمكنني إضافة التوافق مع محطة مثل ADM-3A (وإضافة دعم الرسومات) ، والذي يتم استخدامه في Kaypro / 84 ، وبعد ذلك سيكون بإمكاني الوصول إلى مجموعة واسعة من البرامج (ولن أحتاج إلى منفذ DD9).

النتائج

حتى الآن ، كانت السيارة تعمل لبضعة أيام فقط ، لكن يمكنني القول أنني أحب كل شيء حقًا. الشاشة جميلة وواضحة ، لوحة المفاتيح كبيرة ومريحة ، والجسم ضخم ، ولكنه يزن قليلاً (ويناسب حقيبة الظهر). كان الكمبيوتر المحمول مريحًا بشكل مدهش للعمل في القطار.

أعتقد أنني على الطريق الصحيح. تعتبر القدرة على فتح محرر نصي في نافذة واحدة لتدوين الملاحظات أثناء تصحيح الأخطاء على TP في نافذة أخرى مريحة للغاية (أو القدرة على تدوين الملاحظات أثناء تشغيل Zork!). هناك شعور بأن مثل هذا النهج لإنشاء أجهزة كمبيوتر متعددة المهام منخفضة التكلفة على أساس CP / M يمكن أن توجد.

تريد بناء نفسه؟

حتى الآن ، ليس لدي طريقة سهلة للحصول على الملفات من الجهاز ، لذا فإن الجزء الأكثر فائدة من البرنامج (خادم ملفات CP / Net المكتوب في Turbo Pascal) محاصر. ابق معنا وابق معنا (أو اكتب لي

بريدًا إلكترونيًا إذا كنت لا تستطيع الانتظار على الإطلاق). - , , XXI github. , « ».