Cadence wird Genus auf Seminaren zur Chipentwicklung in St. Petersburg und Zelenograd vorstellen

Nachrichten von befreundeten Organisationen (Cadence, MIET, ITMO, NPC Elvis und andere):Cadence Design Systems, eines der beiden weltweit größten Unternehmen auf dem Gebiet der Automatisierung der Mikrochip-Entwicklung, wird vom 15. bis 16. Oktober Seminare am Moskauer Institut für elektronische Technologie (MIET) in Zelenograd und St. Petersburg durchführen ITMO University, wo (nach den Erfahrungen meiner Reise im Jahr 2012) Studenten Verilog und Systeme auf einem Chip sehr gut verstehen.Drei russische Unternehmen, Elekropribor, NIIMA Progress und SPC Elvis, werden ebenfalls an den Seminaren teilnehmen. Lesen Sie den Artikel über die Zusammenarbeit mit Imagination Technologies des entsprechenden Elvis-Forschungs- und Entwicklungszentrums der Elvis-Neotech-Organisation auf der Rusnano-Website.Unter den Präsentationen empfehle ich persönlich, sich das neue Genus-Synthese-Tool anzusehen - ich habe seine Präsentation im Juni auf der Design Automation-Konferenz in San Francisco gesehen und gedreht:

Die Ankündigung, die ich über das russische Seminar erhalten habe, ist unten. Auf dem Foto rechts - Ich bin vor dem Hintergrund des MIET-Gebäudes in Zelenograd während einer Reise mit MIPS Technologies im Jahr 2011. Dort werden Leute aus Cadence einen der Workshops abhalten:

Cadence Technology Days 15- 16- . : kustarev@yandex.ru. : dsd@miee.ru.

: , .. 14 « »

:

Technology day at ITMO – Seminar Title:

Virtual Model Prototyping, High Level Synthesis, Synthesis and Digital Implementation by Cadence

9:15 – 9:45 Welcome and Cadence Overview

9:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 -11:30 Break

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 Lunch

13:30 – 14:30 Cadence: Genus the new synthesis solution

14:30 – 15:30 Cadence: Innovus – state of the art digital implementation

15:30 – 15:45 Break

15:45 – 16:45 “» — experience with Cadence tools

16:45 – 17:45

17:45 – 18:15 Round table and open discussions with the speakers

:

09:00 – 09:15 .

09:15 – 09:45 Cadence; 0:30 hour.

09:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 – 11:30 – .

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 .

13:30 – 14:45 Cadence: Genus the new synthesis solution

14:45 – 15:00 – .

15:00 – 16:15 Cadence: Innovus – state of the art digital implementation

16:15 – 16:45 « «» – Cadence

16:45 – 17:15 «» – Cadence Incisive .

17:15 – 18:00 , .

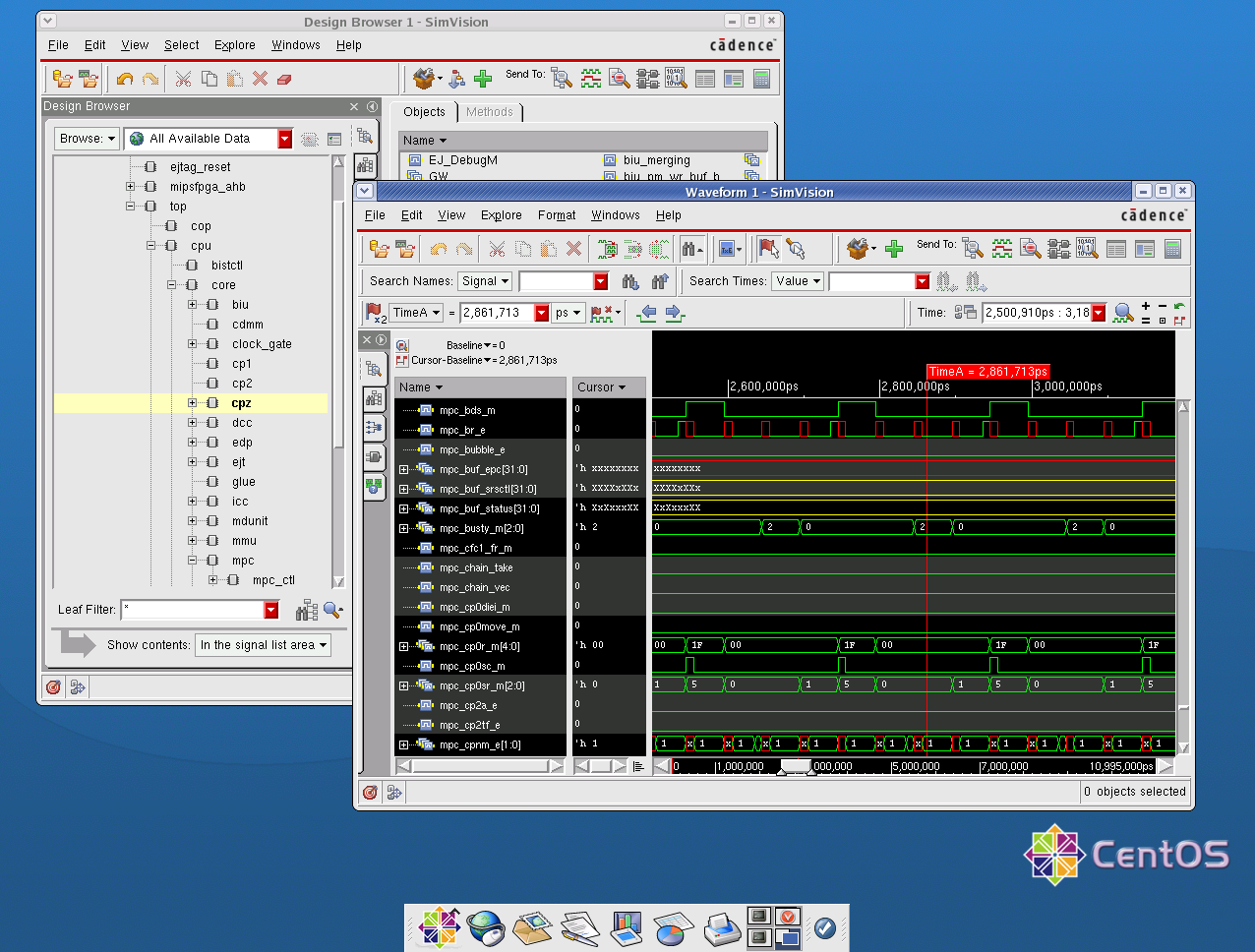

Cadence. MIPS microAptiv UP MIPSfpga SimVision:

Source: https://habr.com/ru/post/de384913/

All Articles