T1 - Diskreter 8-Bit-DIY-Computer

Es gab schon immer viele "hausgemachte". Mit dem Aufkommen des Netzwerks organisierten sich Liebhaber, die etwas mit ihren eigenen Händen tun wollten, sofort und schufen viele Arten von Communities, Foren und anderen Orten, an denen Sie mit Ihrer eigenen Art chatten können. Dank dessen erscheinen regelmäßig interessante Werke im Internet, von denen einige besonders beachtet werden sollten.Eine solche Arbeit ist insbesondere ein Projekt zur Schaffung eines diskreten 8-Bit-Computers. Der Autor des Projekts ist Andrew Starr , und das Projekt selbst befindet sich hier auf dieser Seite . Wie ist ein Projekt?Laut dem Autor handelt es sich teilweise um eine kinetische Zusammenstellung, teilweise um eine Hommage an die Errungenschaften von Wissenschaft und Technologie und die Errungenschaften der vergangenen Jahre. Zum Teil ist dies ein Bildungsprojekt.Um dieses System zu erstellen, verwendet der Autor die folgenden Elemente:

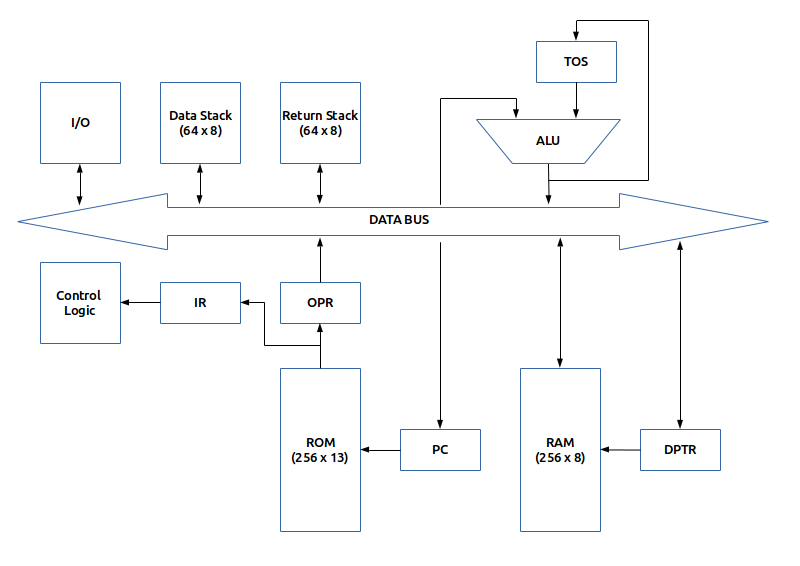

Es gab schon immer viele "hausgemachte". Mit dem Aufkommen des Netzwerks organisierten sich Liebhaber, die etwas mit ihren eigenen Händen tun wollten, sofort und schufen viele Arten von Communities, Foren und anderen Orten, an denen Sie mit Ihrer eigenen Art chatten können. Dank dessen erscheinen regelmäßig interessante Werke im Internet, von denen einige besonders beachtet werden sollten.Eine solche Arbeit ist insbesondere ein Projekt zur Schaffung eines diskreten 8-Bit-Computers. Der Autor des Projekts ist Andrew Starr , und das Projekt selbst befindet sich hier auf dieser Seite . Wie ist ein Projekt?Laut dem Autor handelt es sich teilweise um eine kinetische Zusammenstellung, teilweise um eine Hommage an die Errungenschaften von Wissenschaft und Technologie und die Errungenschaften der vergangenen Jahre. Zum Teil ist dies ein Bildungsprojekt.Um dieses System zu erstellen, verwendet der Autor die folgenden Elemente:- 8-Bit-Bus

- 2 * 64-Bit-Stapel (Daten, Rückgabe);

- Harvard-Architektur : 256-Byte-Hauptspeicher und 256-Wort-Programmspeicher;

- 13-Bit-Software-Befehlswort: 5 Bit pro Opcode, 8-Bit-Operand;

- Alle Speicherelemente werden mit Ferritkernen hergestellt.

- Der Programmspeicher wird mit Ferrittransformatoren erstellt.

- Logikelemente bestehen aus diskreten Elementen in Form von Plug-In-Modulen.

- Die Zieltaktfrequenz beträgt 1 MHz.

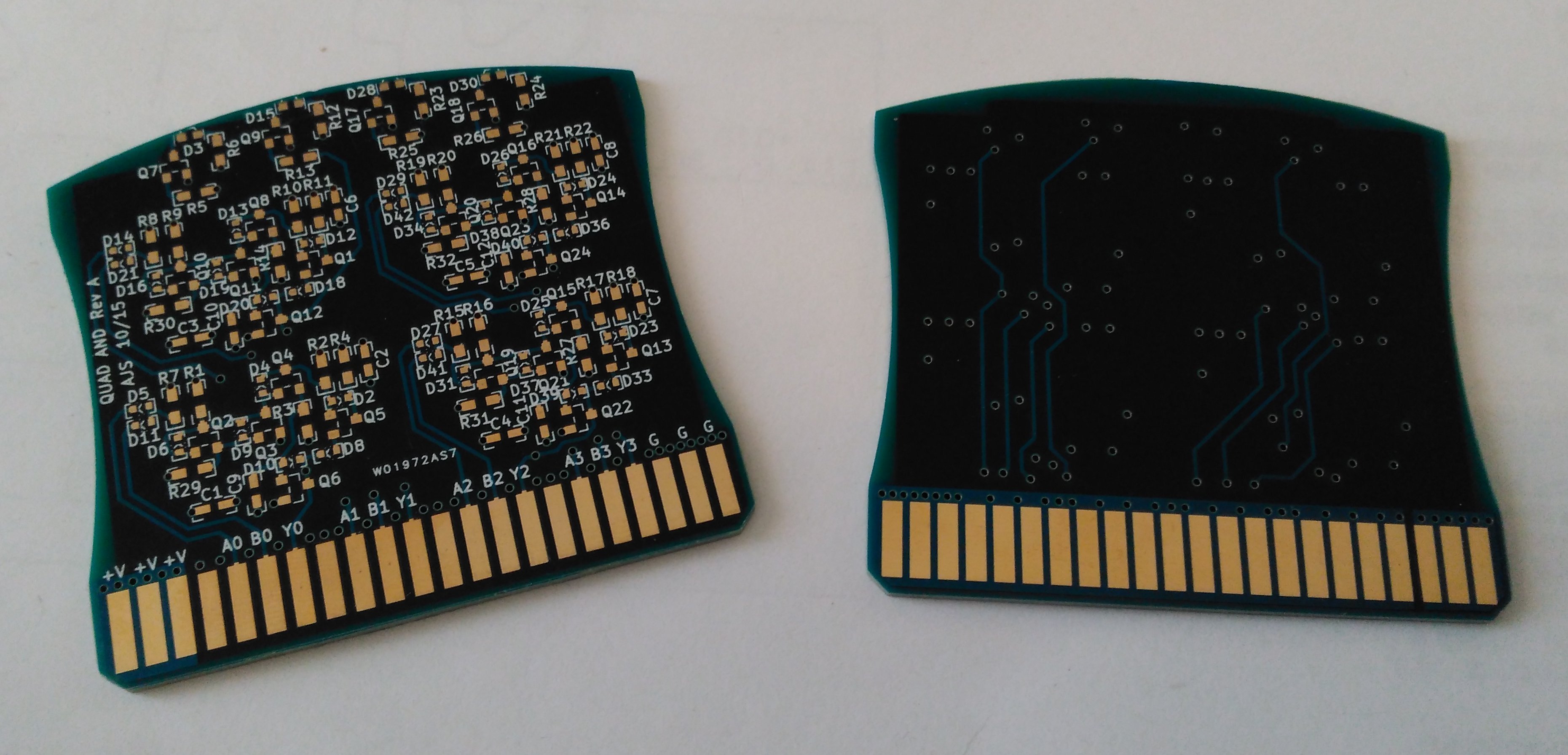

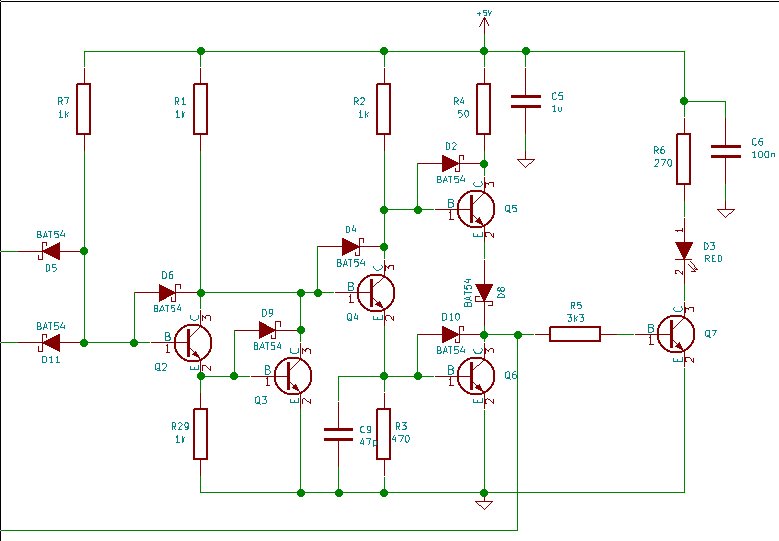

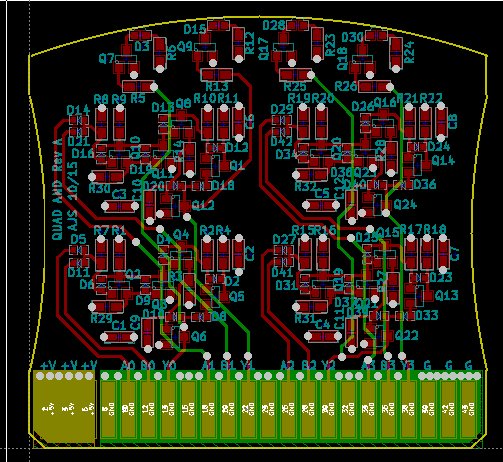

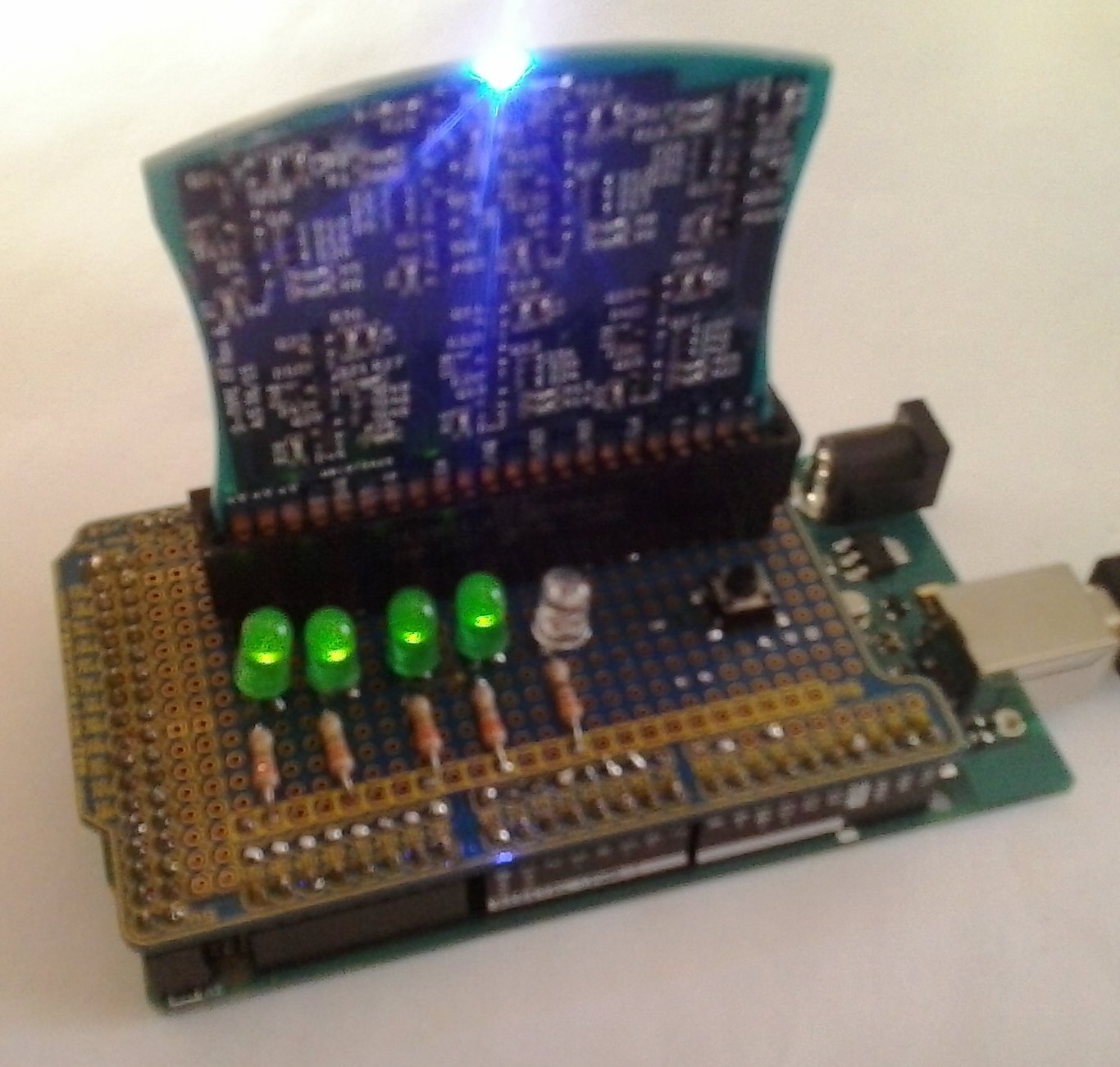

In der Harvard-Architektur müssen die Eigenschaften von Speichervorrichtungen für Anweisungen und Speicher für Daten nicht dieselben sein. Insbesondere können Wortbreite, Taktung, Implementierungstechnologie und Speicheradressstruktur variieren. Auf einigen Systemen können Anweisungen im Nur-Lese-Speicher gespeichert werden, während für die Datenspeicherung normalerweise Lese- und Schreibspeicher erforderlich sind. Einige Systeme benötigen erheblich mehr Speicher für Anweisungen als Speicher für Daten, da Daten normalerweise aus einem externen oder langsameren Speicher geladen werden können. Ein solcher Bedarf erhöht die Bitbreite (Breite) des Befehlsspeicher-Adressbusses im Vergleich zum Datenspeicher-Adressbus.Systemarchitektur: Es wird eine Standard-2-Stack-Maschine mit mehreren Modifikationen verwendet, die die Verwendung der Harvard-Architektur und des optionalen Datenfelds in den Anweisungen ermöglichen.Jetzt hat der Autor bereits ein UND-Modul-Schema entwickelt und die entsprechenden Module bestellt, die neulich eingetroffen sind. Testen von

Es wird eine Standard-2-Stack-Maschine mit mehreren Modifikationen verwendet, die die Verwendung der Harvard-Architektur und des optionalen Datenfelds in den Anweisungen ermöglichen.Jetzt hat der Autor bereits ein UND-Modul-Schema entwickelt und die entsprechenden Module bestellt, die neulich eingetroffen sind. Testen von

Schemata

Schemata

:

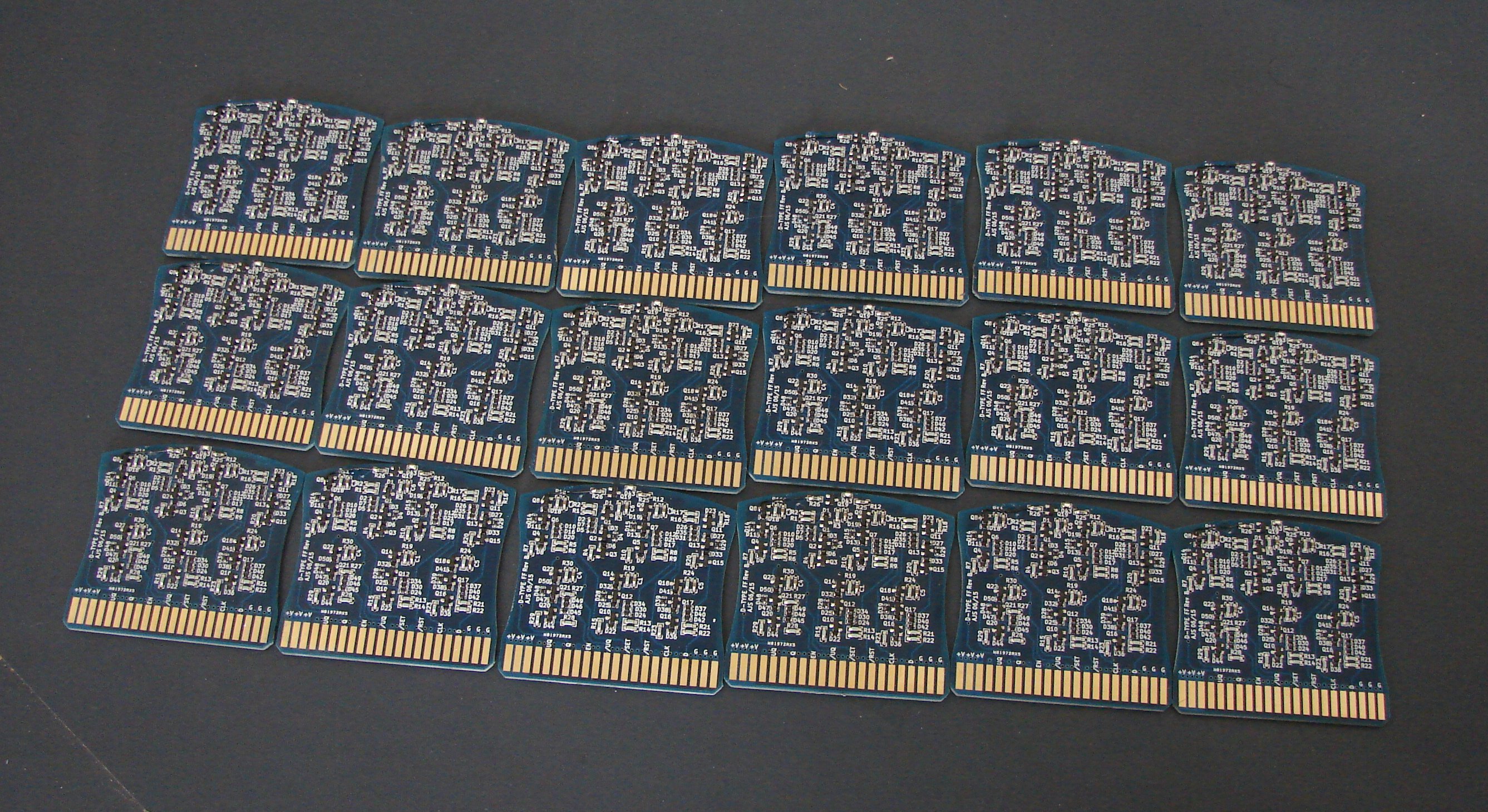

: Andere Komponenten sind ebenfalls bereit, einschließlich Adressdecoder für den Stapelspeicher.

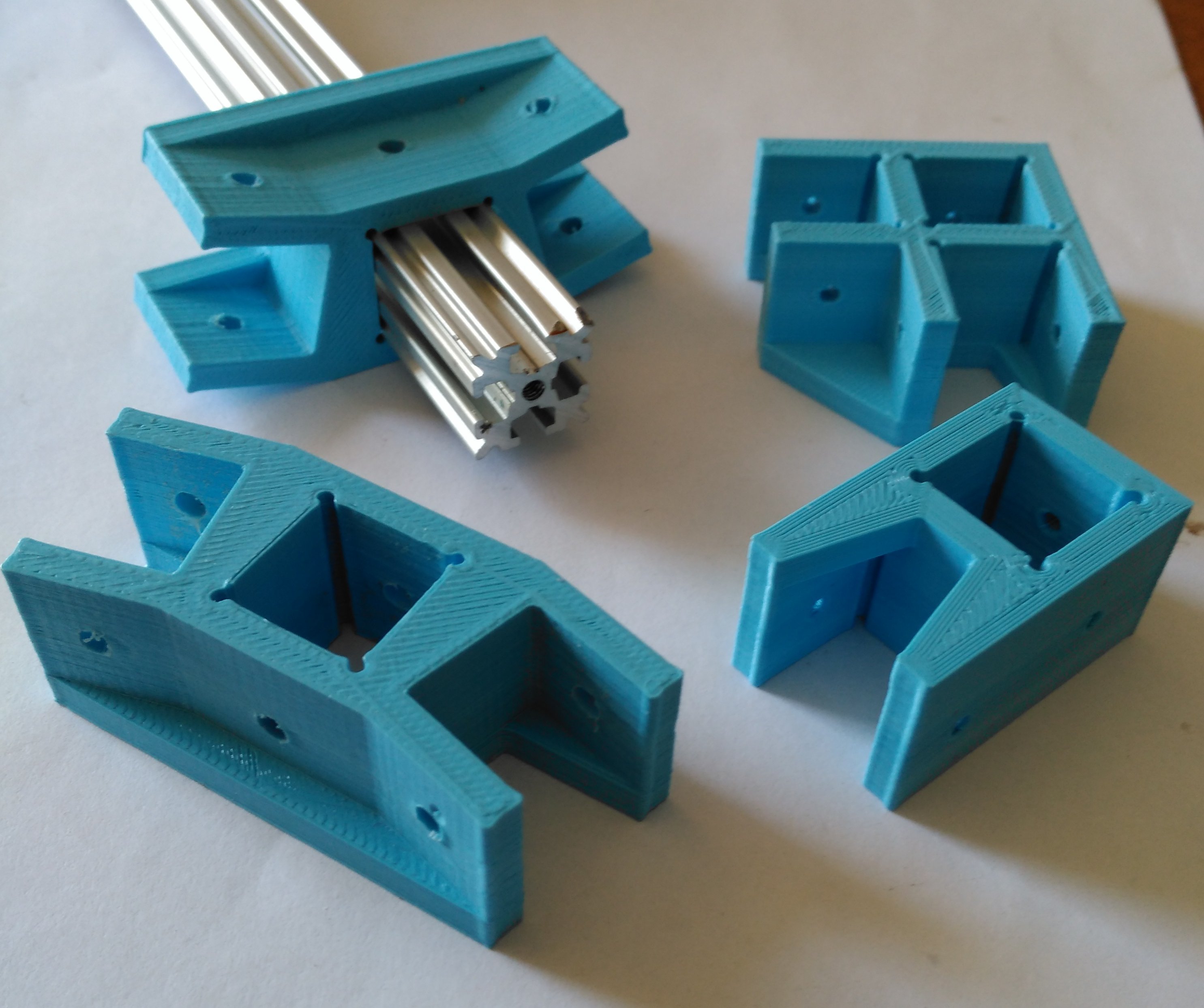

Andere Komponenten sind ebenfalls bereit, einschließlich Adressdecoder für den Stapelspeicher. Unter anderem wird der Autor die Entwicklung auch ein Fall für seine Schöpfung:

Unter anderem wird der Autor die Entwicklung auch ein Fall für seine Schöpfung: Nun ist die Arbeit noch nicht abgeschlossen, so dass Sie die Umsetzung des Projekts überwachen hier .

Nun ist die Arbeit noch nicht abgeschlossen, so dass Sie die Umsetzung des Projekts überwachen hier .Source: https://habr.com/ru/post/de385409/

All Articles