Fotos, Materialien und Wendungen des MIPSfpga-Seminars am MEPhI

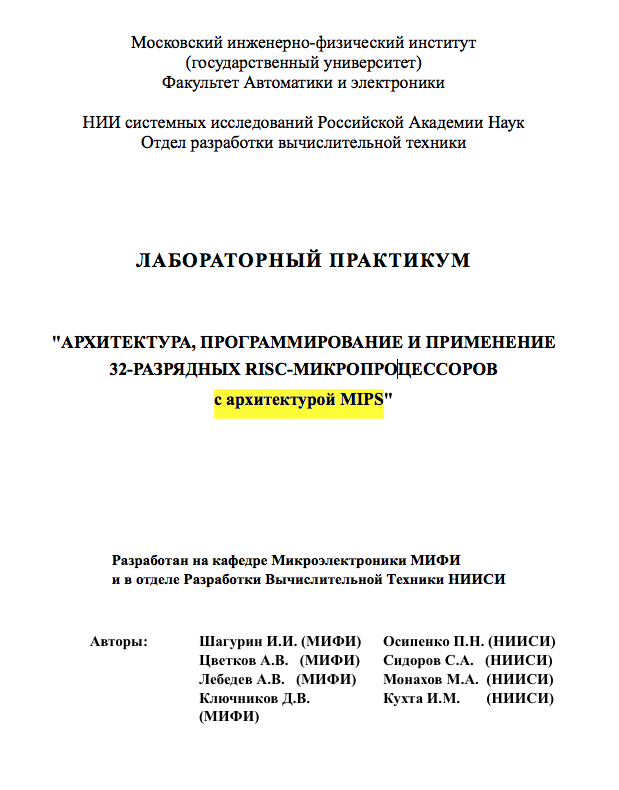

Ende Oktober fand am MEPhI ein Seminar über MIPSfpga statt - eines aus einer Reihe von Seminaren, die von russischen Universitäten zusammen mit Imagination Technologies, Microchip Technology in Zusammenarbeit mit Gamma St. Petersburg, Vertretern der Macro Group von Xilinx in Russland, unter Beteiligung von Rednern von MathWorks und NIISI organisiert wurden. Nachfolgend finden Sie eine Mischung aus Fotografien, Links zu Materialien, Notizen zur Vorbereitung des Seminars und zur mythischen Kultur. Unten ist ein Bild von MEPhI draußen. Das Wort "Nuklear" erinnert daran, dass es im Moskauer Institut für Technische Physik einen Kernreaktor gibt. Daher ist es schwierig, dorthin zu gelangen, insbesondere mit einem amerikanischen Pass. Ich habe einen Pass für zwei Wochen erhalten, und der Rektor hat den Auftrag für das Seminar unterschrieben. Am Eingang steht ein Maschinengewehrschütze mit Kalaschnikow (!) (Ich durfte den Maschinengewehrschützen nicht fotografieren.) Hier bin ich (Yuri Panchul) mit anderen Organisatoren des Seminars - Igor Ivanovich Shagurin und Maxim Gorbunov: Igor Ivanovich Shagurin, Stellvertreter. Leiter der Abteilung für Mikro- und Nanoelektronik - Autor von Büchern und Artikeln über Mikroprozessoren Intel, Motorola und PowerPC, Laborarbeiten zu MIPS . UPD: Klarstellung eines Kameraden von NIIIS:

(Ich durfte den Maschinengewehrschützen nicht fotografieren.) Hier bin ich (Yuri Panchul) mit anderen Organisatoren des Seminars - Igor Ivanovich Shagurin und Maxim Gorbunov: Igor Ivanovich Shagurin, Stellvertreter. Leiter der Abteilung für Mikro- und Nanoelektronik - Autor von Büchern und Artikeln über Mikroprozessoren Intel, Motorola und PowerPC, Laborarbeiten zu MIPS . UPD: Klarstellung eines Kameraden von NIIIS:

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

Interessanterweise vertrat Igor Ivanovich Shagurin die sowjetische Elektronik auf einer Konferenz in San Francisco in den 1970er Jahren, als die UdSSR ein ziemlich isoliertes Land war. Die Teilnehmer dieser VLSI-Konferenz in den 1970er Jahren wurden nach Muir Woods gebracht, dem Gebiet mit den höchsten Mammutbäumen der Welt. Sequoia sempervirens Maxim Gorbunov , ein Forscher von NIISI / SRISA , einem Institut, das an der Entwicklung russischer Mikroprozessoren mit MIPS-Architektur beteiligt ist - COMDIV-32 und KOMMISSION-64. Maxim hat sich auf die Entwicklung der Topologie strahlenresistenter VLSI spezialisiert und war Co-Vorsitzender einer der Sektionen der internationalen RADECS- Konferenz in Moskau:

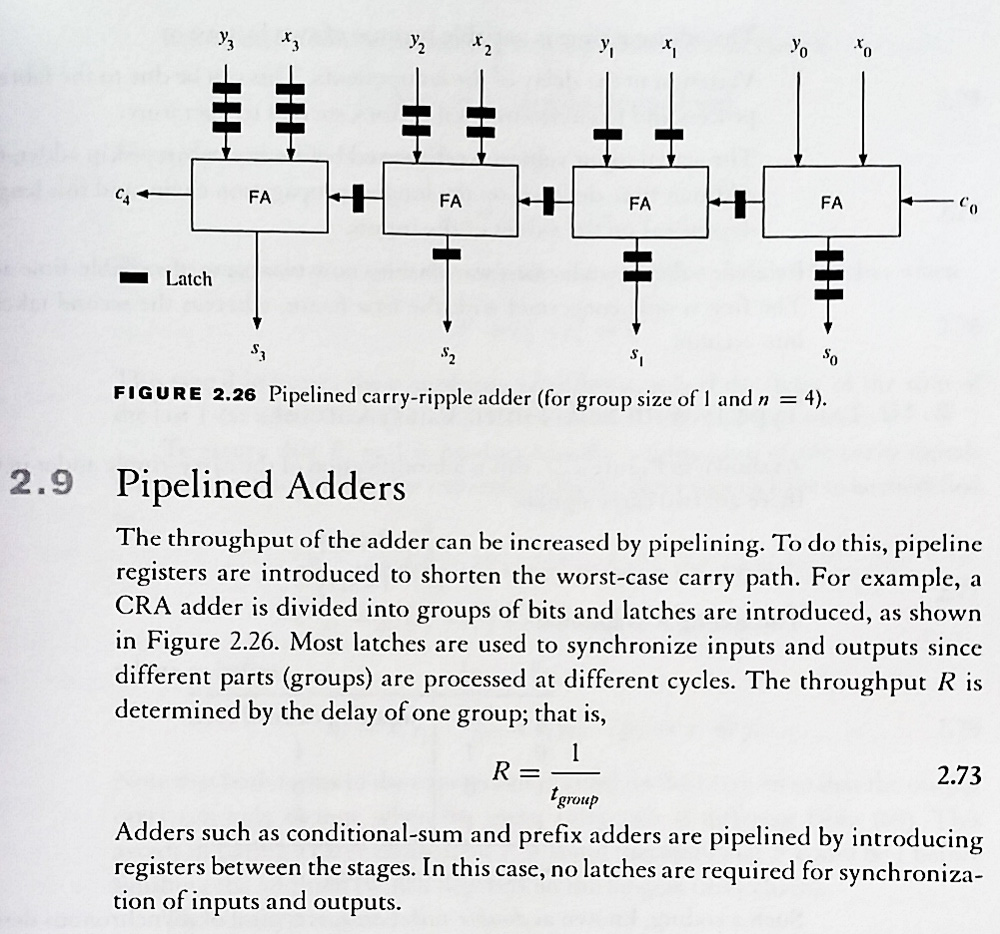

Vor dem MIPSfpga-Seminar bei MEPhI begann mich einer der Ausbilder, Yegor Kuzmin, nach den Rennbedingungen in einem bestimmten Schema für spezialisiertes Computing zu fragen, das als Studentenprojekt entstanden war. Ich bin mir nicht sicher, ob ich es richtig verstanden habe, habe aber zum Ausdruck gebracht, dass in einem richtig organisierten synchronen Design solche Probleme nicht auftreten, und versprochen, als Beispiel ein Foto einer Seite aus dem Buch "Digital Arithmetic" zu senden., der die Organisation des Pipeline-Addierers versteht, der eine kleine Menge kombinatorischer Logik enthält (wie beim Addierer mit sequentieller Übertragung), aber gleichzeitig die Register (D-Trigger) so platziert, dass der Addierer bei jedem Taktzyklus eine neue Additionsoperation mit einer Frequenz starten kann Taktsignal, bestimmt durch die Verzögerung eines Einzelbit-Vollkombinationsaddierers : Digital Arithmetic 1st Edition von Milos D. Ercegovac und Tomás Lang Gleichzeitig habe ich ein paar Seiten über asynchrone Selbstzeitschaltungen fotografiert, die sich ebenfalls auf das Problem beziehen .

Vor dem MIPSfpga-Seminar bei MEPhI begann mich einer der Ausbilder, Yegor Kuzmin, nach den Rennbedingungen in einem bestimmten Schema für spezialisiertes Computing zu fragen, das als Studentenprojekt entstanden war. Ich bin mir nicht sicher, ob ich es richtig verstanden habe, habe aber zum Ausdruck gebracht, dass in einem richtig organisierten synchronen Design solche Probleme nicht auftreten, und versprochen, als Beispiel ein Foto einer Seite aus dem Buch "Digital Arithmetic" zu senden., der die Organisation des Pipeline-Addierers versteht, der eine kleine Menge kombinatorischer Logik enthält (wie beim Addierer mit sequentieller Übertragung), aber gleichzeitig die Register (D-Trigger) so platziert, dass der Addierer bei jedem Taktzyklus eine neue Additionsoperation mit einer Frequenz starten kann Taktsignal, bestimmt durch die Verzögerung eines Einzelbit-Vollkombinationsaddierers : Digital Arithmetic 1st Edition von Milos D. Ercegovac und Tomás Lang Gleichzeitig habe ich ein paar Seiten über asynchrone Selbstzeitschaltungen fotografiert, die sich ebenfalls auf das Problem beziehen . Dann wurde ich Vladimir Dementiev vorgestellt, der zusammen mit Andrei Andrianov, Dmitry Kozlovsky, am MEPhI Laborkurse zur Programmierung von Microchip PIC32MX-Mikrocontrollern durchführt. Ich sagte Vladimir, dass Professor Alex Dean von der University of North Carolina mit Imagination, Microchip und Digilent zusammengearbeitet hat und jetzt einen neuen Kurs zur Programmierung von Microchip PIC32MZ-Mikrocontrollern entwickeltDieser Kurs beinhaltet RTOSs und die neue Verbindung von Mikrocontrollern mit der Cloud. Der PIC32MZ-Mikrocontroller basiert auf dem MIPS microAptiv UP-Mikroprozessorkern, der dem in MIPSfpga verwendeten entspricht. Deshalb begann ich die MEPhI-Genossen zu erregen, um an der Überprüfung und (wenn sie möchten) Beta-Tests dieses Kurses teilzunehmen: Aber zurück zu unserem Seminar. Das Thema des Seminars war MIPSfpga. Was ist das:

Dann wurde ich Vladimir Dementiev vorgestellt, der zusammen mit Andrei Andrianov, Dmitry Kozlovsky, am MEPhI Laborkurse zur Programmierung von Microchip PIC32MX-Mikrocontrollern durchführt. Ich sagte Vladimir, dass Professor Alex Dean von der University of North Carolina mit Imagination, Microchip und Digilent zusammengearbeitet hat und jetzt einen neuen Kurs zur Programmierung von Microchip PIC32MZ-Mikrocontrollern entwickeltDieser Kurs beinhaltet RTOSs und die neue Verbindung von Mikrocontrollern mit der Cloud. Der PIC32MZ-Mikrocontroller basiert auf dem MIPS microAptiv UP-Mikroprozessorkern, der dem in MIPSfpga verwendeten entspricht. Deshalb begann ich die MEPhI-Genossen zu erregen, um an der Überprüfung und (wenn sie möchten) Beta-Tests dieses Kurses teilzunehmen: Aber zurück zu unserem Seminar. Das Thema des Seminars war MIPSfpga. Was ist das:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

Also sprach und sprach ich zuerst über:1. Imagination Technologies und seine MIPS-Geschäftseinheit2. Bildungsprogramme von Imagination Technologies3. Auffrischung des Konzepts des RTL-zu-GDSII-Flusses für diejenigen im Publikum, die nicht über Verilog / VHDL verfügten zur Spezialisierung: Wie IP-Blöcke und Systeme auf einem Chip (SoC) entworfen werden.4. Ich sprach ein wenig über die drei Zeilen der MIPS-Mikroprozessorkerne und ausführlicher über die Reihe der Mikrocontroller-Klassenkerne, auf deren Grundlage (MIPS microAptiv UP) das MIPSfpga5- Paket erstellt wurde . Da eine der Übungen die Demonstration des Caches beinhaltete, sagte ich ein paar Wörter und über Caches in MIPS microAptiv UP

Nach meiner ersten Rede hielt Mikhail Peselnik, ein Sprecher von MathWorks, eine Rede: Mikhail Peselnik implementierte eine Teilmenge von MIPS auf Simulink , die eine Art redaktionellen Preis MATLAB Central Pick der Woche erhielt: Mikhails Beispiel zeigte, dass für einen Studenten die Architektur und Mikroarchitektur von Prozessorkernen auf verschiedene Arten untersucht werden kann - Zumindest bei Verilog und VHDL, zumindest mit Hilfe von C-Modellen, zumindest mit Hilfe von Simulink. Nachdem die Grundlagen der Architektur und der Mikroarchitektur studiert wurden, sollte der Student mit einem industriellen Prozessor experimentieren. Hier tritt MIPSfpga in die Szene ein, mit der:

Nach meiner ersten Rede hielt Mikhail Peselnik, ein Sprecher von MathWorks, eine Rede: Mikhail Peselnik implementierte eine Teilmenge von MIPS auf Simulink , die eine Art redaktionellen Preis MATLAB Central Pick der Woche erhielt: Mikhails Beispiel zeigte, dass für einen Studenten die Architektur und Mikroarchitektur von Prozessorkernen auf verschiedene Arten untersucht werden kann - Zumindest bei Verilog und VHDL, zumindest mit Hilfe von C-Modellen, zumindest mit Hilfe von Simulink. Nachdem die Grundlagen der Architektur und der Mikroarchitektur studiert wurden, sollte der Student mit einem industriellen Prozessor experimentieren. Hier tritt MIPSfpga in die Szene ein, mit der:

- Die Schüler können ihre eigenen Prototypen von Systemen auf einem Chip erstellen und dabei einen von ihnen entworfenen Mikroprozessorkern, Speicher und E / A-Geräte kombinieren

- , . « ».

- , , .

Um jedoch mit SoC-Entwicklungen und dem Kernel experimentieren zu können, müssen sie das Tool / Implementierungs-Tool gut beherrschen. Daher sprach nach Mikhail Mikhail Filippov, Anwendungsingenieur der Macro Group, ein offizieller Vertreter von Xilinx in Russland. Xilinx ist das Unternehmen, das einst FPGAs erfunden hat und bis heute die Nummer 1 unter den schnellsten FPGAs ist.Alexander Filippov machte zwei Berichte:- Neue 7er-FPGAs und MPSoC UltraScale - XILINX-Produkte für leistungsstarke programmierbare Chipsysteme

- XILINX VIVADO Design-Umgebung zum Erstellen von Systemen auf einem Chip

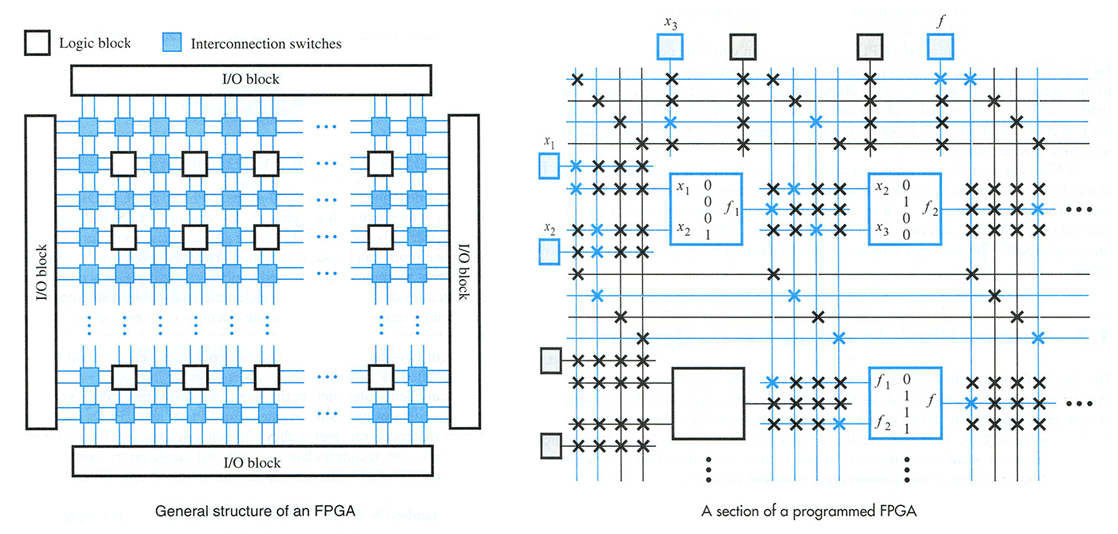

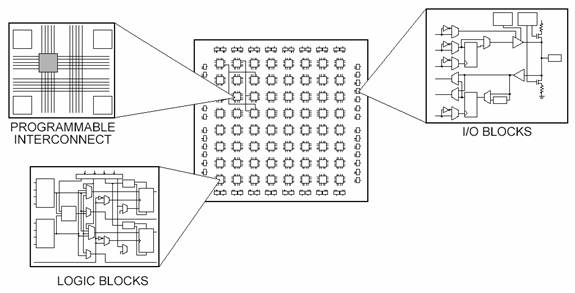

Was FPGA / FPGA habe ich in einem anderen Beitrag über Habr an den Fingern erklärt - Wie man mit der Entwicklung von Eisen mithilfe von FPGAs beginnt - Schritt für Schritt Anleitung . Aber lassen Sie uns diese Informationen noch einmal wiederholen:In der einfachsten Version besteht das FPGA aus einer Matrix homogener Zellen, von denen jede mithilfe von Multiplexern, die mit den Bits des Konfigurationsspeichers verbunden sind, in ihre Funktion geändert werden kann. Eine Zelle kann ein UND-Gatter mit vier Eingängen und einem Ausgang werden, ein anderes - ein Einzelbitregister usw. Wir laden eine Folge von Bits aus dem Speicher in den Konfigurationsspeicher - und die gegebene elektronische Schaltung wird im FPGA gebildet, das ein Prozessor, ein Anzeigecontroller usw. sein kann.FPGAs / FPGAs sind keine Prozessoren. Durch „Programmieren“ von FPGAs (Füllen des Konfigurationsspeichers von FPGAs) erstellen Sie eine elektronische Schaltung (Hardware), während Sie beim Programmieren eines Prozessors (feste Hardware) eine Kette von sequentiellen Programmanweisungen hineinschieben (Software).Unten sehen Sie ein Diagramm der einfachsten FPGA-Einheit, die eine Nachschlagetabelle (LUT) und ein Flip-Flop enthält. In diesem Schema werden zwar Multiplexer, die die Funktion der Zelle ändern, und Verbindungen zum Konfigurationsspeicher nicht angezeigt.

Was FPGA / FPGA habe ich in einem anderen Beitrag über Habr an den Fingern erklärt - Wie man mit der Entwicklung von Eisen mithilfe von FPGAs beginnt - Schritt für Schritt Anleitung . Aber lassen Sie uns diese Informationen noch einmal wiederholen:In der einfachsten Version besteht das FPGA aus einer Matrix homogener Zellen, von denen jede mithilfe von Multiplexern, die mit den Bits des Konfigurationsspeichers verbunden sind, in ihre Funktion geändert werden kann. Eine Zelle kann ein UND-Gatter mit vier Eingängen und einem Ausgang werden, ein anderes - ein Einzelbitregister usw. Wir laden eine Folge von Bits aus dem Speicher in den Konfigurationsspeicher - und die gegebene elektronische Schaltung wird im FPGA gebildet, das ein Prozessor, ein Anzeigecontroller usw. sein kann.FPGAs / FPGAs sind keine Prozessoren. Durch „Programmieren“ von FPGAs (Füllen des Konfigurationsspeichers von FPGAs) erstellen Sie eine elektronische Schaltung (Hardware), während Sie beim Programmieren eines Prozessors (feste Hardware) eine Kette von sequentiellen Programmanweisungen hineinschieben (Software).Unten sehen Sie ein Diagramm der einfachsten FPGA-Einheit, die eine Nachschlagetabelle (LUT) und ein Flip-Flop enthält. In diesem Schema werden zwar Multiplexer, die die Funktion der Zelle ändern, und Verbindungen zum Konfigurationsspeicher nicht angezeigt. Diagramme zur Veranschaulichung der Struktur des FPGA:

Diagramme zur Veranschaulichung der Struktur des FPGA: Und noch eines:

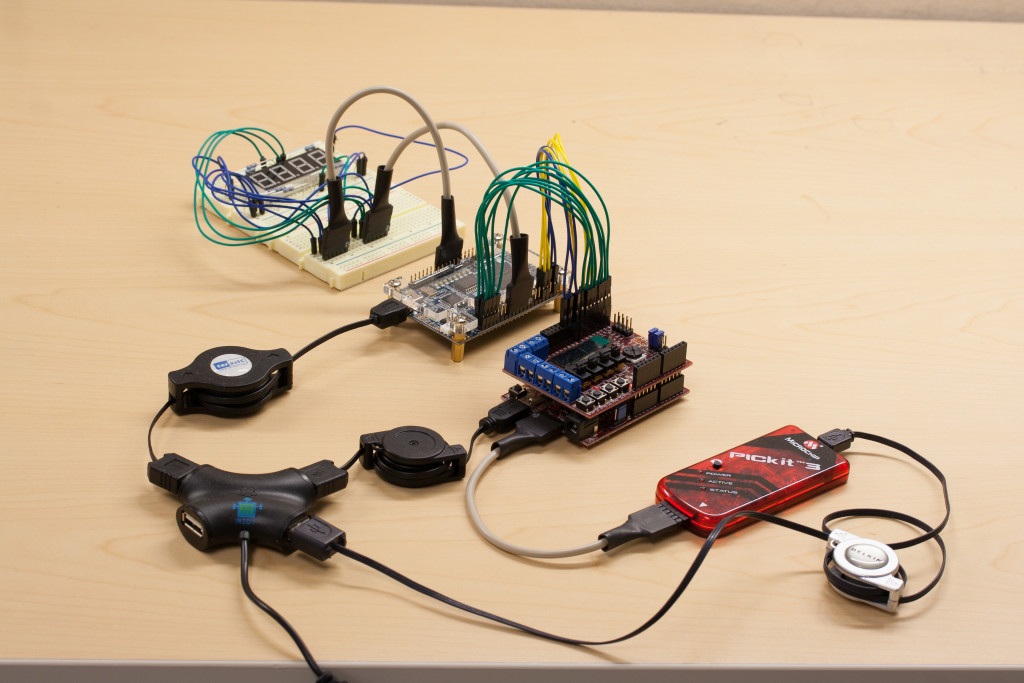

Und noch eines: Nach dem Mittagessen im Speisesaal des Moskauer Instituts für Technische Physik begannen wir mit dem praktischen Teil. Als Imagination Technologies und Xilinx ein solches Seminar in Los Angeles abhielten, nutzten sie es zunächstFolien vorbereitet von den Professoren David und Sarah Harris aus Südkalifornien . Wie es ursprünglich aussah, können Sie auf dem Video sehen:Alle 8 Videos aus demWorkshop in Los Angeles Für Seminare in Russland mussten Harris 'Kern- und Laborbindungen erheblich modifiziert werden. Änderungen finden Sie unter https://github.com/MIPSfpga/mipsfpga-plus . Zu den Unterschieden gehören:1. Alles ist nach billigen Motherboards von Altera sortiert, die in Russland ohne Export-Import-Traktor erhältlich sind.2. Das Programm wurde ohne Verwendung von BusBlaster einfach über UART3 in ein synthetisiertes System geladen . Der Lichtsensor als Peripheriegerät anstelle eines LCD-Displays.4. Umschaltbar Ultra-Niederfrequenz-Taktsignal, mit dem Labore den Betrieb von Prozessor-Interna visualisieren können5. Ein einfaches Labor zur Visualisierung von Cache-Fehlern wurde hinzugefügt+ jede Kleinigkeit und Kosmetik - ein kompakterer Bootloader / Bootloader, die Möglichkeit, nicht zwischenspeicherbare Transaktionen auf den Speicher zu beschränken usw.Weitere Details:1. Portierung unter AlteraZunächst zeigten Harris-Folien alles für Xilinx, und in letzter Zeit ist der Versand von Boards von Xilinx-FPGAs nach Russland zu einem ziemlich komplizierten bürokratischen Verfahren geworden, das 3-4 Monate dauert. Dasselbe geschah mit der Lizenzierung der Synthesesoftware und des Place-and-Route-Xilinx Vivado, auch mit kostenlosen Lizenzen. Einige russische Universitäten hatten keine Xilinx-Boards oder Vivado-Lizenzen. andere hatten nur die alte Lizenz für den Vorgänger von Vivado - die 2013 ISE-Software, die keine FPGAs auf Boards unterstützte, die ich in Russland transportierte.Kurz gesagt, für Seminare in Russland hatten Genossen und ich in Kalifornien MIPSfpga auf ein paar billige Boards portiert, die in Russland vom Xilinx-Rivalen Altera erhältlich sind (dieses Unternehmen fusioniert jetzt mit Intel). Die Alter-Boards wurden von der Zelenograd-Firma SPC Elvis für die Bedürfnisse des Workshops gespendet . Das Hauptboard bei MEPhI, MIPT und SSAU war das Terasic DE0-CV basierend auf Altera Cyclone V: Ein anderes Board war das Terasic DE0-Nano - ein sehr kompakter Schal, der für Projekte wie fliegende Roboter geeignet ist, aber nur wenige Peripheriegeräte an Bord hat: Terasic DE0-Nachteil Nano ist eine kleine Anzahl von Peripheriegeräten auf der Karte selbst, aber es ist auch ein Vorteil, da DE0-Nano als Designer mit anderen Karten verbunden und in verschiedene Geräte eingebaut werden kann:

Nach dem Mittagessen im Speisesaal des Moskauer Instituts für Technische Physik begannen wir mit dem praktischen Teil. Als Imagination Technologies und Xilinx ein solches Seminar in Los Angeles abhielten, nutzten sie es zunächstFolien vorbereitet von den Professoren David und Sarah Harris aus Südkalifornien . Wie es ursprünglich aussah, können Sie auf dem Video sehen:Alle 8 Videos aus demWorkshop in Los Angeles Für Seminare in Russland mussten Harris 'Kern- und Laborbindungen erheblich modifiziert werden. Änderungen finden Sie unter https://github.com/MIPSfpga/mipsfpga-plus . Zu den Unterschieden gehören:1. Alles ist nach billigen Motherboards von Altera sortiert, die in Russland ohne Export-Import-Traktor erhältlich sind.2. Das Programm wurde ohne Verwendung von BusBlaster einfach über UART3 in ein synthetisiertes System geladen . Der Lichtsensor als Peripheriegerät anstelle eines LCD-Displays.4. Umschaltbar Ultra-Niederfrequenz-Taktsignal, mit dem Labore den Betrieb von Prozessor-Interna visualisieren können5. Ein einfaches Labor zur Visualisierung von Cache-Fehlern wurde hinzugefügt+ jede Kleinigkeit und Kosmetik - ein kompakterer Bootloader / Bootloader, die Möglichkeit, nicht zwischenspeicherbare Transaktionen auf den Speicher zu beschränken usw.Weitere Details:1. Portierung unter AlteraZunächst zeigten Harris-Folien alles für Xilinx, und in letzter Zeit ist der Versand von Boards von Xilinx-FPGAs nach Russland zu einem ziemlich komplizierten bürokratischen Verfahren geworden, das 3-4 Monate dauert. Dasselbe geschah mit der Lizenzierung der Synthesesoftware und des Place-and-Route-Xilinx Vivado, auch mit kostenlosen Lizenzen. Einige russische Universitäten hatten keine Xilinx-Boards oder Vivado-Lizenzen. andere hatten nur die alte Lizenz für den Vorgänger von Vivado - die 2013 ISE-Software, die keine FPGAs auf Boards unterstützte, die ich in Russland transportierte.Kurz gesagt, für Seminare in Russland hatten Genossen und ich in Kalifornien MIPSfpga auf ein paar billige Boards portiert, die in Russland vom Xilinx-Rivalen Altera erhältlich sind (dieses Unternehmen fusioniert jetzt mit Intel). Die Alter-Boards wurden von der Zelenograd-Firma SPC Elvis für die Bedürfnisse des Workshops gespendet . Das Hauptboard bei MEPhI, MIPT und SSAU war das Terasic DE0-CV basierend auf Altera Cyclone V: Ein anderes Board war das Terasic DE0-Nano - ein sehr kompakter Schal, der für Projekte wie fliegende Roboter geeignet ist, aber nur wenige Peripheriegeräte an Bord hat: Terasic DE0-Nachteil Nano ist eine kleine Anzahl von Peripheriegeräten auf der Karte selbst, aber es ist auch ein Vorteil, da DE0-Nano als Designer mit anderen Karten verbunden und in verschiedene Geräte eingebaut werden kann:

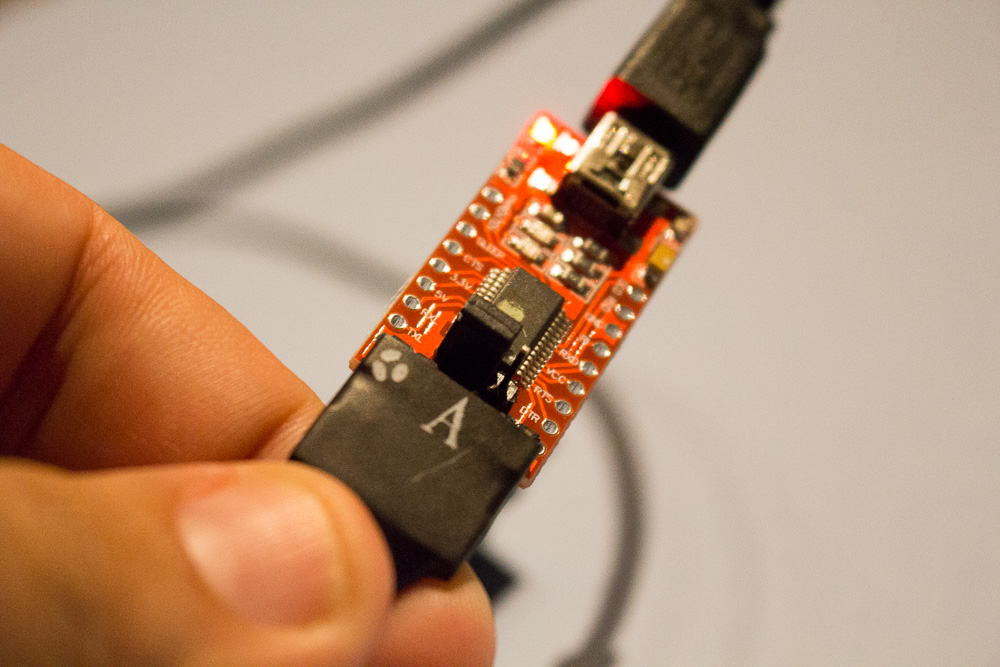

2. Download über UART Daszweite Folienproblem von Harris war die Verwendung des Bus Blaster-Debug-Adapters und der dafür verwendeten Software namens OpenOCD . Grundsätzlich ist BusBlaster / OpenOCD eine ziemlich gute Lösung dieser Art. Es ermöglicht nicht nur das Laden von Programmen in das im FPGA synthetisierte System, sondern auch das Remote-Debuggen über die EJTAG-Schnittstelle, ein Add-In einer höheren Ebene über die JTAG-Schnittstelle. Gleichzeitig kostet BusBlaster nur 43 US-Dollar, was viel billiger ist als industrielle Debugging-EJTAG-Adapter.Leider ist die BusBlaster / OpenOCD-Kombination ziemlich grob und ich befürchtete, dass sie bei einer unerwarteten Computerkonfiguration in Russland nicht funktionieren würde (ich hatte Recht - sie funktionierte bei MIPT und SSAU nicht). Neben,Auf einer Site, die eine BusBlaster / OpenOCD-Kombination für MIPS verkauft , gehen manchmal die Boards aus.Aus diesem und anderen Gründen suchte ich nach anderen Möglichkeiten, um Software auf das System herunterzuladen (im FPGA müssen Sie die Konfiguration / Hardware und Software für den Prozessor separat laden (in einem synthetisierten System mit einem Prozessor)). Der anonyme Internet-Troll Alexey versuchte lange Zeit, mich schwach zu machen, damit ich den EJTAG-Bootloader über den Altera USB Blaster implementieren konnte. Da ich jedoch kein EJTAG-Experte war, entschied ich mich für eine einfache Lösung, die seit der Sowjetzeit funktionierte - das Programm über die serielle Schnittstelle / UART zu laden. Während der Sowjetzeit gab es zwar einen RS-232C-Anschluss, und in den 1990er Jahren erschienen Chips von FTDI, die es ermöglichten, alles über ein an einen PC angeschlossenes USB-Kabel zu erledigen. Verschiedene Varianten eines solchen Adapters können in Moskau für 5 USD und in China für weniger als 2 USD über das Internet gekauft werden:

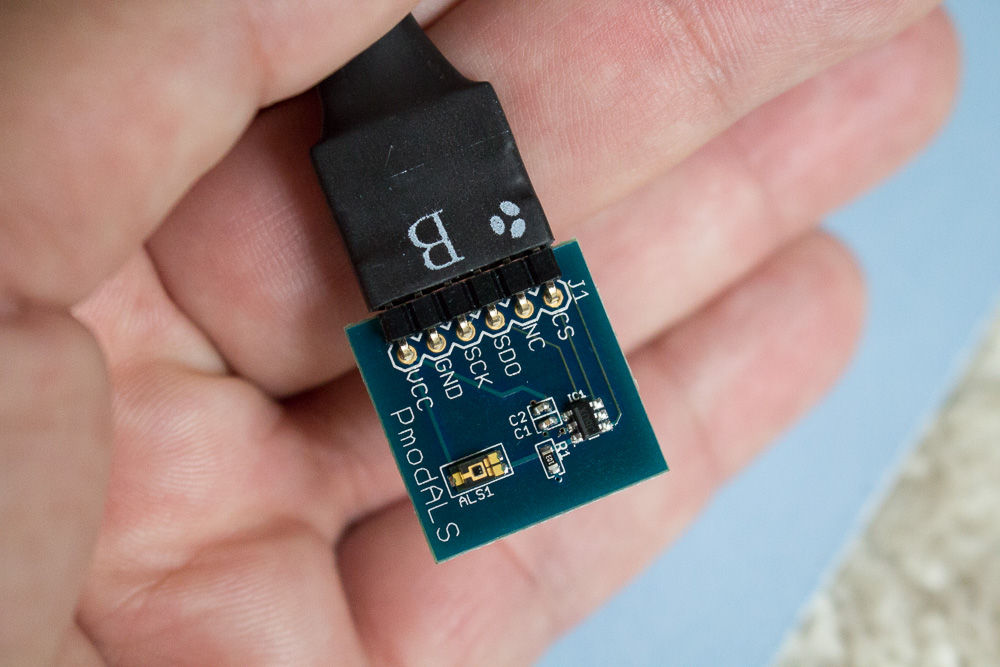

2. Download über UART Daszweite Folienproblem von Harris war die Verwendung des Bus Blaster-Debug-Adapters und der dafür verwendeten Software namens OpenOCD . Grundsätzlich ist BusBlaster / OpenOCD eine ziemlich gute Lösung dieser Art. Es ermöglicht nicht nur das Laden von Programmen in das im FPGA synthetisierte System, sondern auch das Remote-Debuggen über die EJTAG-Schnittstelle, ein Add-In einer höheren Ebene über die JTAG-Schnittstelle. Gleichzeitig kostet BusBlaster nur 43 US-Dollar, was viel billiger ist als industrielle Debugging-EJTAG-Adapter.Leider ist die BusBlaster / OpenOCD-Kombination ziemlich grob und ich befürchtete, dass sie bei einer unerwarteten Computerkonfiguration in Russland nicht funktionieren würde (ich hatte Recht - sie funktionierte bei MIPT und SSAU nicht). Neben,Auf einer Site, die eine BusBlaster / OpenOCD-Kombination für MIPS verkauft , gehen manchmal die Boards aus.Aus diesem und anderen Gründen suchte ich nach anderen Möglichkeiten, um Software auf das System herunterzuladen (im FPGA müssen Sie die Konfiguration / Hardware und Software für den Prozessor separat laden (in einem synthetisierten System mit einem Prozessor)). Der anonyme Internet-Troll Alexey versuchte lange Zeit, mich schwach zu machen, damit ich den EJTAG-Bootloader über den Altera USB Blaster implementieren konnte. Da ich jedoch kein EJTAG-Experte war, entschied ich mich für eine einfache Lösung, die seit der Sowjetzeit funktionierte - das Programm über die serielle Schnittstelle / UART zu laden. Während der Sowjetzeit gab es zwar einen RS-232C-Anschluss, und in den 1990er Jahren erschienen Chips von FTDI, die es ermöglichten, alles über ein an einen PC angeschlossenes USB-Kabel zu erledigen. Verschiedene Varianten eines solchen Adapters können in Moskau für 5 USD und in China für weniger als 2 USD über das Internet gekauft werden: Ich werde sofort feststellen, dass Sie Programme auf verschiedene Arten in synthetisierten SoC laden können. In einem dieser traditionelleren Systeme verfügt das System über ein kleines festes Programm im Speicher (Bootloader), das nach dem Zurücksetzen des Systems startet und ein größeres Programm über die UART / serielle Schnittstelle lädt. Diese Methode wurde von Anton Pavlov aus NIIIS verwendet, der es in Seminaren an der Staatlichen Universität Moskau und Moskauer Engineering Physics Institute gezeigt, und auch eine Notiz für ihn auf geektimes schrieb „MIPSfpga: außerhalb des Kanons . “Ich habe das Laden auf eine alternative Weise durchgeführt, bei der der Speicher mit einer Zustandsmaschine gefüllt ist, die vollständig in der Hardware implementiert ist. Das Gerät akzeptiert eine Textdatei im Motorola S-Record-Format von einem PC über UART, analysiert es (alles in der Hardware) und füllt den Speicher mit Daten, während sich der Prozessor im Reset-Zustand befindet. Dann wacht der Prozessor auf und beginnt, das Programm aus dem Systemspeicher zu lesen. Auf der PC-Seite muss lediglich die ausführbare ELF-Datei in das Motorola S-Record-Format konvertiert und mit dem Windows-Shell-Befehl „type“ an den virtuellen COM-Port gesendet werden.3. Lichtsensor als Peripheriegerät anstelle eines LCD-DisplaysIn den ursprünglichen Harris-Labors verwendeten sie eine Sieben-Segment-Anzeige und ein SPI-LCD-Display als Beispiele für Peripheriegeräte. Ein Beispiel mit einer Sieben-Segment-Anzeige ist langweilig - jeder Schüler versteht, dass man mit sieben Lichtern blinken kann, wenn man weiß, wie man mit einem Licht blinkt. Das SPI-Beispiel ist etwas besser, insbesondere wenn es sich um Anfänger handelt. Warum benötigen wir jedoch eine zweite Anzeige, wenn bereits ein Sieben-Segment-Indikator vorhanden ist? Kurz gesagt, bevor ich nach Russland gereist bin, habe ich 20 Lichtsensoren gekauft, auch mit einer SPI-Schnittstelle, und sie anstelle von Displays verwendet: Gleichzeitig ist die Schnittstelle dazu sehr einfach - hier ist das Schnittstellenmodul, das ich geschrieben habe (Hinweis: Dieser Code enthält nicht alle Modifikationen des Systems, mit denen es gekoppelt werden soll AHB-Lite-Bus, damit die Software den Wert sieht):

Ich werde sofort feststellen, dass Sie Programme auf verschiedene Arten in synthetisierten SoC laden können. In einem dieser traditionelleren Systeme verfügt das System über ein kleines festes Programm im Speicher (Bootloader), das nach dem Zurücksetzen des Systems startet und ein größeres Programm über die UART / serielle Schnittstelle lädt. Diese Methode wurde von Anton Pavlov aus NIIIS verwendet, der es in Seminaren an der Staatlichen Universität Moskau und Moskauer Engineering Physics Institute gezeigt, und auch eine Notiz für ihn auf geektimes schrieb „MIPSfpga: außerhalb des Kanons . “Ich habe das Laden auf eine alternative Weise durchgeführt, bei der der Speicher mit einer Zustandsmaschine gefüllt ist, die vollständig in der Hardware implementiert ist. Das Gerät akzeptiert eine Textdatei im Motorola S-Record-Format von einem PC über UART, analysiert es (alles in der Hardware) und füllt den Speicher mit Daten, während sich der Prozessor im Reset-Zustand befindet. Dann wacht der Prozessor auf und beginnt, das Programm aus dem Systemspeicher zu lesen. Auf der PC-Seite muss lediglich die ausführbare ELF-Datei in das Motorola S-Record-Format konvertiert und mit dem Windows-Shell-Befehl „type“ an den virtuellen COM-Port gesendet werden.3. Lichtsensor als Peripheriegerät anstelle eines LCD-DisplaysIn den ursprünglichen Harris-Labors verwendeten sie eine Sieben-Segment-Anzeige und ein SPI-LCD-Display als Beispiele für Peripheriegeräte. Ein Beispiel mit einer Sieben-Segment-Anzeige ist langweilig - jeder Schüler versteht, dass man mit sieben Lichtern blinken kann, wenn man weiß, wie man mit einem Licht blinkt. Das SPI-Beispiel ist etwas besser, insbesondere wenn es sich um Anfänger handelt. Warum benötigen wir jedoch eine zweite Anzeige, wenn bereits ein Sieben-Segment-Indikator vorhanden ist? Kurz gesagt, bevor ich nach Russland gereist bin, habe ich 20 Lichtsensoren gekauft, auch mit einer SPI-Schnittstelle, und sie anstelle von Displays verwendet: Gleichzeitig ist die Schnittstelle dazu sehr einfach - hier ist das Schnittstellenmodul, das ich geschrieben habe (Hinweis: Dieser Code enthält nicht alle Modifikationen des Systems, mit denen es gekoppelt werden soll AHB-Lite-Bus, damit die Software den Wert sieht):

4.Uhr auf Ultra-Low-Frequenz umgestellt Als MIPSfpga erschien und russische Universitätsprofessoren begannen, es zu studieren, beschwerten sich einige von ihnen, dass das Paket in seiner ursprünglichen Form für fortgeschrittene Studenten nicht sehr interessant sei, da die von David und Sarah Harris vorbereiteten Labore einen Prozessor verwenden wie eine „Black Box“, die nur Geräte daran anschließt. Mit anderen Worten, Harris ignorierte völlig, dass der Prozessor im Quellcode angegeben ist, und daher ist es möglich, Labore damit zu implementieren, die die Ausgabe von Verbindungen aus beliebigen Prozessorregistern (nicht nur Registern, die für den Programmierer sichtbar sind, sondern im Allgemeinen von beliebigen D-Triggern) ermöglichen, um eine Verbindung herzustellen Zum Beispiel an LEDs und beobachten Sie, was mit dem Prozessor passiert, wenn Sie bestimmte Programme ausführen.Wie Sie verstehen, ist es erforderlich, dass der Prozessor mit einer sehr niedrigen Taktfrequenz arbeitet, beispielsweise einem Takt pro Sekunde, um solche Beobachtungen „live“ zu machen. Wie kann man das machen? Der in ASIC auf 28-nm-Technologie implementierte MIPS microAptiv UP-Kern kann bei Frequenzen über 500 MHz und auf 65-nm-Technologie über 300 MHz betrieben werden. Bei der Implementierung auf FPGAs sind die Frequenzen viel niedriger, aber immer noch hoch - 50-60 MHz. Die Frequenzen der Taktsignalgeneratoren auf den Karten betragen 50-100 MHz, mit der Möglichkeit, die Frequenz unter Verwendung einer Phasenregelschleife (PLL) / Phasenregelschleife (PLL) zu erhöhen oder zu verringern .Leider können Sie mit PLL die Frequenz auf ~ 100 kHz reduzieren, aber Sie müssen die Frequenz auf andere Weise auf 1 Hz reduzieren. Zuerst habe ich versucht, dies mit einem Block von Altera namens zu tunALTCLKCTRL , aber aus irgendeinem Grund hat es nicht funktioniert. Dann habe ich versucht, das Taktsignal mit einem Zähler zu teilen, aber (ich wusste es bereits) diese Lösung selbst funktioniert nicht, weil der Synthesizer nicht versteht, dass das Ausgangssignal ein Taktsignal ist, und beginnt, es falsch zu teilen, wodurch der Prozessor nicht funktioniert. Ich habe mich mit mehreren Freunden beraten und wir haben begonnen, das Alter-Makro „global“ (und sein Äquivalent zu Xilinx BUFG) zu verwenden. 5. Ein einfaches Cache-Miss-Visualisierungslabor wurde hinzugefügt

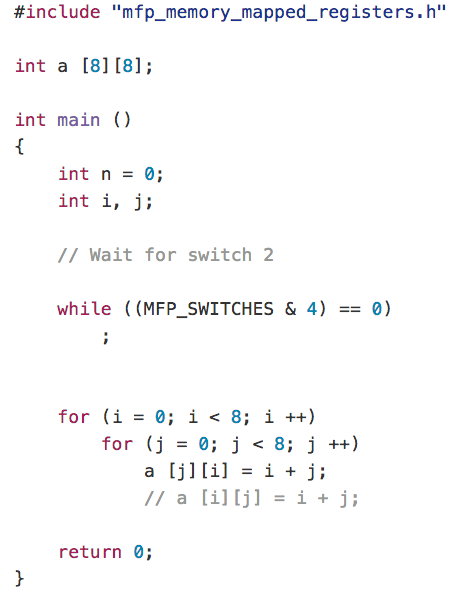

4.Uhr auf Ultra-Low-Frequenz umgestellt Als MIPSfpga erschien und russische Universitätsprofessoren begannen, es zu studieren, beschwerten sich einige von ihnen, dass das Paket in seiner ursprünglichen Form für fortgeschrittene Studenten nicht sehr interessant sei, da die von David und Sarah Harris vorbereiteten Labore einen Prozessor verwenden wie eine „Black Box“, die nur Geräte daran anschließt. Mit anderen Worten, Harris ignorierte völlig, dass der Prozessor im Quellcode angegeben ist, und daher ist es möglich, Labore damit zu implementieren, die die Ausgabe von Verbindungen aus beliebigen Prozessorregistern (nicht nur Registern, die für den Programmierer sichtbar sind, sondern im Allgemeinen von beliebigen D-Triggern) ermöglichen, um eine Verbindung herzustellen Zum Beispiel an LEDs und beobachten Sie, was mit dem Prozessor passiert, wenn Sie bestimmte Programme ausführen.Wie Sie verstehen, ist es erforderlich, dass der Prozessor mit einer sehr niedrigen Taktfrequenz arbeitet, beispielsweise einem Takt pro Sekunde, um solche Beobachtungen „live“ zu machen. Wie kann man das machen? Der in ASIC auf 28-nm-Technologie implementierte MIPS microAptiv UP-Kern kann bei Frequenzen über 500 MHz und auf 65-nm-Technologie über 300 MHz betrieben werden. Bei der Implementierung auf FPGAs sind die Frequenzen viel niedriger, aber immer noch hoch - 50-60 MHz. Die Frequenzen der Taktsignalgeneratoren auf den Karten betragen 50-100 MHz, mit der Möglichkeit, die Frequenz unter Verwendung einer Phasenregelschleife (PLL) / Phasenregelschleife (PLL) zu erhöhen oder zu verringern .Leider können Sie mit PLL die Frequenz auf ~ 100 kHz reduzieren, aber Sie müssen die Frequenz auf andere Weise auf 1 Hz reduzieren. Zuerst habe ich versucht, dies mit einem Block von Altera namens zu tunALTCLKCTRL , aber aus irgendeinem Grund hat es nicht funktioniert. Dann habe ich versucht, das Taktsignal mit einem Zähler zu teilen, aber (ich wusste es bereits) diese Lösung selbst funktioniert nicht, weil der Synthesizer nicht versteht, dass das Ausgangssignal ein Taktsignal ist, und beginnt, es falsch zu teilen, wodurch der Prozessor nicht funktioniert. Ich habe mich mit mehreren Freunden beraten und wir haben begonnen, das Alter-Makro „global“ (und sein Äquivalent zu Xilinx BUFG) zu verwenden. 5. Ein einfaches Cache-Miss-Visualisierungslabor wurde hinzugefügt Jetzt können Sie interessante Experimente durchführen - zum Beispiel, um die LED während eines Cache-Fehlers blinken zu lassen und dann die Treffer und Fehler des Caches beim Füllen eines zweidimensionalen Arrays in Echtzeit zu beobachten. Wenn Sie das Array Zeile für Zeile füllen, unterscheiden sich die Blinkzeichen von denen beim Ausfüllen der Spalten: Es sollte beachtet werden, dass nicht alles reibungslos verlief:

Jetzt können Sie interessante Experimente durchführen - zum Beispiel, um die LED während eines Cache-Fehlers blinken zu lassen und dann die Treffer und Fehler des Caches beim Füllen eines zweidimensionalen Arrays in Echtzeit zu beobachten. Wenn Sie das Array Zeile für Zeile füllen, unterscheiden sich die Blinkzeichen von denen beim Ausfüllen der Spalten: Es sollte beachtet werden, dass nicht alles reibungslos verlief: 1. Der GPIO in DE0-Nano unterscheidet sich vom GPIO in DE0-CV- und Xilinx-Karten. Insbesondere konnte ich aus irgendeinem Grund nicht den gesamten GPIO-Port als einen Inout deklarieren und dann seine einzelnen Bits entweder als Eingang oder als Ausgang verwenden. Obwohl auf DE0-CV dies gut geht. Ich hatte keine Zeit, die verschiedenen GPIO-Ausgänge auf verschiedene logische (auf Verilog) Signale aufzuteilen, also habe ich das Labor mit dem Lichtsensor auf DE0-Nano nicht sortiert. Aus dem gleichen Grund habe ich die Schnittstelle mit dem Bus Blaster nicht in den DE0-CV exportiert.2. Schlimmer noch, das Herunterladen über UART für DE0-Nano funktionierte bei MEPhI nicht, obwohl es zuvor an der Moskauer Staatsuniversität und auf meinem Laptop funktionierte. Der Grund ist immer noch nicht 100% klar:2.1. Möglicherweise gab es ein Problem mit der Inkompatibilität der Windows-Version (7 mit dem Patch) und des für DE0-Nano verwendeten USB-zu-UART-Kabels. Das Kabel war ein billiger chinesischer Kabelklon, der auf dem PL2303TA-Chipsatz basierte, obwohl ich es vor dem Seminar nicht ausprobiert habe. Es ist bekannt, dass die vorherige Version solcher Kabel, die auf Chipsätzen mit PL2303HX basieren, ein Kompatibilitätsproblem mit Windows 8 hatte ( siehe ). Das abscheulichste, das ich bei mir hatte, war ein Laptop mit einer Version von Windows 7 und ein Laptop mit einer Version von Windows 8 sowie verschiedene Alternativen zu diesem Kabel. Aber ich habe vor dem Seminar nicht alle Kombinationen überprüft, obwohl ich es am Abend zuvor hätte tun können - leider.2.2. Zwei Tage vor dem Workshop nahm ich Änderungen am Uhrenteiler vor. Es hat sich auch nicht gelohnt.2.3. Nun, zumindest hat im DE0-CV alles gut funktioniert.3. Bei MEPhI habe ich eine komplexere Version des Cache-Beispiels gezeigt als zuvor an der Moskauer Staatsuniversität. Es war ein Fehler - in einem komplexen Beispiel hat der Compiler etwas optimiert, und das Muster der Lichter war nicht so offensichtlich wie im ursprünglichen einfachen Beispiel. Die Situation etwas durch die eingeladen zusätzliche Lautsprecher von NIIMI Anton Pavlov gerettet wurde, der, obwohl er keine Zeit in MEPhI hatte, zeigte eine gewisse Gegenwart seine eigene Version des MIPSfpga genannt Bindung myMIPSfpga, die er auch in der Note beschrieben „MIPSfpga: außerhalb des Kanons . “ Anton hat MIPSfpga unter anderem auf das russische Board Mars Rover 3 portiert

1. Der GPIO in DE0-Nano unterscheidet sich vom GPIO in DE0-CV- und Xilinx-Karten. Insbesondere konnte ich aus irgendeinem Grund nicht den gesamten GPIO-Port als einen Inout deklarieren und dann seine einzelnen Bits entweder als Eingang oder als Ausgang verwenden. Obwohl auf DE0-CV dies gut geht. Ich hatte keine Zeit, die verschiedenen GPIO-Ausgänge auf verschiedene logische (auf Verilog) Signale aufzuteilen, also habe ich das Labor mit dem Lichtsensor auf DE0-Nano nicht sortiert. Aus dem gleichen Grund habe ich die Schnittstelle mit dem Bus Blaster nicht in den DE0-CV exportiert.2. Schlimmer noch, das Herunterladen über UART für DE0-Nano funktionierte bei MEPhI nicht, obwohl es zuvor an der Moskauer Staatsuniversität und auf meinem Laptop funktionierte. Der Grund ist immer noch nicht 100% klar:2.1. Möglicherweise gab es ein Problem mit der Inkompatibilität der Windows-Version (7 mit dem Patch) und des für DE0-Nano verwendeten USB-zu-UART-Kabels. Das Kabel war ein billiger chinesischer Kabelklon, der auf dem PL2303TA-Chipsatz basierte, obwohl ich es vor dem Seminar nicht ausprobiert habe. Es ist bekannt, dass die vorherige Version solcher Kabel, die auf Chipsätzen mit PL2303HX basieren, ein Kompatibilitätsproblem mit Windows 8 hatte ( siehe ). Das abscheulichste, das ich bei mir hatte, war ein Laptop mit einer Version von Windows 7 und ein Laptop mit einer Version von Windows 8 sowie verschiedene Alternativen zu diesem Kabel. Aber ich habe vor dem Seminar nicht alle Kombinationen überprüft, obwohl ich es am Abend zuvor hätte tun können - leider.2.2. Zwei Tage vor dem Workshop nahm ich Änderungen am Uhrenteiler vor. Es hat sich auch nicht gelohnt.2.3. Nun, zumindest hat im DE0-CV alles gut funktioniert.3. Bei MEPhI habe ich eine komplexere Version des Cache-Beispiels gezeigt als zuvor an der Moskauer Staatsuniversität. Es war ein Fehler - in einem komplexen Beispiel hat der Compiler etwas optimiert, und das Muster der Lichter war nicht so offensichtlich wie im ursprünglichen einfachen Beispiel. Die Situation etwas durch die eingeladen zusätzliche Lautsprecher von NIIMI Anton Pavlov gerettet wurde, der, obwohl er keine Zeit in MEPhI hatte, zeigte eine gewisse Gegenwart seine eigene Version des MIPSfpga genannt Bindung myMIPSfpga, die er auch in der Note beschrieben „MIPSfpga: außerhalb des Kanons . “ Anton hat MIPSfpga unter anderem auf das russische Board Mars Rover 3 portiert Die ich als durch Export-Import gefolterte Person (Scylla: amerikanische Exportkontrolle + Charybdis: russischer Zoll) für die folgenden Bildungsveranstaltungen in Russland verwenden werde: In der Pause und nach dem Seminar zeigte mir Maxim Gorbunov verschiedene mythische Sehenswürdigkeiten, darunter Drei Tafeln im Geiste der Ära der Andromeda-Galaxie und des Molecular Cafe aus rotem und weißem Multiband stammen aus dem Jahr 1960: UPD: Wie in den Kommentaren begann, über die Mifishnuyu-Kirche zu diskutieren, werde ich darauf eingehen (ich bin nicht eingefügt l Dieses Fragment war ursprünglich, da er nicht sicher war, ob es für geektimes geeignet ist):

Die ich als durch Export-Import gefolterte Person (Scylla: amerikanische Exportkontrolle + Charybdis: russischer Zoll) für die folgenden Bildungsveranstaltungen in Russland verwenden werde: In der Pause und nach dem Seminar zeigte mir Maxim Gorbunov verschiedene mythische Sehenswürdigkeiten, darunter Drei Tafeln im Geiste der Ära der Andromeda-Galaxie und des Molecular Cafe aus rotem und weißem Multiband stammen aus dem Jahr 1960: UPD: Wie in den Kommentaren begann, über die Mifishnuyu-Kirche zu diskutieren, werde ich darauf eingehen (ich bin nicht eingefügt l Dieses Fragment war ursprünglich, da er nicht sicher war, ob es für geektimes geeignet ist):

Ich ging in die mythische Kirche, um die es vor ungefähr drei Jahren im Internet so viele Schreie gab, weshalb Mitarbeiter aus Protest sogar das Moskauer Institut für technische Physik verließen. Als neutrale Person, d.h. Als wahrhaft Ungläubiger, nicht als militanter Anhänger der einen oder anderen Seite des Konflikts, muss ich sagen, dass 1) die mythische Kirche eher bescheiden und nicht vulgär ist, ähnlich wie die orthodoxe Kathedrale in San Francisco; 2) MEPhI ist nicht die erste russische Universität mit einer Religion, der Kurs für Orthodoxie erschien bereits 1988 am Moskauer Institut für Physik und Technologie (dann kam die gesamte Hochschule für Physik und Technologie zu ihm, die Studenten hörten der ersten Vorlesung zu, aber nach drei Monaten waren nicht mehr als ein Dutzend Studenten übrig); 3) Es gibt Kirchen an vielen amerikanischen Universitäten. Fortsetzung folgt.

Ich ging in die mythische Kirche, um die es vor ungefähr drei Jahren im Internet so viele Schreie gab, weshalb Mitarbeiter aus Protest sogar das Moskauer Institut für technische Physik verließen. Als neutrale Person, d.h. Als wahrhaft Ungläubiger, nicht als militanter Anhänger der einen oder anderen Seite des Konflikts, muss ich sagen, dass 1) die mythische Kirche eher bescheiden und nicht vulgär ist, ähnlich wie die orthodoxe Kathedrale in San Francisco; 2) MEPhI ist nicht die erste russische Universität mit einer Religion, der Kurs für Orthodoxie erschien bereits 1988 am Moskauer Institut für Physik und Technologie (dann kam die gesamte Hochschule für Physik und Technologie zu ihm, die Studenten hörten der ersten Vorlesung zu, aber nach drei Monaten waren nicht mehr als ein Dutzend Studenten übrig); 3) Es gibt Kirchen an vielen amerikanischen Universitäten. Fortsetzung folgt.

Source: https://habr.com/ru/post/de387157/

All Articles