3D NAND Flash Technologie

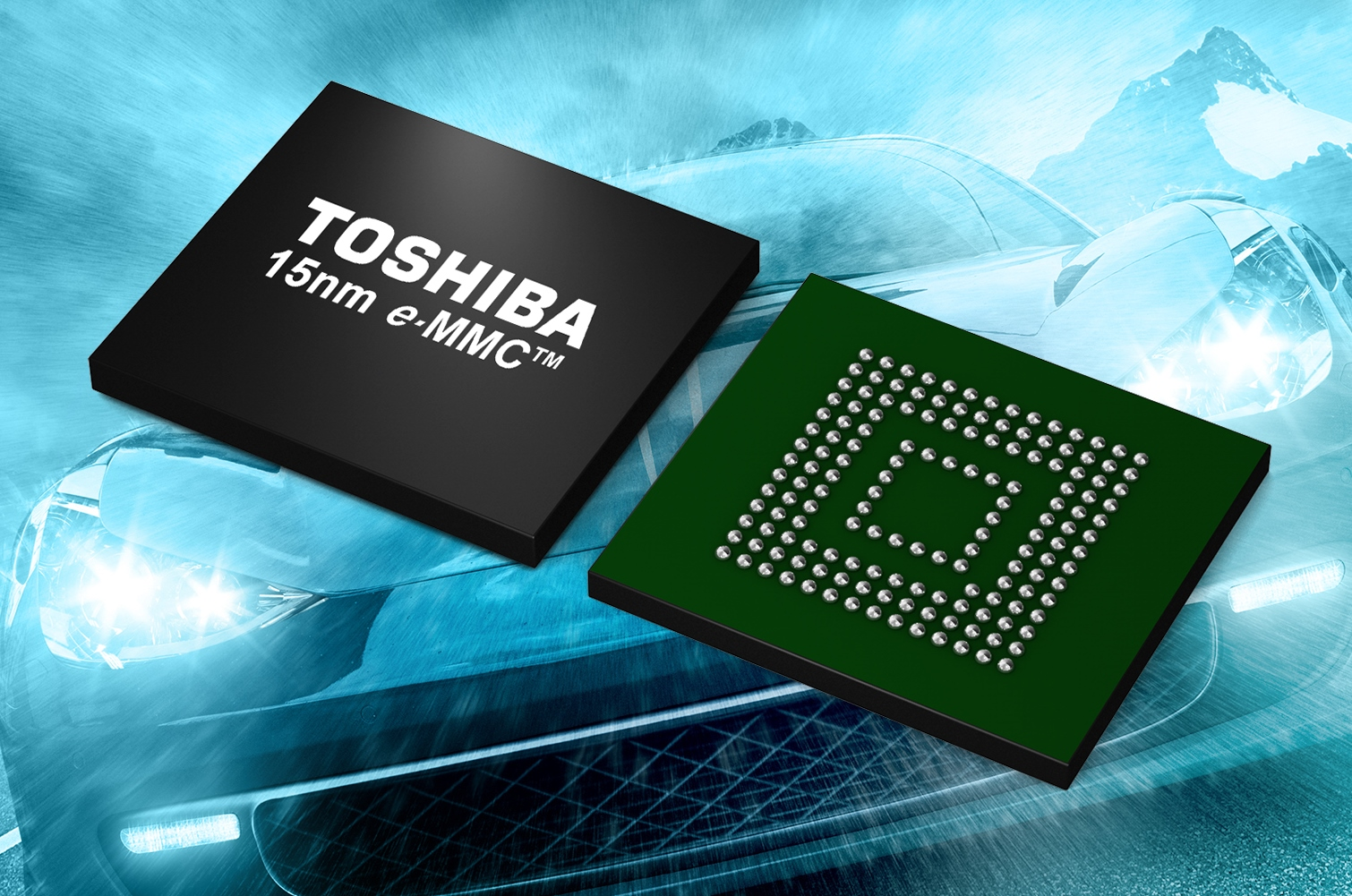

Hallo allerseits! Wie Sie wissen, hat der moderne planare NAND-Flash-Speicher sein Potenzial fast ausgeschöpft. Das Hauptproblem besteht darin, dass es zunehmend schwieriger wird, die Größe des Kristalls zu verringern. Experten zufolge werden technologische Standards von 14 bis 15 nm zumindest in naher Zukunft die Grenze des planaren Flash-Speichers bilden. Und es wird durch die Technologie des "vertikalen" Flash-Speichers - 3D NAND - ersetzt.Es ist sehr wichtig zu verstehen, was die weitere Verringerung der Größe des Kristalls verhindert. Erstens erfordert die Entwicklung feinerer Herstellungsverfahren teure Geräte, deren Kauf aus wirtschaftlicher Sicht in Zukunft möglicherweise nicht gerechtfertigt ist. Und wenn die Anschaffung neuer Lithografiemaschinen ein lösbares Problem ist, ist das Problem des Ladungsflusses von einer Zelle zur anderen, aufgrund dessen Fehler auftreten, nicht so einfach zu lösen.

Source: https://habr.com/ru/post/de391899/

All Articles