Forscher von Intel und der University of North Carolina beschleunigen den Datenaustausch zwischen CPU-Kernen um das 2-12-fache

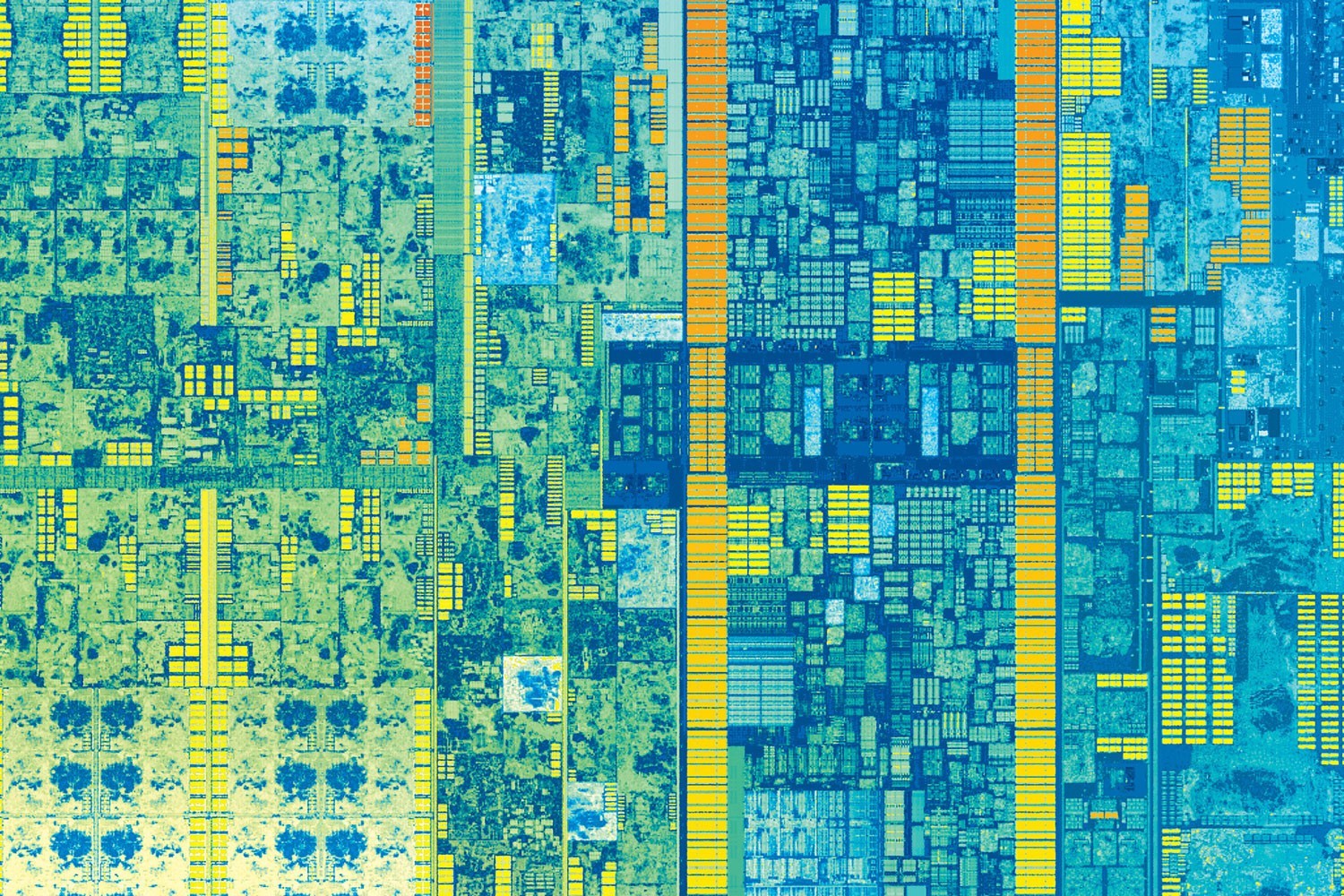

Die Topologie der siebten Generation von Intel Core-Prozessoren (ehemals Codename Kaby Lake), die Ende 2016 verfügbar sein wird. Foto: IntelEin Forscherteam der University of North Carolina und Intel hat die CAF- Technologie (Core to Core Communication Acceleration Framework) entwickelt , mit der der Datenaustausch zwischen Prozessorkernen erheblich beschleunigt werden kann. Durch die Beseitigung dieses Engpasses können Hersteller endlich die Anzahl der Kerne in der CPU erhöhen, ohne den Serviceverkehr zwischen ihnen exponentiell zu erhöhen.Bei der Implementierung paralleler Programme ist es am schwierigsten, die korrekte Koordination der zwischen den Prozessen geteilten Ressourcen sicherzustellen. Auf modernen Prozessoren erfolgt die Synchronisation der parallelen Interaktion zwischen den Kernen auf zwei Arten: unter Verwendung der Nachrichtenübermittlung und über den gemeinsam genutzten Speicher.Im ersten Fall wird auf jedem Kern ein Single-Thread-Prozess gestartet, der Daten mit anderen Prozessen austauscht, die auf anderen Kerneln ausgeführt werden.Bei der Interaktion über den gemeinsam genutzten Speicher auf jedem Prozessor eines Multiprozessorsystems wird der Ausführungsthread gestartet, der zu einem Prozess gehört. Streams tauschen Daten über einen Teil des Speichers aus, der diesem Prozess gemeinsam ist. Die Anzahl der Threads entspricht der Anzahl der Prozessoren.Die Forscher schlagen vor, eine solche Ressourcenkoordination umzusetzenauf Hardware-Ebene . In der Zusammenfassung der vorbereiteten wissenschaftlichen Arbeit stellen sie fest, dass „die Interaktion durch das gemeinsame Gedächtnis naturgemäß Behinderungen zur Aufrechterhaltung der Kohärenz und Cache-Fehler umfasst, was den Overhead erheblich erhöht und eine große Menge an [übermäßigem] Netzwerkverkehr erzeugt“.Viele wichtige Aufgaben erfordern einen großen Datenverkehr zwischen den Kernen, sodass eine erhebliche Erhöhung des Overheads einen enormen Leistungseinbruch bedeutet. Dies gilt auch für die Leistung der Computer-Pipeline, die in Softwarelösungen für den Betrieb von Parallelität auf Befehlsebene weit verbreitet ist.Die Hardwarebeschleunigung koordiniert die Arbeit der Kerne beim parallelen Rechnen. Die vorgeschlagene Hardware-Kernkoordination ist viel effizienter als alle derzeit verwendeten Software-Synchronisationsmethoden."Dieser Ansatz, den wir als CAF- Framework zur Beschleunigung der Kommunikation zwischen Kernen bezeichnet haben , verbessert die Datenübertragung um das 2-12-fache", sagte Yan Solihin, Professor für Elektro- und Computertechnik an der University of North Carolina und Mitautor der Forschung. "Mit anderen Worten, die Ausführungsgeschwindigkeit - von Anfang bis Ende - ist mindestens doppelt so hoch."In der vorbereiteten wissenschaftlichen Arbeit führten die Autoren eine Analyse des Overheads (übermäßiger Netzwerkverkehr zwischen den Kernen) durch, der beim Synchronisieren paralleler Berechnungen mit vorhandenen Softwaremethoden auftritt. Und sie schlugen eine alternative Lösung vor.Ein Schlüsselelement des neuen Frameworks ist das Warteschlangenverwaltungshardwaremodul QMD (Queue Management Device). Es kann einfache Rechenfunktionen ausführen und ist mit der Hardware an das Kommunikationssubsystem angeschlossen, dh an NoC (ein Netzwerk auf einem Chip - ein Mini-Internet im Prozessor ).

Die Topologie der siebten Generation von Intel Core-Prozessoren (ehemals Codename Kaby Lake), die Ende 2016 verfügbar sein wird. Foto: IntelEin Forscherteam der University of North Carolina und Intel hat die CAF- Technologie (Core to Core Communication Acceleration Framework) entwickelt , mit der der Datenaustausch zwischen Prozessorkernen erheblich beschleunigt werden kann. Durch die Beseitigung dieses Engpasses können Hersteller endlich die Anzahl der Kerne in der CPU erhöhen, ohne den Serviceverkehr zwischen ihnen exponentiell zu erhöhen.Bei der Implementierung paralleler Programme ist es am schwierigsten, die korrekte Koordination der zwischen den Prozessen geteilten Ressourcen sicherzustellen. Auf modernen Prozessoren erfolgt die Synchronisation der parallelen Interaktion zwischen den Kernen auf zwei Arten: unter Verwendung der Nachrichtenübermittlung und über den gemeinsam genutzten Speicher.Im ersten Fall wird auf jedem Kern ein Single-Thread-Prozess gestartet, der Daten mit anderen Prozessen austauscht, die auf anderen Kerneln ausgeführt werden.Bei der Interaktion über den gemeinsam genutzten Speicher auf jedem Prozessor eines Multiprozessorsystems wird der Ausführungsthread gestartet, der zu einem Prozess gehört. Streams tauschen Daten über einen Teil des Speichers aus, der diesem Prozess gemeinsam ist. Die Anzahl der Threads entspricht der Anzahl der Prozessoren.Die Forscher schlagen vor, eine solche Ressourcenkoordination umzusetzenauf Hardware-Ebene . In der Zusammenfassung der vorbereiteten wissenschaftlichen Arbeit stellen sie fest, dass „die Interaktion durch das gemeinsame Gedächtnis naturgemäß Behinderungen zur Aufrechterhaltung der Kohärenz und Cache-Fehler umfasst, was den Overhead erheblich erhöht und eine große Menge an [übermäßigem] Netzwerkverkehr erzeugt“.Viele wichtige Aufgaben erfordern einen großen Datenverkehr zwischen den Kernen, sodass eine erhebliche Erhöhung des Overheads einen enormen Leistungseinbruch bedeutet. Dies gilt auch für die Leistung der Computer-Pipeline, die in Softwarelösungen für den Betrieb von Parallelität auf Befehlsebene weit verbreitet ist.Die Hardwarebeschleunigung koordiniert die Arbeit der Kerne beim parallelen Rechnen. Die vorgeschlagene Hardware-Kernkoordination ist viel effizienter als alle derzeit verwendeten Software-Synchronisationsmethoden."Dieser Ansatz, den wir als CAF- Framework zur Beschleunigung der Kommunikation zwischen Kernen bezeichnet haben , verbessert die Datenübertragung um das 2-12-fache", sagte Yan Solihin, Professor für Elektro- und Computertechnik an der University of North Carolina und Mitautor der Forschung. "Mit anderen Worten, die Ausführungsgeschwindigkeit - von Anfang bis Ende - ist mindestens doppelt so hoch."In der vorbereiteten wissenschaftlichen Arbeit führten die Autoren eine Analyse des Overheads (übermäßiger Netzwerkverkehr zwischen den Kernen) durch, der beim Synchronisieren paralleler Berechnungen mit vorhandenen Softwaremethoden auftritt. Und sie schlugen eine alternative Lösung vor.Ein Schlüsselelement des neuen Frameworks ist das Warteschlangenverwaltungshardwaremodul QMD (Queue Management Device). Es kann einfache Rechenfunktionen ausführen und ist mit der Hardware an das Kommunikationssubsystem angeschlossen, dh an NoC (ein Netzwerk auf einem Chip - ein Mini-Internet im Prozessor ). Illustration aus dem Artikel " Netzwerk auf einem Chip - Mini-Internet im Prozessor "Das QMD-Modul übernimmt die Verwaltung der Warteschlange und die Synchronisierung der parallelen Interaktion der Kerne ohne zusätzliche Softwareanweisungen auf den CPU-Kernen. Es ist wie ein Hardware-Router in einem Netzwerk.Die zukünftige Entwicklung ist wichtig angesichts der stetigen Zunahme der Kerne auf modernen Prozessoren. Dies ist ein völlig natürlicher Vorgang, da die Taktrate aufgrund natürlicher physikalischer Einschränkungen fast zum Stillstand gekommen ist. Die Hersteller haben keine andere Wahl, als die Berechnungen zu parallelisieren.Unter solchen Bedingungen wird die Synchronisation der parallelen Interaktion zwischen den Kernen zum Engpass, der die Systemleistung einschränkt. Mit einem effizienten Verkehrsrouting zwischen Prozessorkernen können Sie die CPU-Architektur weiter skalieren und Prozessoren mit zehn oder Hunderten von Kernen mit nahezu linearer Leistungsskalierung erstellen. Effizientes Verkehrsrouting zwischen Kernen ist eine Schlüsseltechnologie, die zur weiteren Skalierung der Multi-Core-CPU-Architektur erforderlich ist.Das QMD-Modul beschleunigt nicht nur den Datenaustausch zwischen Kernen wiederholt, während es das parallele Rechnen synchronisiert, sondern kann auch beim Aggregieren von Daten aus mehreren Kernen hilfreich sein. Forscher glauben, dass dies die Verarbeitung einiger grundlegender Rechenvorgänge um bis zu 15% beschleunigen wird.Die wissenschaftliche Arbeit " CAF: Core to Core Communication Acceleration Framework " wird auf der 25. Konferenz über parallele Architekturen und Kompilierungsmethoden PACT '16 vorgestellt , die vom 11. bis 15. September 2016 in Haifa (Israel) stattfinden wird.Die Erfinder sind Yipeng Wang (Universität von North Carolina), Ren Wang, Andrew Herdrich und James Tsai (alle Intel Corp.), und der Hauptautor des Papiers ist der oben genannte Yan Solihin von der University of North Carolina und der US National Science Foundation.Der Artikel wurde in die Proceedings der Internationalen Konferenz für parallele Architekturen und Kompilierung 2016 aufgenommen, S. 351-362, doi: 10.1145 / 2967938.2967954. Die Sammlung von Berichten wird wahrscheinlich an Konferenzteilnehmer verteilt und im Internet veröffentlicht.

Illustration aus dem Artikel " Netzwerk auf einem Chip - Mini-Internet im Prozessor "Das QMD-Modul übernimmt die Verwaltung der Warteschlange und die Synchronisierung der parallelen Interaktion der Kerne ohne zusätzliche Softwareanweisungen auf den CPU-Kernen. Es ist wie ein Hardware-Router in einem Netzwerk.Die zukünftige Entwicklung ist wichtig angesichts der stetigen Zunahme der Kerne auf modernen Prozessoren. Dies ist ein völlig natürlicher Vorgang, da die Taktrate aufgrund natürlicher physikalischer Einschränkungen fast zum Stillstand gekommen ist. Die Hersteller haben keine andere Wahl, als die Berechnungen zu parallelisieren.Unter solchen Bedingungen wird die Synchronisation der parallelen Interaktion zwischen den Kernen zum Engpass, der die Systemleistung einschränkt. Mit einem effizienten Verkehrsrouting zwischen Prozessorkernen können Sie die CPU-Architektur weiter skalieren und Prozessoren mit zehn oder Hunderten von Kernen mit nahezu linearer Leistungsskalierung erstellen. Effizientes Verkehrsrouting zwischen Kernen ist eine Schlüsseltechnologie, die zur weiteren Skalierung der Multi-Core-CPU-Architektur erforderlich ist.Das QMD-Modul beschleunigt nicht nur den Datenaustausch zwischen Kernen wiederholt, während es das parallele Rechnen synchronisiert, sondern kann auch beim Aggregieren von Daten aus mehreren Kernen hilfreich sein. Forscher glauben, dass dies die Verarbeitung einiger grundlegender Rechenvorgänge um bis zu 15% beschleunigen wird.Die wissenschaftliche Arbeit " CAF: Core to Core Communication Acceleration Framework " wird auf der 25. Konferenz über parallele Architekturen und Kompilierungsmethoden PACT '16 vorgestellt , die vom 11. bis 15. September 2016 in Haifa (Israel) stattfinden wird.Die Erfinder sind Yipeng Wang (Universität von North Carolina), Ren Wang, Andrew Herdrich und James Tsai (alle Intel Corp.), und der Hauptautor des Papiers ist der oben genannte Yan Solihin von der University of North Carolina und der US National Science Foundation.Der Artikel wurde in die Proceedings der Internationalen Konferenz für parallele Architekturen und Kompilierung 2016 aufgenommen, S. 351-362, doi: 10.1145 / 2967938.2967954. Die Sammlung von Berichten wird wahrscheinlich an Konferenzteilnehmer verteilt und im Internet veröffentlicht.Source: https://habr.com/ru/post/de397275/

All Articles