Vorwort

Ich freue mich sehr, ausführlich über meine erste integrierte Schaltung zu berichten und die Wendungen dieses Projekts zu teilen, an dem ich im letzten Jahr beteiligt war. Ich hoffe, mein Erfolg wird andere inspirieren und dazu beitragen, die Produktion von Heimchips zu revolutionieren. Als ich dieses Projekt startete, hatte ich keine Ahnung, worauf ich mich einließ, aber am Ende lernte ich mehr als ich jemals über Physik, Chemie, Optik, Elektronik und viele andere Bereiche gedacht hatte.

Darüber hinaus wurden meine Bemühungen nur von den positivsten Bewertungen und der Unterstützung aus der ganzen Welt begleitet. Ich bin allen aufrichtig dankbar, die mir geholfen, Ratschläge gegeben und für dieses Projekt inspiriert haben. Besonders an meine großartigen Eltern, die mich nicht nur immer unterstützen und ermutigen, sobald sie können, sondern auch einen Arbeitsplatz geschaffen und die Stromkosten in Kauf genommen haben ... Danke!

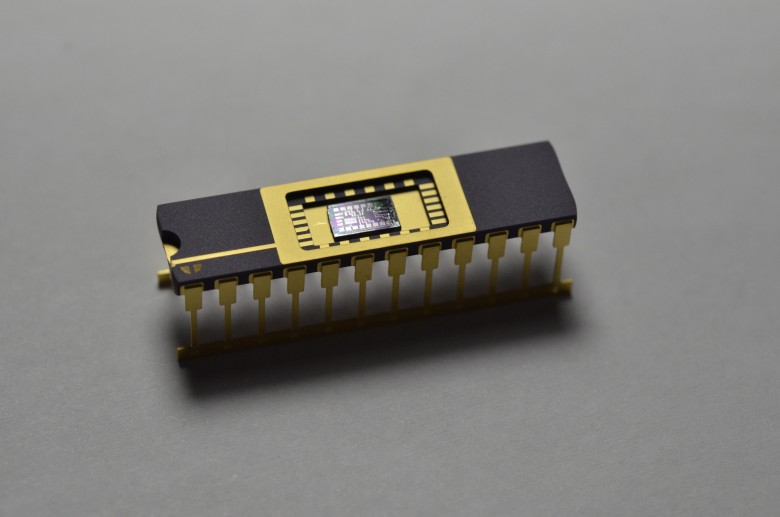

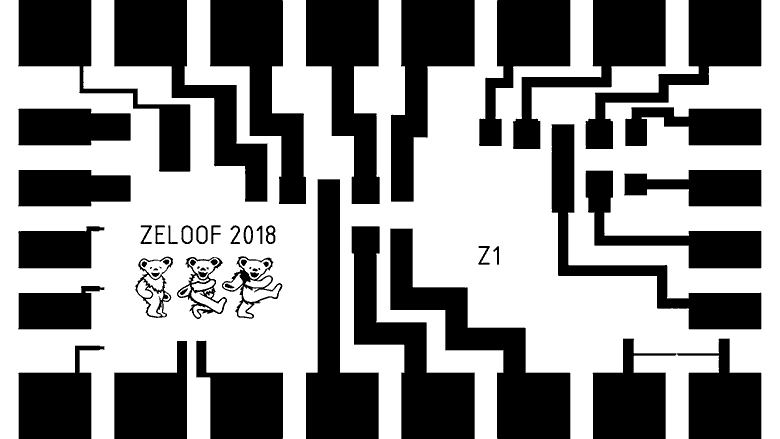

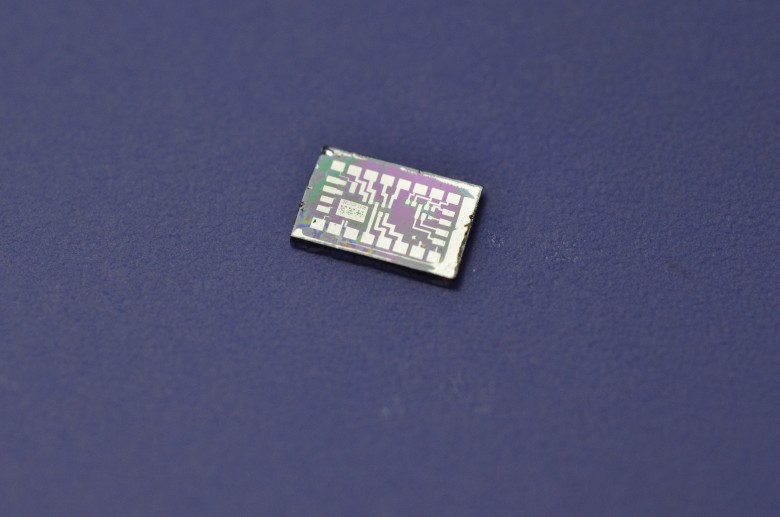

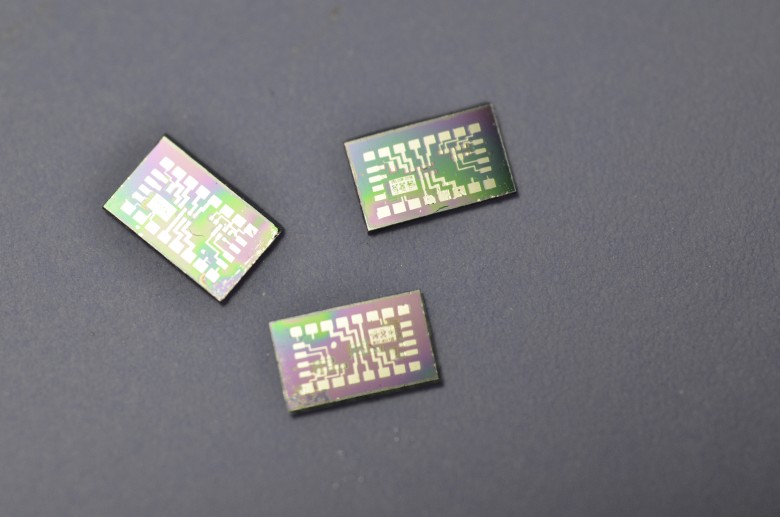

Ohne weiteres stelle ich die erste integrierte Schaltung (IC) vor, die nach der Lithografie unter Heim- (Garagen-) Bedingungen hergestellt wurde - den PMOS-Chip des Z1-Doppeldifferentialverstärkers.

Ich sage "hergestellt durch lithografische Methode", weil Jerry Ellsworth die ersten Transistoren und Logikgatter (mit sorgfältig von Hand leitendem Epoxidharz verlegten Verbindungen) herstellte und der Welt zeigte, dass dies möglich ist. Inspiriert von ihrer Arbeit präsentiere ich integrierte Schaltkreise, die nach einem skalierbaren Standard-Fotolithografieverfahren erstellt wurden. Dies ist natürlich ein logischer Schritt vorwärts im Vergleich zu meiner vorherigen Arbeit, bei der ich

den Jerry-Feldeffekttransistor reproduziert habe .

Design

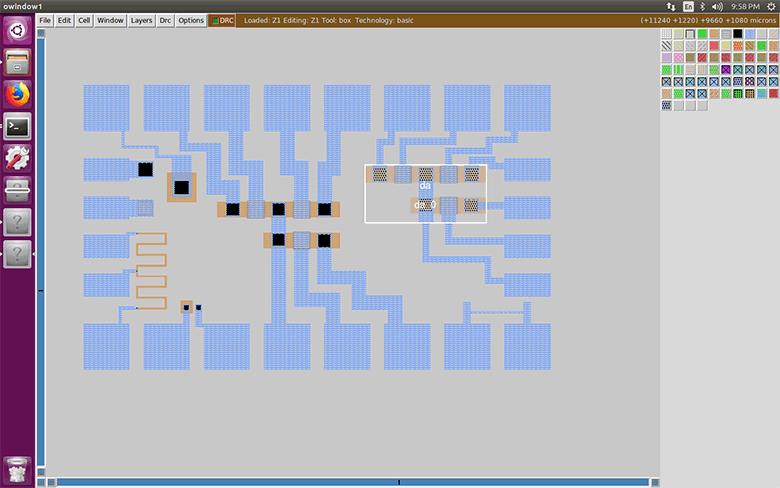

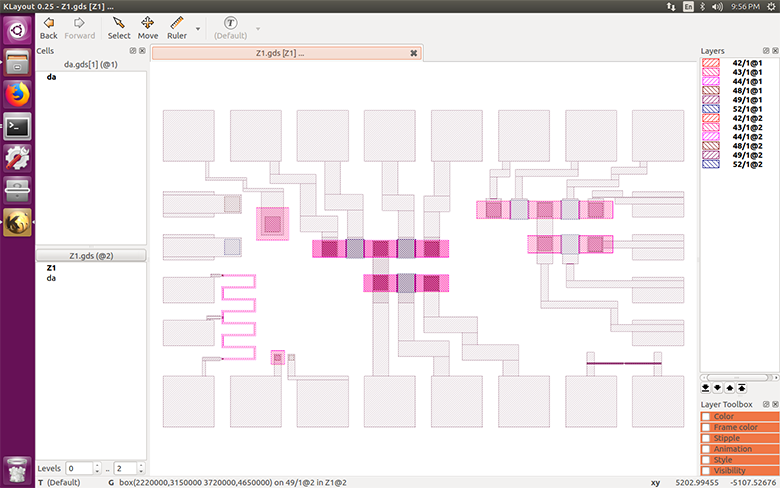

Ich habe

den Z1-Verstärker entwickelt, als ich nach einem einfachen Chip suchte, um meinen Prozess zu testen und abzustimmen. Das Layout wurde in

Magic VLSI für den PMOS-Prozess mit vier Masken (aktiver / dotierter Bereich, Gateoxid, Kontaktfenster und obere Metallschicht) erstellt. PMOS hat einen Vorteil gegenüber NMOS, wenn ionische Verunreinigungen aufgrund der Herstellung in einer Garage berücksichtigt werden. Masken sind mit einem Seitenverhältnis von 16: 9 ausgelegt, um die Projektion zu vereinfachen.

Magisches VLSI-Layout

Magisches VLSI-Layout Maskenerstellung

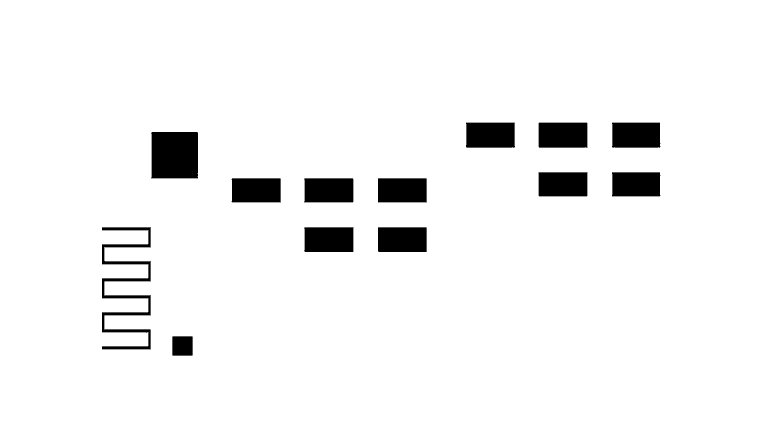

Maskenerstellung Aktiver Bereich

Aktiver Bereich Verschluss

Verschluss Kontakt

Kontakt Metall

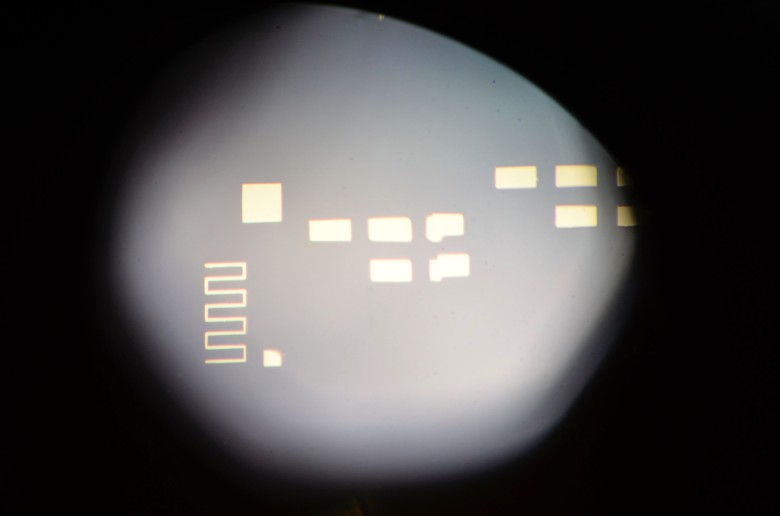

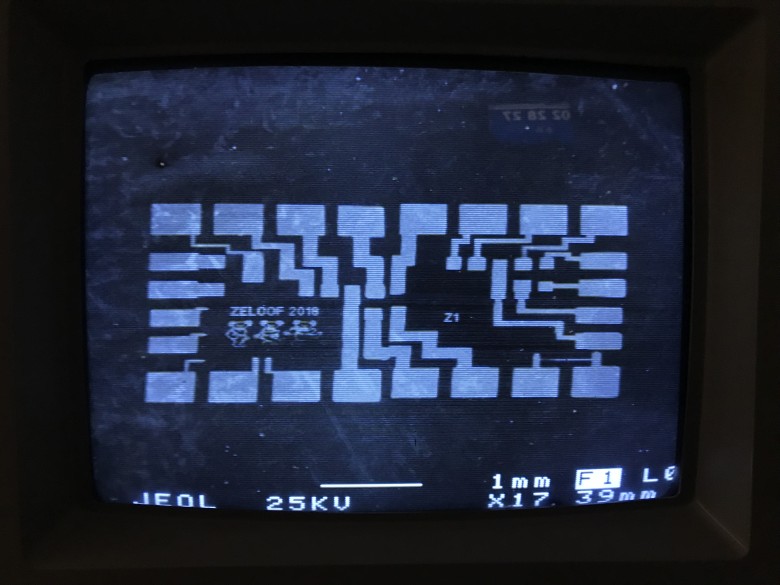

MetallDie Verschlussgröße beträgt ungefähr 175 Mikrometer, obwohl Elemente bis zu 2 Mikrometer zur Überprüfung auf dem Chip hergestellt werden. Jeder Verstärkerabschnitt (Mitte und rechts) enthält drei Transistoren (zwei für eine

Gegentaktschaltung mit einem gemeinsamen Kathodenwiderstand und einen als Stromquelle / Lastwiderstand), was insgesamt sechs Transistoren pro IC bedeutet. Die linke Seite der Widerstände, Kondensatoren, Dioden und anderer Testelemente, um die Eigenschaften des Prozesses zu untersuchen. Jeder Knoten der Differentialpaare verfügt über einen separaten Pin am Ausgangsrahmen, sodass er untersucht werden kann und bei Bedarf ein externer Offset hinzugefügt werden kann.

Herstellung

Der Herstellungsprozess besteht aus 66 Einzelschritten und dauert ca. 12 Stunden. Die Ausbeute erreicht bei großen Artikeln 80%, hängt jedoch stark von der Kaffeemenge ab, die Sie an einem bestimmten Tag trinken. Ich habe auch ein Video auf YouTube über die

Theorie der Herstellung von Mikroschaltungen und

über die separate Herstellung von MOS-Transistoren aufgenommen .

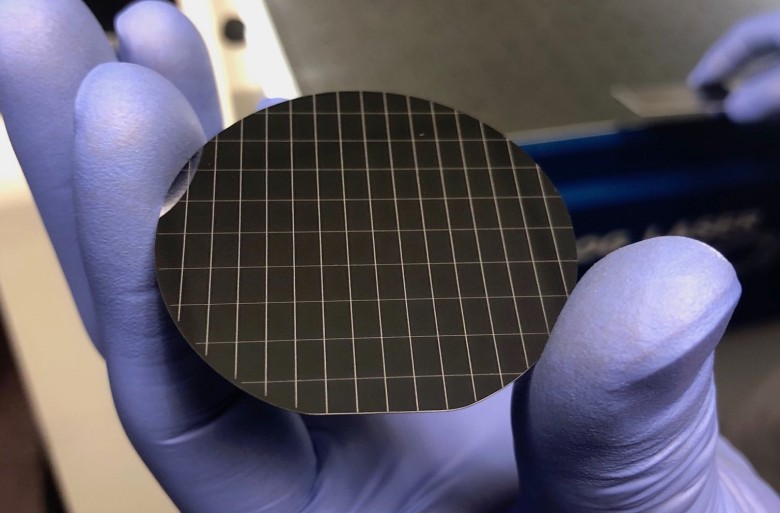

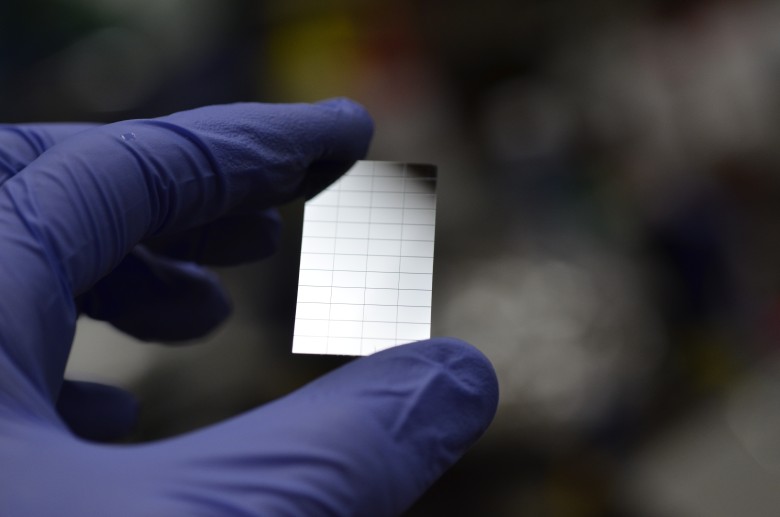

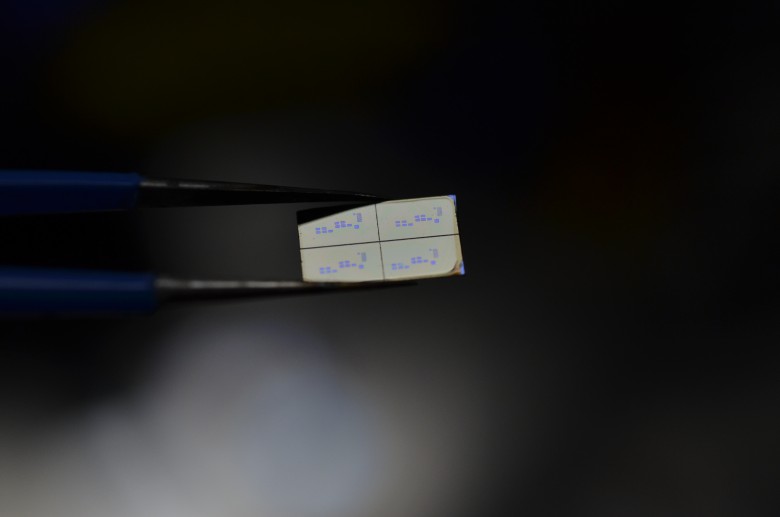

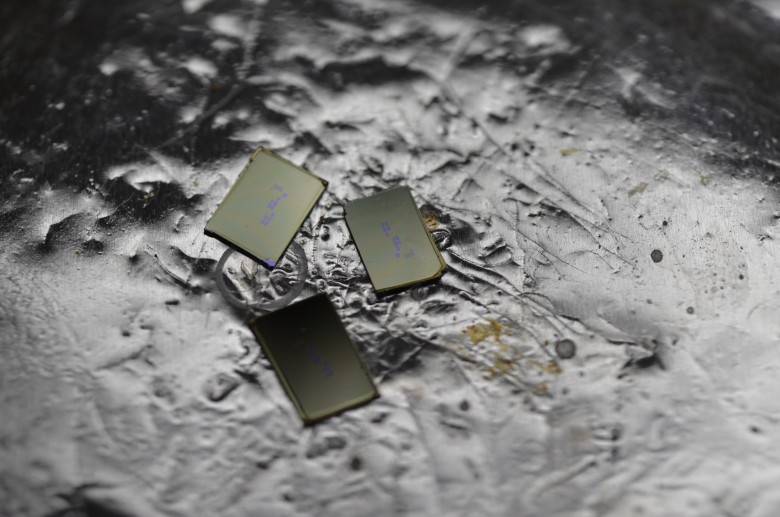

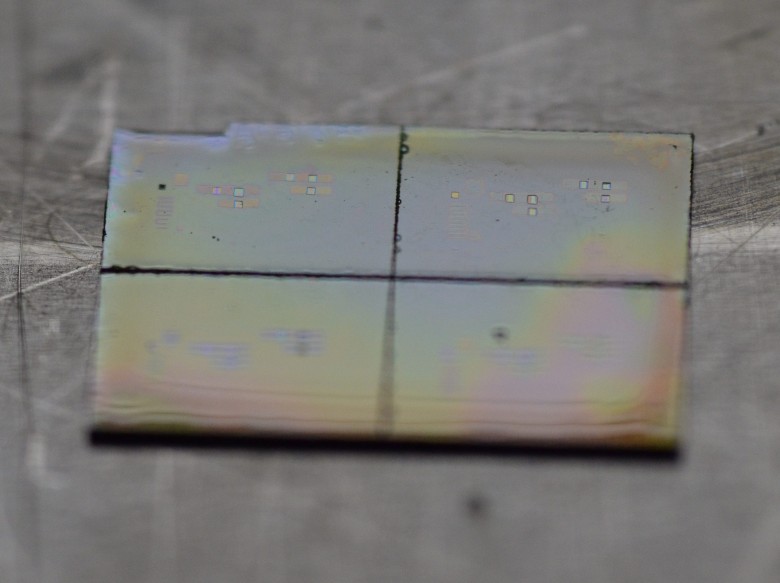

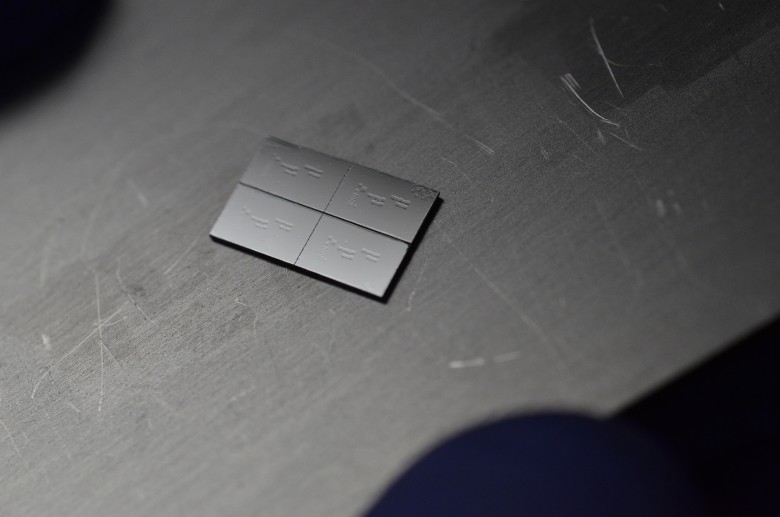

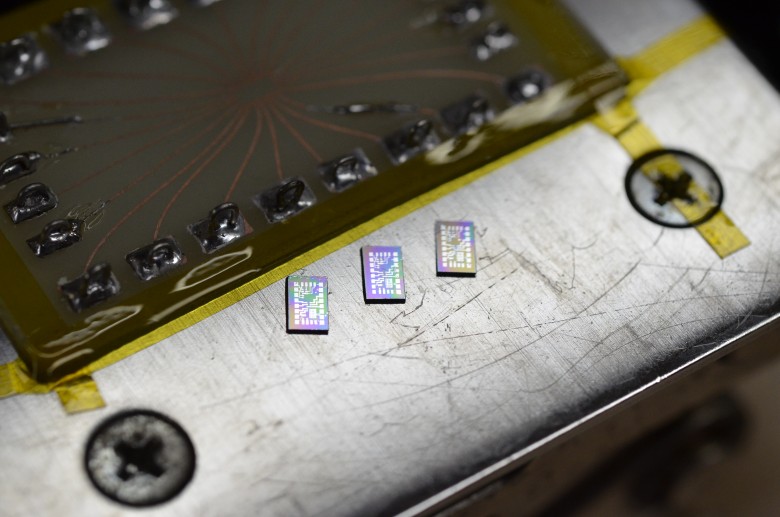

50 mm (2 ") Siliziumwafer werden

mit einem Epilog-Faserlaser in Kristalle von 5,08 x 3,175 mm (ca. 16 mm² Fläche) zerbrochen. Die Größe des Kristalls wird so gewählt, dass er in das 24-polige DIP-Gehäuse von Kyocera passt.

N-Typ Platte 50 mm

N-Typ Platte 50 mm N-Typ Platte 50 mm

N-Typ Platte 50 mmZunächst wird natives Oxid durch schnelles Eintauchen in verdünnten Fluorwasserstoff von der Platte entfernt, gefolgt von einer intensiven Behandlung mit einem Piranha-Ätzgemisch (einem Gemisch aus Schwefelsäure und Wasserstoffperoxid), einem Gemisch aus RCA 1 (Wasser, Ammoniak, Wasserstoffperoxid), einem Gemisch aus RCA 2 (Wasser, Salzsäure, Wasserstoffperoxid) und wiederholtes Eintauchen in Fluorwasserstoff.

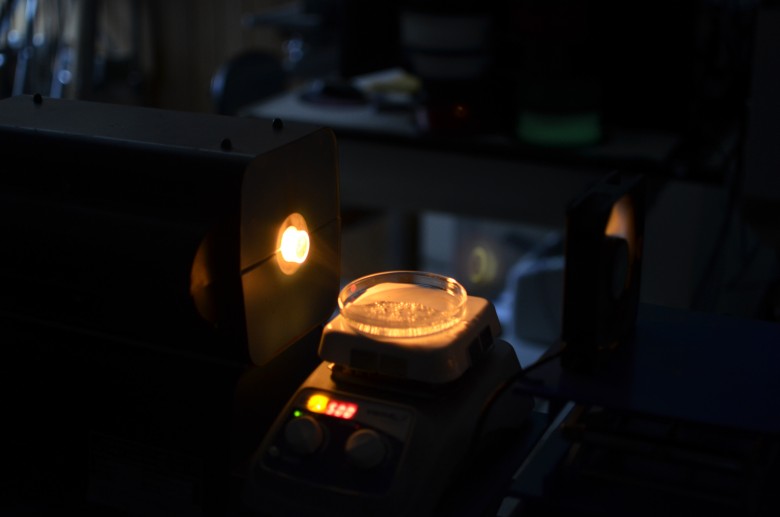

Schutzoxid

wird in Wasserdampf der Umgebungsluft (Nassoxidation) bis zu einer Dicke von 5000-8000 Å

thermisch gezüchtet .

Nasse thermische Oxidation

Nasse thermische Oxidation Nasse thermische Oxidation

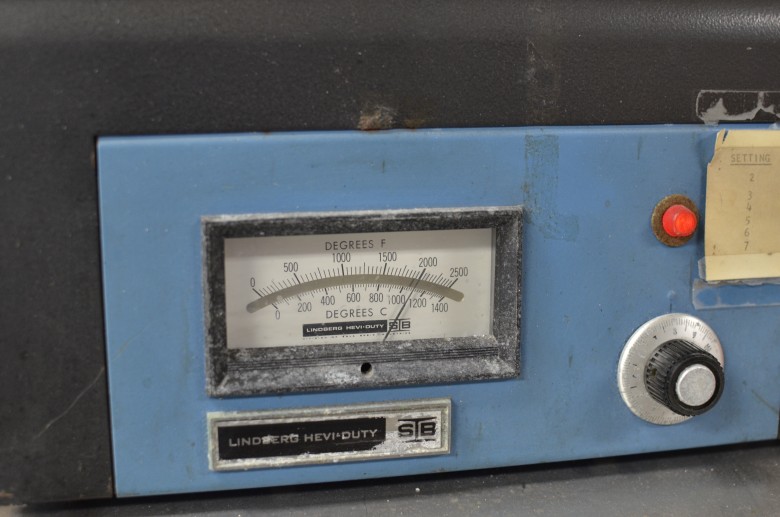

Nasse thermische Oxidation Rohrofen

Rohrofen Oxidierte Platte

Oxidierte PlatteDie oxidierte Platte ist bereit, sich im aktiven / dotierten Bereich (P-Typ) zu bilden. Der

AZ4210- Fotolack wird auf eine

Brust aufgetragen,

die sich mit etwa 3000 U / min dreht und einen etwa 3,5 Mikrometer dicken Film bildet, der bei 90 ° C auf einer

Heizplatte vorsichtig getrocknet wird.

Lithographieprozess im DetailDie Kernmaske wird von meinem

photolithografischen Stepper Mark IV im ultravioletten Bereich mit einem Schritt von 365 nm verarbeitet - und die Struktur in einer Lösung von Kaliumhydroxid ausgearbeitet.

Resist Struktur

Resist Struktur Resist Struktur

Resist Struktur 30 Minuten Trocknen

30 Minuten Trocknen Kernätzung

KernätzungDanach wird die Resiststruktur verfestigt und

verschiedene andere Tricks werden verwendet, um eine gute Haftung und chemische Beständigkeit beim nächsten Ätzen in Fluorwasserstoff sicherzustellen, wodurch diese Struktur auf die Gateoxidschicht übertragen wird und die Fenster geöffnet werden, um Silizium zum Dotieren freizulegen. Diese Bereiche werden später die Source und Drain des Transistors.

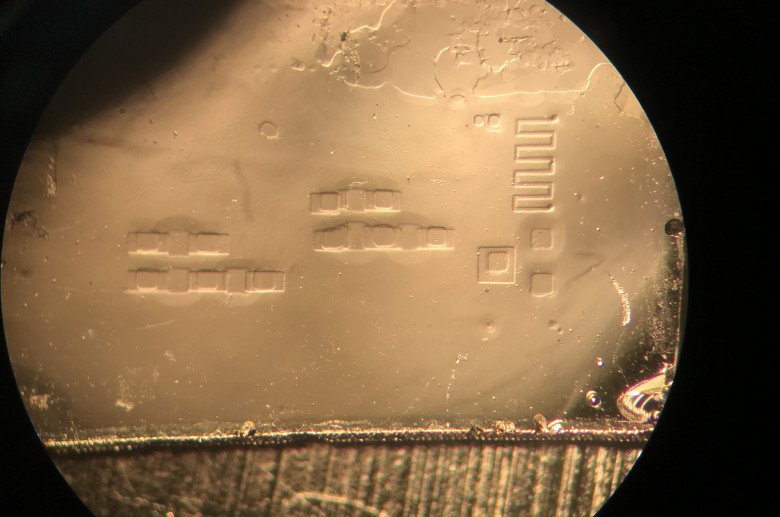

Partikel schließen den Verschluss

Partikel schließen den Verschluss Legierungskristalle mit geätzten Toren

Legierungskristalle mit geätzten TorenDanach wird das Legieren durchgeführt, dh das Einbringen von Verunreinigungen aus einer festen oder flüssigen Quelle. Als feste Quelle wird eine Bornitridscheibe verwendet, die sich in der Nähe (weniger als 2 mm) von der Platte in einem Rohrofen befindet. Alternativ können Sie eine flüssige Phosphor- oder Borsäurequelle in Wasser oder einem Lösungsmittel herstellen - und gemäß dem Standardverfahren zum

Aufbringen / Eintauchen in Fluorwasserstoff / Diffusion / Entfernen der Glasur dotieren .

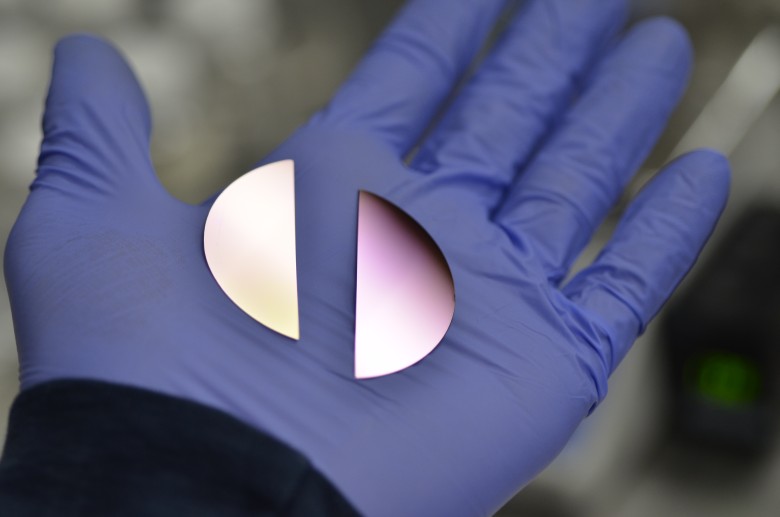

Die obigen Strukturierungsschritte werden dann zweimal für das Gateoxid und die Kontaktschicht wiederholt. Das Gateoxid sollte viel dünner sein (weniger als ~ 750 Å) als das Schutzoxid, damit die Zonen zwischen Drain / Source geätzt werden - und dort ein dünneres Oxid wächst. Da dann die gesamte Platte beim Dotierungsschritt oxidiert wurde, müssen die Kontaktfenster geätzt werden, um den Kontakt der Metallschicht mit den dotierten Source / Drain-Zonen herzustellen.

Jetzt sind alle Transistoren ausgebildet und bereit für Verbindungen mit Zugriff auf den Ausgangsrahmen. Die Schutzschicht aus Aluminium (400-500 nm) wird auf die Platte

gesprüht oder

thermisch gesprüht . Eine Alternative wäre der Abhebevorgang, bei dem zuerst ein Fotolack gebildet und dann das Metall abgeschieden wird.

Metall besprüht

Metall besprüht Metall besprüht

Metall besprühtDann wird ein Photolithographiemuster auf der Metallschicht gebildet und in heißer Phosphorsäure geätzt, um die Herstellung der integrierten Schaltung abzuschließen. Die letzten Schritte vor dem Testen sind die Sichtprüfung und das Hochtemperaturglühen von Aluminium unter Bildung ohmscher Übergänge.

Der Chip ist jetzt zum Verpacken und Testen bereit.

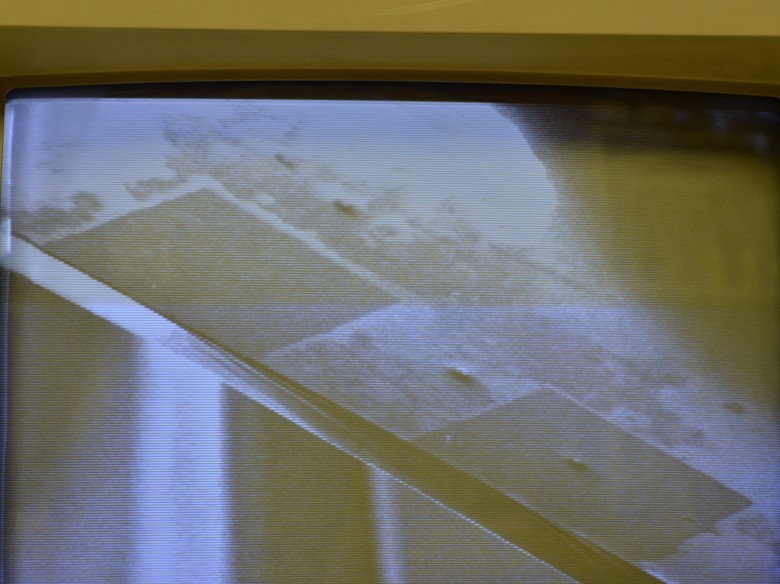

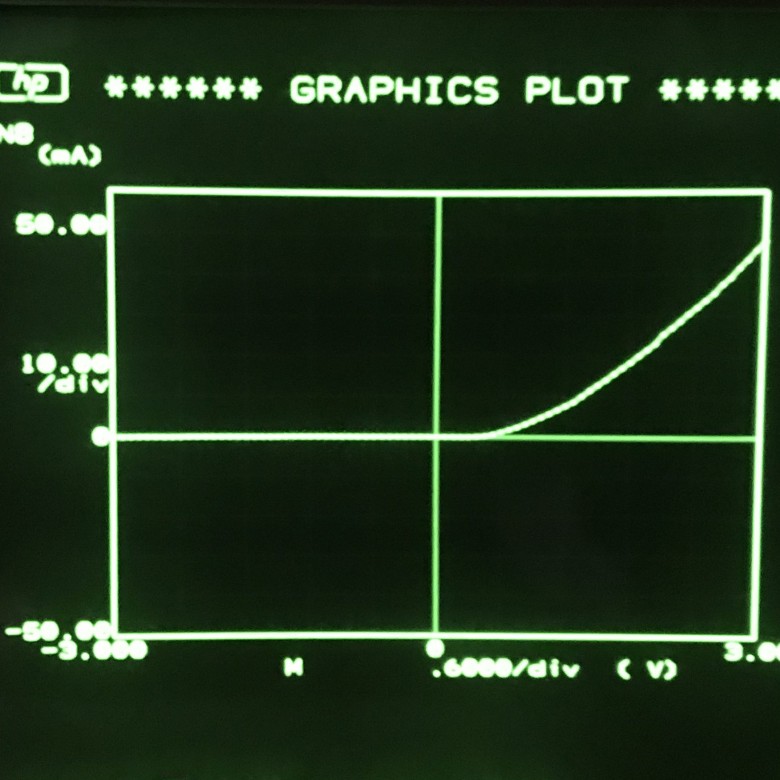

Ich habe keine Mikrowellen-Installation (ich nehme Spenden an!). Daher beschränkt sich der Testprozess jetzt darauf, die Platte mit einer scharfen Pinzette abzutasten oder eine Flip-Chip-Platine (schwer auszurichten) mit einer Verbindung zum Charakterographen zu verwenden. Der Differenzverstärker wird auch empirisch in der Schaltung getestet, um die Funktionsfähigkeit zu überprüfen.

Kurve IV

Kurve IV Kurve IVFET-IDs / Vds-Kurve vom vorherigen NMOS-Gerät

Kurve IVFET-IDs / Vds-Kurve vom vorherigen NMOS-GerätNatürlich sind diese Kurven alles andere als ideal (auch aufgrund eines übermäßigen Kontaktwiderstands und anderer ähnlicher Faktoren), aber ich erwarte eine Verbesserung der Leistung, wenn ich Mikroschweißen installiere. Dies kann teilweise einige Unterschiede von Kristall zu Kristall erklären. In Kürze werde ich

dieser Seite neue IV-Kurven, Transistor- und Differenzverstärkereigenschaften hinzufügen.