In jedem Artikel über Habré, der sich auf die eine oder andere Weise mit inländischen Mikroprozessoren befasst, wird die Frage der lizenzierten IP-Blöcke und wie stark ihre Anwesenheit und Abwesenheit den Wert, die Häuslichkeit oder die Sicherheit der Entwicklung verringert, angesprochen. Gleichzeitig verstehen viele Kommentatoren das Diskussionsthema nicht sehr gut. Versuchen wir also, genau herauszufinden, wie die Lizenzierung in der mikroelektronischen Industrie funktioniert, was gute und schlechte lizenzierte Blöcke sind und wie die Entwicklung einer Mikroschaltung abläuft, wenn die meisten Blöcke darin gekauft werden.

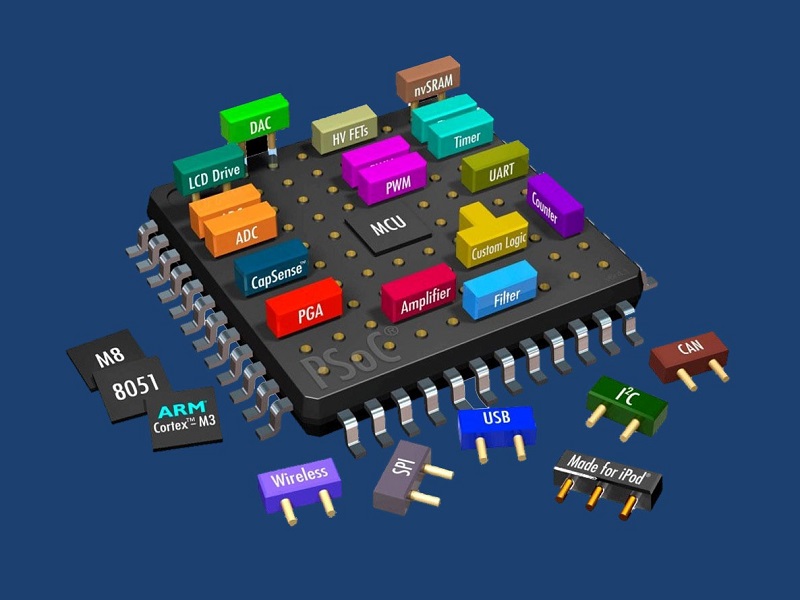

Jede moderne Mikroschaltung wurde vor einiger Zeit stolz als „System auf einem Chip“ bezeichnet: Selbst dreibeinige Linearregler und Spannungsquellen haben eine digitale Einstellung, die dem Benutzer verborgen bleibt. Was können wir über Mikroprozessoren und Mikrocontroller sagen, die Dutzende verschiedener Blöcke enthalten, deren Entwicklung Davon sind spezielle Fähigkeiten und umfangreiche Erfahrung erforderlich, um Fallstricke zu umgehen, über die nicht in Büchern und Artikeln geschrieben wird. Darüber hinaus verfügt jedes Projekt in der Regel über eine eigene Killer-Funktion, aufgrund derer Entwickler einen Vorteil gegenüber Wettbewerbern erwarten. Diese Killer-Funktion sollte so gut wie möglich ausgeführt werden, und alle anderen Blöcke sollten einfach nicht schlechter sein als andere.

Achtung, die Frage ist: Ist es notwendig, ein teures Entwicklungsteam zu unterhalten, das alle notwendigen Blöcke unabhängig voneinander selbst herstellen kann?

Eine noch interessantere Frage: Wenn Sie selbst ein Mikroprozessor-Befehlssystem entwickelt haben, müssen Sie ein Programmiererteam enthalten,

das einen Compiler dafür schreibt , neue Kernel gängiger Betriebssysteme portiert, viele andere harte Arbeiten ausführt und Ihre Kreation höchstwahrscheinlich nicht auf eines setzt Niveau mit populären Architekturen, auf denen viel mehr Menschen arbeiten?

Und vor allem: Werden positive Antworten auf die beiden vorherigen Fragen Ihrem Produkt Wettbewerbsvorteile verschaffen?

Lyrischer ExkursAm 5. Juni ging Morris Chang in den Ruhestand, ein Mann, von dem Sie noch nie gehört hatten, ohne den es jedoch keine moderne Elektronik geben würde. Morris Chang wurde in China geboren, auf dem Höhepunkt des Bürgerkriegs, den er in die USA verließ, absolvierte das MIT und arbeitete dann viele Jahre bei Texas Instruments und General Instruments. In jenen Jahren war ein wesentlicher Bestandteil eines jeden mikroelektronischen Unternehmens seine eigene Produktion, deren Ausrüstung mehrere Größenordnungen billiger war als jetzt, aber dennoch sehr teuer. So schrieb Chang selbst darüber:

Als ich bei TI und General Instrument war, sah ich viele IC-Designer, die gehen und ihr eigenes Unternehmen gründen wollten, aber das einzige oder größte, was sie davon abhielt, diese Unternehmen zu verlassen, war, dass sie nicht genug Geld sammeln konnten eine eigene Firma zu gründen. Denn zu dieser Zeit glaubte man, dass jedes Unternehmen eine Herstellung brauchte, eine Waferherstellung und das war der kapitalintensivste Teil eines Halbleiterunternehmens, eines IC-Unternehmens. Und ich sah all die Leute, die gehen wollten, aber durch die mangelnde Fähigkeit, viel Geld für den Bau einer Waffelfabrik zu sammeln, gestoppt wurden.

1985 wollte Morris Chang in den Ruhestand gehen, nahm jedoch das Angebot der taiwanesischen Regierung an, am Industrial Technology Research Institute zu arbeiten, einem Forschungsinstitut, das dazu beitragen sollte, eine industrielle Revolution in Taiwan herbeizuführen und die Lücke zwischen der entwickelten Wirtschaft und den Industrieländern zu schließen. Parallel zu seiner Arbeit bei ITRI gründete Chang 1987 TSMC, ein Unternehmen, das sich zum weltweit größten Hersteller von integrierten Schaltkreisen entwickelte. Das Geschäftsmodell von TSMC basierte ursprünglich auf der Tatsache, dass das Unternehmen nichts entwickelt, sondern nur die Entwicklungen anderer Menschen produziert. Dies war einer der ersten Schritte zur Schaffung eines modernen Ökosystems für die Entwicklung und Produktion von Mikroschaltungen, das als Fabless-Modell bekannt ist.

Das Ende des lyrischen ExkursesWas ist Fabless?

Fabless ist ein Modell für die Entwicklung und Produktion von Mikroschaltungen, bei denen das Entwicklerunternehmen keine eigene Produktion hat und die Dienste einer Drittfabrik nutzt, die auch mit anderen Entwicklern zusammenarbeitet (und manchmal über eigene Produkte verfügt).

Das Vorhandensein von Fabriken von Drittanbietern kann die Schwelle für den Eintritt in den Mikroelektronikmarkt (von der Morris Chang einmal geträumt hatte) von Hunderten auf Millionen Dollar drastisch senken, da keine Produktionsanlagen gekauft und gewartet werden müssen. Sie können diesen Schwellenwert auch noch weiter senken, da sich ein Markt für Anbieter komplexer Funktionsblöcke bildet (diese sind auch Silicon IP). Wenn Sie Chips in Ihrer eigenen Fabrik produzieren, können Sie sich nur auf Ihre eigenen Stärken verlassen und müssen ein Team haben, das alle erforderlichen Blöcke erstellen kann. Wenn die Fabrik nicht nur von Ihnen, sondern auch von anderen Unternehmen genutzt wird, hat bereits jemand die meisten typischen Aufgaben vor Ihnen gelöst, und Sie können die Ergebnisse der Arbeit eines anderen verwenden - oder Ihre eigene Lösung an einen anderen weiterverkaufen, nachdem Sie zuvor den Preis und die Bedingungen so vereinbart haben niemand blieb im Verlierer. Natürlich ist es unwahrscheinlich, dass Sie Ihr Know-how an direkte Wettbewerber verkaufen, aber es gibt viele Situationen, in denen Sie verdienen können, ohne in einen Interessenkonflikt verwickelt zu werden. Aus der Möglichkeit und dem Wunsch heraus, die Ergebnisse der Lösung typischer Probleme wiederzuverwenden, entstand der IP-Block-Markt, dessen Größe ab 2017 fast vier Milliarden Dollar betrug und weiterhin schnell wächst.

Wie ist es rentabel?

Käufer IP - vor allem sparen. Nach verschiedenen Schätzungen ist der Kauf von IP-Blöcken in der Regel zwei- bis fünfmal billiger als die Selbstentwicklung. Darüber hinaus können Sie durch den Kauf in der Regel die Entwicklungszeit erheblich verkürzen, da Sie keine eigenständigen Testchips erstellen und Fehler beheben müssen.

Für den IP-Entwickler - die Möglichkeit, ein funktionierendes Geschäft auf einer Nischenlösung aufzubauen und die Geschäftskosten erheblich zu senken. Ein wesentlicher Teil der Kosten für die Mikroschaltung sind die Kosten für Marketing, Verpackung, Test, technischen Support, Anwendungssoftware und schließlich Fotovorlagen für die Massenproduktion usw. usw. Wenn Sie keine fertigen Produkte herstellen, sondern nur Blöcke verkaufen, haben Sie nicht alle diese Kosten.

Fabrik - eine Gelegenheit, mehr Kunden anzulocken. Große Fabriken bemühen sich, ein Ökosystem von IP-Block-Lieferanten um sie herum zu schaffen, da ihre Verwendung das Design erheblich beschleunigen und, was ebenso wichtig ist, so weit wie möglich automatisieren kann. Ein reichhaltiges Portfolio an vorgefertigten Komponenten ist eine große Hilfe bei der Gestaltung des Endprodukts, da Sie nur Ihr eigenes Know-how selbst einsetzen und keine wertvollen Ressourcen für die Entwicklung von allem im Allgemeinen ausgeben können - insbesondere in einer Situation, in der bereits eine von Menschen entwickelte vorgefertigte Lösung vorhanden ist Wer hat in seine Entwicklung deutlich mehr Zeit und Erfahrung investiert, als Sie sich leisten können. Dementsprechend kann eine große Auswahl an vorgefertigten IPs ein schwerwiegender Faktor bei der Auswahl einer bestimmten Fabrik für die Produktion Ihres Projekts sein.

Wie funktioniert es

Betrachten wir die Lizenzierung von Kernen am Beispiel eines kugelförmigen benutzerdefinierten Systems auf einem Chip. Das System enthält einen Prozessorkern, Busse zum Kombinieren von Kern und Peripheriegeräten, eine bestimmte Menge an Cache-Speicher, Schnittstellen für die Kommunikation mit der Außenwelt (z. B. CAN und I2C), PLL, DAC und ADC. Nehmen wir für die Reinheit des Experiments an, dass alles ohne unabhängige Entwicklung überhaupt gekauft wird. "Dumme Annahme", sagen Sie, und Sie werden nicht ganz richtig sein. In der Realität sind solche Situationen natürlich äußerst selten, aber es ist durchaus möglich, sich vorzustellen, dass das Killer-Merkmal des Produkts kein Block an sich ist, sondern eine bestimmte Kombination vorhandener Blöcke. Sie sind beispielsweise der erste Käufer eines Blocks (daher haben Wettbewerber ihn noch nicht) oder Sie haben einen vorhandenen Block zur Verwendung in einem für ihn untypischen Segment entwickelt (daher haben Wettbewerber in diesem Segment nichts Ähnliches).

Beginnen wir also mit ...

... nein, nicht vom Prozessorkern, sondern von der analogen Bindung. Nehmen Sie zum Beispiel den Analog-Digital-Wandler (ADC) - eine typische Einheit der meisten Mikrocontroller und aller anderen Systeme, die Daten von außerhalb verarbeiten.

Der ADC ist ein analoger Block, was bedeutet, dass seine Parameter nicht nur stark von seiner Schaltung abhängen, sondern auch davon, wie genau diese Schaltung auf einem Chip implementiert ist. Wenn wir die fertige Datei mit der Topologie aus einem technischen Prozess nehmen und in einer anderen Fabrik mit denselben Konstruktionsstandards produzieren, können wir völlig andere Parameter erhalten (ganz zu schweigen von der Übertragung auf andere Konstruktionsstandards). Die seit der Mitte des Jahrhunderts bekannte Kultur der „Zweitlieferanten“ existiert jedoch immer noch. Beispielsweise bietet die Towerjazz-Fabrik Kopien einiger TSMC-Herstellungsprozesse an.

Der ADC ist ein hervorragendes Beispiel für einen Hard IP-Block, der an einen bestimmten Prozess gebunden ist. Um ein solches Gerät zu kaufen, müssen Sie genau wissen, auf welcher Technologie Ihr Endprodukt hergestellt wird. Wie oben erwähnt, kann die Verfügbarkeit des erforderlichen Hard IP einen ernsthaften Wettbewerbsvorteil für das Werk darstellen.

Wie wird Hard IP geliefert? Dies ist eine interessante Frage, und um sie zu beantworten, muss diskutiert werden, in welcher Form ein solcher Block entwickelt wird. Bei den meisten analogen Blöcken erfolgt die Entwicklung der Schaltung auf der Ebene einzelner Transistoren, dh die Ausgangsdateien sind die elektrische Schaltungsdatei und die Datei mit der Topologie. Darüber hinaus können die Merkmale sowohl des Schemas als auch der Topologie einen ernsthaften kommerziellen Wert haben, den ich natürlich nicht der Seite geben möchte. Und damit der Client das Schema nicht nach Topologie zurückentwickeln kann, wird die Topologie normalerweise auch nicht übertragen. Daher sehen die gelieferten Dateien im Normalfall folgendermaßen aus:

- Anstelle eines Stromkreises erhält der Client ein Verhaltensmodell auf hoher Ebene, das keine Implementierungsmerkmale offenbart. Ein solches Modell kann in Verilog-A geschrieben werden. Eine Alternative besteht darin, dass einige CAD-Systeme (z. B. Cadence Virtuoso) die Verschlüsselung elektrischer Schaltkreise unterstützen. Das heißt, der Client kann Ihren Schaltkreis (oder die Verilog-A-Datei) verwenden, den Inhalt jedoch nicht öffnen und anzeigen.

- Dimensionslayout der Topologie mit markierten externen Schlussfolgerungen und einer Beschreibung, wie viele Metallisierungsstufen ein Block einnimmt.

- Testumgebung zur Überprüfung der Hauptparameter.

- Dokumentation

In diesem Fall ist natürlich die Teilnahme eines Dritten erforderlich, auf den Sie die Topologie ohne Angst vor Wettbewerb und Reverse Engineering übertragen können. Diese dritte Partei ist die Fabrik, und ihre Vermittlerrolle zwischen Kunden und Auftragnehmern ist ein wichtiger Bestandteil des Ökosystems für die Entwicklung von Fabless-Chips. Die Fabrik sollte natürlich einen kristallklaren Ruf haben (hier geht es um Lesezeichen) und im Idealfall sollte sie selbst nichts Ähnliches produzieren, da die Arbeit in einer Fabrik eines konkurrierenden Unternehmens auf jeden Fall ein zweifelhaftes Vergnügen ist. Samsung ist es gelungen, Prozessoren gleichzeitig für sich und Apple zu produzieren, aber andere große Fabriken konzentrieren sich normalerweise entweder auf ihre eigene Produktion (wie Intel) oder geben die Selbstentwicklung (wie TSMC) vollständig auf. Der Wunsch, diesen Interessenkonflikt loszuwerden, war übrigens einer der Treiber für die Zuweisung von Globalfoundries (dem zweitgrößten Player auf dem Fabrikmarkt) von AMD.

Lyrischer ExkursÜbrigens gibt es in Russland keine reinen Fabriken in Russland. Darüber hinaus hat für absolut alle Marktteilnehmer die Herstellung eigener Produkte Priorität, und alle vollständig inländischen Chips, die von Fabless-Entwicklern hergestellt werden, werden in den Einrichtungen ihrer potenziellen Wettbewerber hergestellt - oder in reinen Fabriken im Ausland.

Das Ende des lyrischen ExkursesDarüber hinaus gibt es ein weiteres wichtiges Detail der Lieferanten-Fabrik-Interaktion: Die Fabrik gibt Ihren IP-Block in ihre eigene Datenbank ein und überprüft alle eingehenden Projekte auf das Vorhandensein Ihrer Topologie (die jemand von Ihnen sowie illegal erhalten könnte) Fragen Sie bei Ihnen nach, ob die Person, die die Produktion anfordert, eine Lizenz besitzt (da viele billige Lizenzen die Verwendung des Geräts in nur einem Projekt implizieren). Das Vorhandensein einer Überprüfung durch die Fabrik ermöglicht es dem Hard IP-Entwickler, eine geeignete Lizenzierungsoption zu wählen - abhängig von der Anzahl der Projekte, der Anzahl der verkauften Chips, dem Zeitpunkt des Starts der Chips in die Produktion usw. usw. Aber mehr über die Arten von Lizenzen im nächsten Teil.

Wie bei Hard IP in einem typischen System auf einem Chip benötigen Sie ADCs, PLL und physische Schichten von E / A-Schnittstellen.

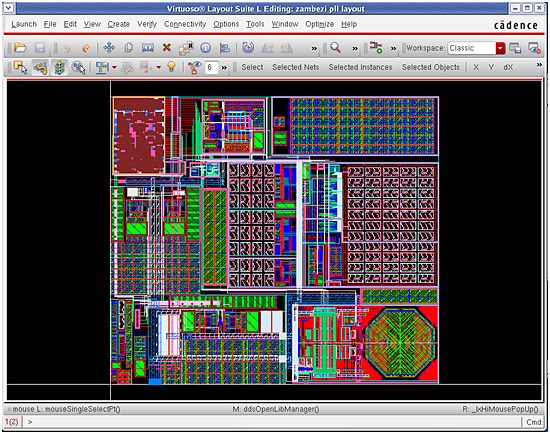

CAD-Fenster Cadence Virtuoso Layout Suite mit der Topologie des analogen Hard IP-Blocks (dies ist PLL, wenn jemand interessiert ist). Die Grenzen zwischen den einzelnen Untereinheiten (die normalerweise von verschiedenen Personen hergestellt werden) und beispielsweise einem für integrierte Schaltkreise sehr seltenen Element - dem Induktor in der unteren rechten Ecke - sind deutlich sichtbar. Und oben links befindet sich ein digitaler Block (wahrscheinlich Steuerung) und seine Multi-Bit-Schnittstelle zum Rest.

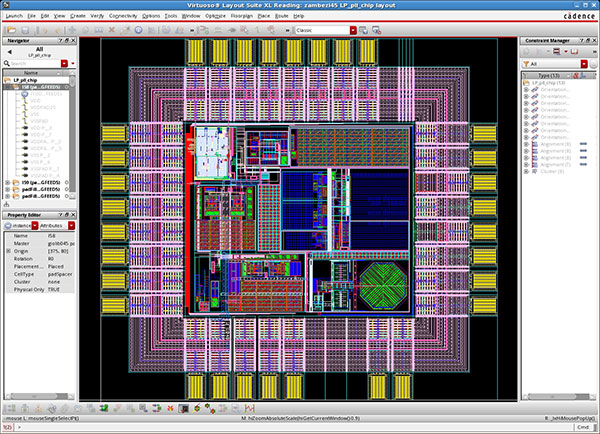

Es ist das gleiche, aber bereits in Form eines fertigen Chips (zum Beispiel zum Testen). E / A-Pads und die Ringe, die sie von den Ländern und Vorräten verbinden, sind deutlich sichtbar.

Der Begriff "Hard IP" wird auch in Bezug auf IP-Blöcke für FPGAs verwendet. In diesem Fall versteht es sich, dass der Blockcode für die Verwendung in einem bestimmten FPGA-Modell optimiert und für die Platzierung in diesem synthetisiert wurde.

Soft ip

Der nächste Block, den wir betrachten werden, ist der Prozessorkern. Tatsächlich kann fast jede digitale Schaltung an ihrer Stelle sein, beispielsweise eine Signalcodiereinheit mit einem Reed-Solomon-Code, aber Prozessorkerne sind am weitesten verbreitet und machen gut die Hälfte des gesamten Marktes aus (auch aufgrund der Komplexität und der hohen Kosten).

Der Hauptunterschied zwischen der Entwicklung digitaler und der Entwicklung analoger Schaltungen besteht darin, dass digitale Schaltungen normalerweise in speziellen Hochsprachen geschrieben werden - Verilog oder VHDL. Anschließend synthetisiert ein spezielles CAD-System die elektrische Schaltung und Topologie aus diesem Code. Bis zum Zeitpunkt der Synthese ist der Code also nicht an eine bestimmte Technologie gebunden, und derselbe Block kann in verschiedenen Fabriken (oder in das FPGA eingenäht) oder in verschiedenen Versionen derselben Technologie (z. B. optimiert für hohe Geschwindigkeit oder geringen Stromverbrauch) hergestellt werden. . Dies wird in der Tat von Entwicklungsunternehmen wie beispielsweise ARM verwendet. Solche digitalen Blöcke, die nicht an eine bestimmte Technologie gebunden sind, werden als Soft IP bezeichnet.

Hier ist das Schema eines Addiererbits:

Und so sieht ein 8-Bit-Addierer in einem Chip-Design tatsächlich aus:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

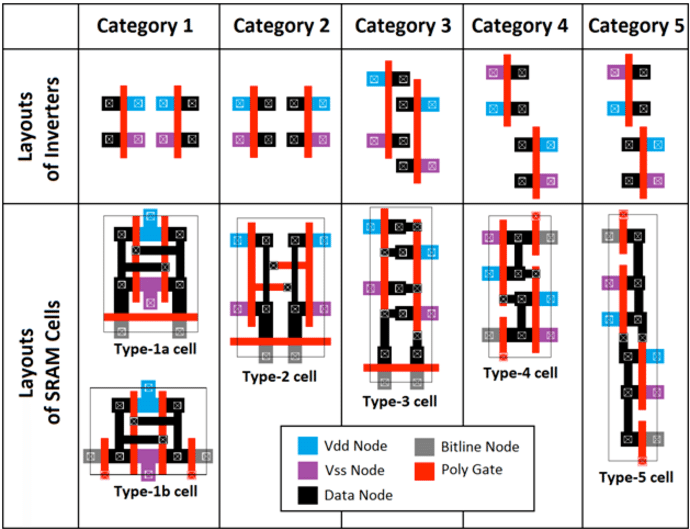

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .