Ich habe lange davon geträumt, den Umgang mit FPGA zu lernen, und habe genau hingeschaut. Dann kaufte er ein Debug-Board, schrieb ein paar Hallo-Welten und steckte das Board in eine Schachtel, weil nicht klar war, was er damit anfangen sollte. Dann kam die Idee: Schreiben wir einen Composite-Video-Generator für einen alten CRT-Fernseher. Die Idee ist natürlich lustig, aber ich kenne Verilog nicht wirklich und muss mich noch daran erinnern, und ich brauche diesen Generator nicht wirklich ... Und kürzlich wollte ich mich mit RISC-V- Softwareprozessoren befassen. Sie müssen irgendwo anfangen, und der Rocket-Chip- Code (dies ist eine der Implementierungen) ist in Chisel geschrieben - dies ist eine solche DSL für Scala. Dann erinnerte ich mich plötzlich daran, dass ich mich zwei Jahre lang professionell an der Scala entwickelt hatte und erkannte: Die Zeit war gekommen ...

Ich habe lange davon geträumt, den Umgang mit FPGA zu lernen, und habe genau hingeschaut. Dann kaufte er ein Debug-Board, schrieb ein paar Hallo-Welten und steckte das Board in eine Schachtel, weil nicht klar war, was er damit anfangen sollte. Dann kam die Idee: Schreiben wir einen Composite-Video-Generator für einen alten CRT-Fernseher. Die Idee ist natürlich lustig, aber ich kenne Verilog nicht wirklich und muss mich noch daran erinnern, und ich brauche diesen Generator nicht wirklich ... Und kürzlich wollte ich mich mit RISC-V- Softwareprozessoren befassen. Sie müssen irgendwo anfangen, und der Rocket-Chip- Code (dies ist eine der Implementierungen) ist in Chisel geschrieben - dies ist eine solche DSL für Scala. Dann erinnerte ich mich plötzlich daran, dass ich mich zwei Jahre lang professionell an der Scala entwickelt hatte und erkannte: Die Zeit war gekommen ...

Wenn Sie also eine Geschichte aus dem Leben von Drahtschneidern, einem Digitalmultimeter und einem Oszilloskop lesen möchten, das sich selbst verwirklicht hat, dann sind Sie bei cat willkommen.

Was wird in diesem Artikel stehen? Darin werde ich meine Versuche beschreiben, ein zusammengesetztes PAL-Videosignal (warum PAL? - Ich habe gerade ein gutes Tutorial speziell zur PAL-Generierung gefunden) auf dem Mars Rover 2- Board von nckma zu generieren . Über RISC-V in diesem Artikel werde ich überhaupt nichts sagen. :) :)

Zunächst ein wenig zu Scala und Chisel: Scala ist eine Sprache, die auf der Java Virtual Machine ausgeführt wird und vorhandene Java-Bibliotheken transparent verwendet (obwohl es auch Scala.js und Scala Native gibt). Als ich anfing, es zu studieren, hatte ich das Gefühl, dass es eine sehr brauchbare Mischung aus „Pluspunkten“ und Haskell ist (Kollegen teilen diese Meinung jedoch nicht) - es ist ein schmerzlich fortschrittliches Typensystem und eine prägnante Sprache, aber wegen der Notwendigkeit, den Funktionalismus zu kreuzen OOP eine Fülle von Sprachkonstrukten an einigen Stellen weckte Erinnerungen an C ++. Haben Sie jedoch keine Angst vor Scala - es ist eine sehr prägnante und sichere Sprache mit einem leistungsstarken Typsystem, in dem Sie zunächst einfach als verbessertes Java schreiben können. Soweit ich weiß, wurde Scala ursprünglich als Sprache für die bequeme Erstellung domänenspezifischer Sprachen entwickelt. In diesem Fall beschreiben Sie beispielsweise digitale Geräte oder Notizen in einer formalen Sprache, und diese Sprache sieht aus Sicht des Themenbereichs recht logisch aus. Und dann stellt man plötzlich fest, dass es der richtige Code in Scala (na ja, oder Haskell) war - nur freundliche Leute haben eine Bibliothek mit einer praktischen Oberfläche geschrieben. Chisel ist eine solche Bibliothek für Scala, mit der wir die digitale Logik in einem praktischen DSL beschreiben und dann den resultierenden Scala-Code ausführen und Code auf Verilog (oder etwas anderem) generieren können, der in das Quartus-Projekt kopiert werden kann. Führen Sie sofort die Standard-Unit-Tests im Scala-Stil aus, die selbst Testbenches simulieren und einen Bericht über die Ergebnisse erstellen.

Um mich mit digitalen Schaltkreisen vertraut zu machen, empfehle ich dieses Buch (es ist bereits in der gedruckten russischen Version). Tatsächlich endet meine systematische Bekanntschaft mit der FPGA-Welt fast mit diesem Buch, so dass konstruktive Kritik in den Kommentaren willkommen ist (ich wiederhole jedoch, das Buch ist wunderbar: Es erzählt von den Grundlagen bis zur Schaffung eines einfachen übermittelten Prozessors. Und es gibt dort Bilder;)). Nun, laut Chisel gibt es ein gutes offizielles Tutorial .

Haftungsausschluss: Der Autor ist nicht für die verbrannten Geräte verantwortlich. Wenn Sie das Experiment wiederholen möchten, ist es besser, die Signalpegel mit einem Oszilloskop zu überprüfen, den analogen Teil neu zu erstellen usw. Und im Allgemeinen - Sicherheitsvorkehrungen beachten. (Als ich zum Beispiel den Artikel schrieb, stellte ich fest, dass die Beine auch Gliedmaßen sind und es nichts gibt, was sie in die Zentralheizungsbatterie stecken und am Ausgang der Platine festhalten könnte ...) Übrigens verursachte diese Infektion auch Störungen im Fernseher im Nebenzimmer im Zuge des Debuggens ...

Projekteinrichtung

Wir werden den Code in IntelliJ Idea Community Edition schreiben, sbt wird das Build-System sein, also erstellen Sie ein Verzeichnis, setzen Sie .gitignore , project/build.properties , project/plugins.sbt von hier und

etwas vereinfacht build.sbt def scalacOptionsVersion(scalaVersion: String): Seq[String] = { Seq() ++ {

Öffnen Sie es nun in der Idee und fordern Sie den Import des sbt-Projekts an - während sbt die erforderlichen Abhängigkeiten herunterlädt.

Erste Module

PWM

Versuchen wir zunächst, eine einfache PWM zu schreiben. Meine Logik war ungefähr die folgende: Um ein Tastverhältnis-Signal n / m zu erzeugen, setzen wir zunächst 0 in das Register und fügen es bei jedem Schritt n hinzu. Wenn der Wert des Registers m überschreitet, subtrahieren Sie m und geben Sie für einen Taktzyklus einen hohen Pegel aus. Eigentlich wird es fehlerhaft sein, wenn n> m ist, aber wir werden dies als unbestimmtes Verhalten betrachten, das erforderlich ist, um die tatsächlich verwendeten Fälle zu optimieren.

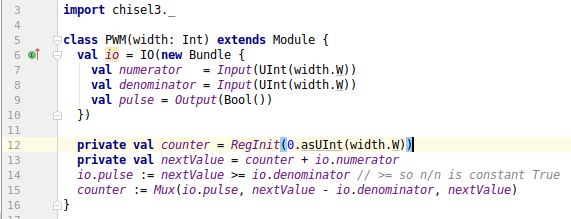

Ich werde nicht den gesamten Anfängerleitfaden nacherzählen - er liest in einer halben Stunde, ich werde nur sagen, dass wir zur Beschreibung des Moduls chisel3._ importieren und von der abstrakten Klasse Module erben müssen. Es ist abstrakt, weil wir das Bundle unter dem Namen io - es wird die gesamte Schnittstelle des Moduls haben. Gleichzeitig werden die clock und reset Eingänge implizit angezeigt - Sie müssen sie nicht separat beschreiben. Folgendes ist passiert:

import chisel3._ class PWM(width: Int) extends Module { val io = IO(new Bundle { val numerator = Input(UInt(width.W)) val denominator = Input(UInt(width.W)) val pulse = Output(Bool()) }) private val counter = RegInit(0.asUInt(width.W)) private val nextValue = counter + io.numerator io.pulse := nextValue > io.denominator counter := Mux(io.pulse, nextValue - io.denominator, nextValue) }

Beachten Sie, dass wir die .W Methode .W einem regulären int aufrufen, um die .W zu erhalten, und die .asUInt(width.W) -Methode, die wir im Allgemeinen auf einem Integer-Literal aufrufen! Wie ist das möglich? - Nun, in Smalltalk würden wir nur eine neue Methode für die Integer-Klasse definieren (oder wie auch immer sie dort heißt), aber in der JVM haben wir immer noch nicht das gesamte Objekt - es gibt auch primitive Typen, und Scala versteht dies (und zusätzlich) Es gibt Klassen von Drittanbietern, die wir nicht ändern können. Daher gibt es eine Vielzahl von impliziten s: In diesem Fall findet Scala wahrscheinlich so etwas

implicit class BetterInt(n: Int) { def W: Width = ... }

im gegenwärtigen Umfang haben also gewöhnliche Ints Superkräfte. Hier ist eine der Funktionen, die Scala übersichtlicher und einfacher macht, DSL zu erstellen.

Fügen Sie eine Prise Tests hinzu. import chisel3.iotesters._ import org.scalatest.{FlatSpec, Matchers} object PWMSpec { class PWMTesterConstant(pwm: PWM, denum: Int, const: Boolean) extends PeekPokeTester(pwm) { poke(pwm.io.numerator, if (const) denum else 0) poke(pwm.io.denominator, denum) for (i <- 1 to 2 * denum) { step(1) expect(pwm.io.pulse, const) } } class PWMTesterExact(pwm: PWM, num: Int, ratio: Int) extends PeekPokeTester(pwm) { poke(pwm.io.numerator, num) poke(pwm.io.denominator, num * ratio) val delay = (1 to ratio + 2).takeWhile { _ => step(1) peek(pwm.io.pulse) == BigInt(0) } println(s"delay = $delay") for (i <- 1 to 10) { expect(pwm.io.pulse, true) for (j <- 1 to ratio - 1) { step(1) expect(pwm.io.pulse, false) } step(1) } } class PWMTesterApproximate(pwm: PWM, num: Int, denom: Int) extends PeekPokeTester(pwm){ poke(pwm.io.numerator, num) poke(pwm.io.denominator, denom) val count = (1 to 100 * denom).map { _ => step(1) peek(pwm.io.pulse).toInt }.sum val diff = count - 100 * num println(s"Difference = $diff") expect(Math.abs(diff) < 3, "Difference should be almost 0") } } class PWMSpec extends FlatSpec with Matchers { import PWMSpec._ behavior of "PWMSpec" def testWith(testerConstructor: PWM => PeekPokeTester[PWM]): Unit = { chisel3.iotesters.Driver(() => new PWM(4))(testerConstructor) shouldBe true } it should "return True constant for 1/1" in { testWith(new PWMTesterConstant(_, 1, true)) } it should "return True constant for 10/10" in { testWith(new PWMTesterConstant(_, 10, true)) } it should "return False constant for 1/1" in { testWith(new PWMTesterConstant(_, 1, false)) } it should "return False constant for 10/10" in { testWith(new PWMTesterConstant(_, 10, false)) } it should "return True exactly once in 3 steps for 1/3" in { testWith(new PWMTesterExact(_, 1, 3)) } it should "return good approximation for 3/10" in { testWith(new PWMTesterApproximate(_, 3, 10)) } }

PeekPokeTester ist einer von drei Standardtestern in Chisel. Hier können Sie die Werte an den Eingängen des Prüflings (Prüfling) einstellen und die Werte an den Ausgängen überprüfen. Wie wir sehen können, wird der übliche ScalaTest für Tests verwendet und die Tests belegen das Fünffache der Implementierung selbst, was im Prinzip für Software normal ist. Ich vermute jedoch, dass erfahrene Entwickler von Geräten, die "in Silizium gegossen" sind, nur mit einer solchen mikroskopischen Anzahl von Tests lächeln werden. Launch und oops ...

Circuit state created [info] [0,000] SEED 1529827417539 [info] [0,000] EXPECT AT 1 io_pulse got 0 expected 1 FAIL ... [info] PWMSpec: [info] PWMSpec [info] - should return True constant for 1/1 [info] - should return True constant for 10/10 *** FAILED *** [info] false was not equal to true (PWMSpec.scala:56) [info] - should return False constant for 1/1 [info] - should return False constant for 10/10 [info] - should return True exactly once in 3 steps for 1/3 [info] - should return good approximation for 3/10

Ja, beheben Sie es in PWM in der Zeile io.pulse := nextValue > io.denominator anmelden >= , starten Sie die Tests neu - alles funktioniert! Ich befürchte, dass erfahrene Entwickler digitaler Geräte mich wegen einer so leichtfertigen Einstellung zum Design umbringen wollen (und einige Softwareentwickler werden sich ihnen gerne anschließen) ...

Impulsgeber

Wir werden auch einen Generator benötigen, der Synchronisationsimpulse für "Halbbilder" ausgibt. Warum halb? weil zuerst die ungeraden Linien übertragen werden, dann die geraden (na ja oder umgekehrt, aber jetzt ist uns Fett egal).

import chisel3._ import chisel3.util._ class OneShotPulseGenerator(val lengths: Seq[Int], val initial: Boolean) extends Module {

Wenn das reset entfernt wird, schießt es mit Rechteckimpulsen mit den Längen der Intervalle zwischen den Schaltvorgängen, die durch den lengths angegeben werden. lengths bleibt es für immer im letzten Zustand. Dieses Beispiel zeigt die Verwendung von Wertetabellen mit VecInit sowie eine Möglichkeit, die erforderliche Registerbreite chisel3.util.log2Ceil(maxVal + 1).W : chisel3.util.log2Ceil(maxVal + 1).W . Ich kann mich ehrlich gesagt nicht erinnern, wie es in Verilog gemacht wurde, aber in Chisel reicht es aus, den Konstruktor der Klasse mit dem erforderlichen Parameter aufzurufen, um ein solches Modul zu erstellen, das durch einen Wertevektor parametrisiert wird.

Sie fragen wahrscheinlich: "Wenn die clock und reset Eingänge implizit generiert werden, wie werden wir dann den Impulsgenerator für jeden Frame" aufladen "?" Meißelentwickler haben für alles gesorgt:

val module = Module( new MyModule() ) val moduleWithCustomReset = withReset(customReset) { Module( new MyModule() ) } val otherClockDomain = withClock(otherClock) { Module( new MyModule() ) }

Naive Implementierung eines Signalgenerators

Damit der Fernseher uns zumindest irgendwie versteht, müssen Sie das „Protokoll“ des durchschnittlichen Trickpegels unterstützen: Es gibt drei wichtige Signalpegel:

- 1,0 V - weiße Farbe

- 0,3 V - schwarze Farbe

- 0V - Sonderpegel

Warum habe ich 0V Special angerufen? Denn mit einem reibungslosen Übergang von 0,3 V auf 1,0 V wechseln wir reibungslos von Schwarz nach Weiß und zwischen 0 V und 0,3 V, soweit ich verstehen kann, gibt es keine Zwischenpegel und 0 V wird nur für die Synchronisation verwendet. (Tatsächlich ändert es sich nicht einmal im Bereich von 0 V - 1 V, sondern von -0,3 V - 0,7 V, aber hoffentlich befindet sich noch ein Kondensator am Eingang.)

Wie dieser wunderbare Artikel lehrt, besteht ein zusammengesetztes PAL-Signal aus einem endlosen Strom sich wiederholender 625 Zeilen: Die meisten davon sind Zeilen, tatsächlich Bilder (getrennt gerade und getrennt ungerade), einige werden für Synchronisationszwecke verwendet (wir haben den Generator für sie erstellt Signale), einige sind auf dem Bildschirm nicht sichtbar. Sie sehen so aus (ich werde keine Piraterie betreiben und Links zum Original geben):

Versuchen wir, die Schnittstellen der Module zu beschreiben:

BWGenerator verwaltet die Timings usw. und muss wissen, mit welcher Häufigkeit es funktioniert:

class BWGenerator(clocksPerUs: Int) extends Module { val io = IO(new Bundle { val L = Input(UInt(8.W)) val x = Output(UInt(10.W)) val y = Output(UInt(10.W)) val inScanLine = Output(Bool()) val millivolts = Output(UInt(12.W)) })

PalColorCalculator berechnet den Pegel des Luminanzsignals sowie ein zusätzliches Farbsignal:

class PalColorCalculator extends Module { val io = IO(new Bundle { val red = Input(UInt(8.W)) val green = Input(UInt(8.W)) val blue = Input(UInt(8.W)) val scanLine = Input(Bool()) val L = Output(UInt(8.W)) val millivolts = Output(UInt(12.W)) })

Im PalGenerator Modul verbinden PalGenerator einfach PalGenerator beiden angegebenen Module erneut:

class PalGenerator(clocksPerUs: Int) extends Module { val io = IO(new Bundle { val red = Input(UInt(8.W)) val green = Input(UInt(8.W)) val blue = Input(UInt(8.W)) val x = Output(UInt(10.W)) val y = Output(UInt(10.W)) val millivolts = Output(UInt(12.W)) }) val bw = Module(new BWGenerator(clocksPerUs)) val color = Module(new PalColorCalculator) io.red <> color.io.red io.green <> color.io.green io.blue <> color.io.blue bw.io.L <> color.io.L bw.io.inScanLine <> color.io.scanLine bw.io.x <> io.x bw.io.y <> io.y io.millivolts := bw.io.millivolts + color.io.millivolts }

Und jetzt zeichnen wir leider die erste Eule ... package io.github.atrosinenko.fpga.tv import chisel3._ import chisel3.core.withReset import io.github.atrosinenko.fpga.common.OneShotPulseGenerator object BWGenerator { val ScanLineHSyncStartUs = 4.0 val ScanLineHSyncEndUs = 12.0 val TotalScanLineLengthUs = 64.0 val VSyncStart = Seq( 2, 30, 2, 30,

Generierung von synthetisiertem Code

Das ist alles gut, aber wir wollen das resultierende Design in eine Tafel nähen. Dazu müssen Sie Verilog synthetisieren. Dies geschieht auf sehr einfache Weise:

import chisel3._ import io.github.atrosinenko.fpga.common.PWM object Codegen { class TestModule(mhz: Int) extends Module { val io = IO(new Bundle { val millivolts = Output(UInt(12.W)) }) val imageGenerator = Module(new TestColorImageGenerator(540, 400)) val encoder = Module(new PalGenerator(clocksPerUs = mhz)) imageGenerator.io.x <> encoder.io.x imageGenerator.io.y <> encoder.io.y imageGenerator.io.red <> encoder.io.red imageGenerator.io.green <> encoder.io.green imageGenerator.io.blue <> encoder.io.blue io.millivolts := encoder.io.millivolts override def desiredName: String = "CompositeSignalGenerator" } def main(args: Array[String]): Unit = { Driver.execute(args, () => new PWM(12)) Driver.execute(args, () => new TestModule(mhz = 32)) } }

Tatsächlich machen wir es in der zweizeiligen Methode main() zweimal, der Rest des Codes ist ein weiteres Modul, das als nächstes bleibt

Absolut langweiliger Testbildgenerator class TestColorImageGenerator(width: Int, height: Int) extends Module { val io = IO(new Bundle { val red = Output(UInt(8.W)) val green = Output(UInt(8.W)) val blue = Output(UInt(8.W)) val x = Input(UInt(10.W)) val y = Input(UInt(10.W)) }) io.red := Mux((io.x / 32.asUInt + io.y / 32.asUInt)(0), 200.asUInt, 0.asUInt) io.green := Mux((io.x / 32.asUInt + io.y / 32.asUInt)(0), 200.asUInt, 0.asUInt) io.blue := Mux((io.x / 32.asUInt + io.y / 32.asUInt)(0), 0.asUInt, 0.asUInt) }

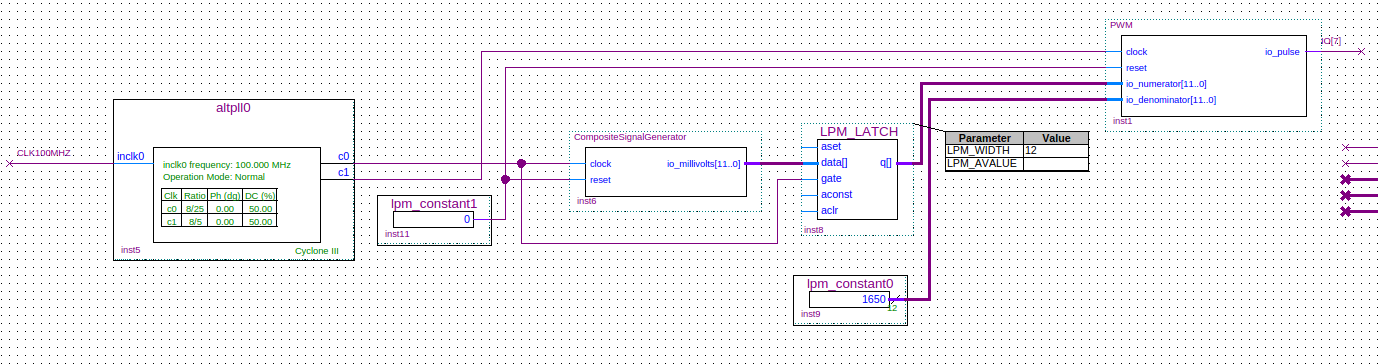

Jetzt müssen Sie es in das Quartus-Projekt verschieben. Für Mars Rover 2 benötigen wir die kostenlose Version von Quartus 13.1. Wie man es installiert, steht auf der Seite der Marsrover. Von dort habe ich das "Erste Projekt" für das Mars Rover 2-Board heruntergeladen, es in das Repository gestellt und ein wenig korrigiert. Da ich kein Elektronikingenieur bin (und FPGA interessiere ich mich eigentlich mehr für Beschleuniger als für Schnittstellenkarten)

wie in diesem Witz ...Der Programmierer sitzt tief im Debuggen.

Fit Sohn:

"Papa, warum geht die Sonne jeden Tag im Osten auf und sitzt im Westen?"

"Hast du das überprüft?"

- Geprüft.

- Gut geprüft?

- Gut.

- Funktioniert es?

- Es funktioniert.

- Funktioniert es jeden Tag?

- Ja, jeden Tag.

- Um Gottes willen, mein Sohn, berühre nichts, ändere nichts.

... Ich habe gerade den VGA-Signalgenerator gelöscht und mein Modul hinzugefügt.

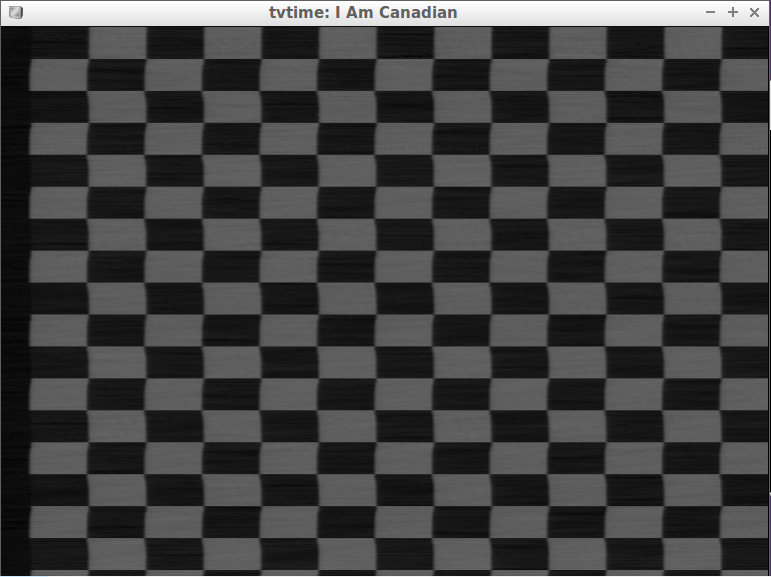

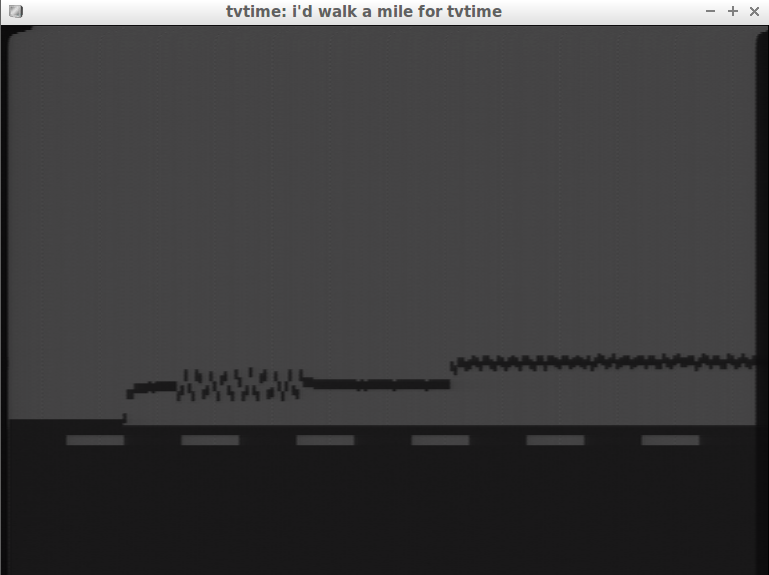

Danach habe ich den analogen TV-Tuner an einen anderen Computer (Laptop) angeschlossen, so dass zwischen der Stromversorgung des Signalgenerators und des Verbrauchers zumindest eine gewisse galvanische Trennung bestand, und nur ein Signal von den Pins IO7 (+) und GND (-) der Karte an den Composite-Eingang (Minus) gesendet zum externen Kontakt sowie zur Mitte). Nun, das heißt, als "einfach" ... Es wäre einfach, wenn die Hände von dort wachsen würden, wo sie sollten, na ja, oder wenn ich weiblich-männliche Verbindungsdrähte hätte. Aber ich habe nur ein paar männlich-männliche Drähte. Aber ich habe Hartnäckigkeit und Zangen! Im Allgemeinen gibt es einen Draht der Verstopfung, ich habe mir zwei beinahe Arbeiter gemacht - mit Schwierigkeiten, aber am Brett festhaltend. Und hier ist was ich gesehen habe:

Tatsächlich habe ich dich natürlich ein wenig getäuscht. Den oben gezeigten Code habe ich nach ungefähr drei Stunden Debuggen "auf Hardware" erhalten, aber verdammt, ich habe ihn geschrieben und er funktioniert !!! Und da ich mit seriöser Elektronik früher fast nicht vertraut war, denke ich, dass die Aufgabe nicht schrecklich war, was für eine schwierige Aufgabe.

Erzeugung von Farbvideos

Nun, dann bleibt die Sache für kleine - einen Farbvideosignalgenerator hinzuzufügen. Ich nahm das Tutorial und begann zu versuchen, einen Farbburst (der für kurze Zeit während der HSync-Erzeugung zum Schwarzpegel der Sinuswelle bei der Trägerfrequenz des Farbsignals addiert wird) und tatsächlich das Farbsignal gemäß der Formel zu bilden. Aber es kommt nicht heraus, selbst wenn Sie knacken ... Irgendwann wurde mir klar, dass der Fernseher trotz der Tatsache, dass mir die Frequenz bei einem kurzen Blick auf das Dokument nicht auffiel, kaum auf eine willkürliche Einstellung eingestellt war. Nach der Suche stellte ich fest, dass der PAL eine Trägerfrequenz von 4,43 MHz verwendet. Das Ding ist der Hut, dachte ich. "Fick dich", antwortete der Tuner. Nach einem ganzen Tag des Debuggens und nur einmalem Erkennen von Farben auf dem Bild (außerdem, als ich dem Tuner sagte, dass es im Allgemeinen NTSC war)

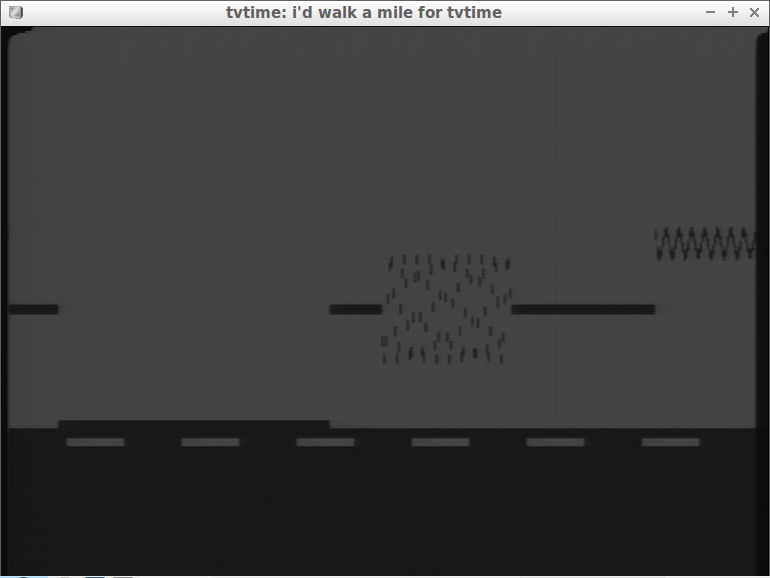

... Mir wurde klar, wie Hoffnungslosigkeit wirklich aussieht Dann wurde mir klar, dass ich ohne ein Oszilloskop nicht auskommen kann. Und wie ich bereits sagte, bin ich mit Elektronik nicht vertraut, und natürlich habe ich zu Hause kein solches Wunder der Technologie. Zu kaufen? Ein bisschen teuer für ein Experiment ... Und woraus kann es auf dem Knie aufgebaut werden? Ein Signal an den Line-Eingang der Soundkarte anschließen? Ja, viereinhalb Megahertz - es ist unwahrscheinlich, dass er startet (zumindest ohne Änderung). Hmm, der Mars Rover hat einen ADC bei 20 MHz, aber es reicht nicht aus, einen Rohstrom der Geschwindigkeit der seriellen Schnittstelle auf den Computer zu übertragen. Nun, irgendwo müssen Sie das Signal für die Anzeige noch verarbeiten, und tatsächlich wird es eine akzeptable Menge an Informationsbits geben, aber es geht auch darum, mit der seriellen Schnittstelle herumzuspielen, Programme für den Computer zu schreiben ... Dann dachte ich, dass der Ingenieur entwickeln sollte Es gibt eine gesunde Hartnäckigkeit an sich: Es gibt einen Farb-Imager im Leerlauf, einen ADC ... Aber das Schwarzweißbild wird stabil ausgegeben ... Nun, lassen Sie den Signalgenerator sich selbst debuggen!

Lyrischer Exkurs (wie sie sagen: „Die Meinung des Schülers muss nicht mit der Meinung des Lehrers, des gesunden Menschenverstandes und der Axiomatik von Peano übereinstimmen“): Als ich die Farbgenerierung mit allen Arten von Multiplikationen und anderen komplizierten Dingen hinzufügte, sackte Fmax für den Signalaufbereiter stark zusammen. Was ist Fmax? Soweit ich aus dem Harris & Harris-Lehrbuch verstanden habe, bevorzugt CAD für FPGA, wenn Verilog nicht wie im Standard geschrieben wird, sondern "nach Konzepten": Das Ergebnis sollte beispielsweise eine Synchronschaltung sein - eine Art direktionales azyklisches Netz aus kombinatorischer Logik (Addition, Multiplikation) , Division, logische Operationen, ...), die mit ihren Ein- und Ausgängen an den Ausgängen bzw. Eingängen von Triggern hängen bleiben. Ein Trigger an der Flanke des Taktsignals speichert den Wert seines Eingangs für den gesamten nächsten Taktzyklus, dessen Pegel einige Zeit vor der Front und einige Zeit danach stabil sein muss (dies sind zwei Zeitkonstanten). Die Signale von den Ausgängen der Trigger laufen wiederum nach dem Beginn des Taktsignals zu den Ausgängen der Kombinationslogik (und damit zu den Eingängen anderer Trigger. Nun, und den Ausgängen der Mikroschaltung), die ebenfalls durch zwei Intervalle gekennzeichnet sind: die Zeit, in der noch kein Ausgang vorhanden ist Sie haben Zeit, sich zu ändern, und die Zeit, nach der sich die Änderungen beruhigen (vorausgesetzt, die Eingabe hat sich einmal geändert). Hier ist die maximale Frequenz, mit der die Kombinationslogik sicherstellt, dass die Anforderungen der Trigger erfüllt werden - und dies ist Fmax. Wenn die Schaltung zwischen zwei Takten Zeit haben sollte, mehr zu zählen, nimmt Fmax ab. Natürlich möchte ich, dass die Frequenz größer ist, aber wenn sie plötzlich zehnmal sprang (oder sogar die Anzahl der Frequenzbereiche im CAD-Bericht abnahm) - überprüfen Sie, ob Sie irgendwo etwas durcheinander gebracht haben, und als Ergebnis fand CAD einen konstanten Ausdruck und gerne zur Optimierung genutzt.

Oszilloskop-Förderung

Nein, nicht der, nach dem das Oszilloskop und eine Handvoll zusätzlicher Teile gedreht werden, aber das Oszilloskop-Bootstrapping ist wie das Compiler-Bootstrapping, nur für das Oszilloskop.

Wir werden auf Befehl ein Oszilloskop herstellen, das einige Abtastwerte des Eingangssignals aufzeichnet und danach nur das aufgezeichnete anzeigt. Da er irgendwie einen Befehl zum Aufzeichnen geben muss und danach - durch ihn navigieren, werden wir einige Tastencontroller benötigen - schrieb ich nicht sehr praktisch, aber ziemlich primitiv, hier ist es:

class SimpleButtonController( clickThreshold: Int, pressThreshold: Int, period: Int, pressedIsHigh: Boolean ) extends Module { val io = IO(new Bundle { val buttonInput = Input(Bool()) val click = Output(Bool()) val longPress = Output(Bool()) })

SCHOCK! SENSATION! Damit es funktioniert, müssen Sie nur ... private val cycleCounter = RegInit(0.asUInt(32.W)) private val pressedCounter = RegInit(0.asUInt(32.W)) io.click := false.B io.longPress := false.B when (cycleCounter === 0.asUInt) { when (pressedCounter >= pressThreshold.asUInt) { io.longPress := true.B }.elsewhen (pressedCounter >= clickThreshold.asUInt) { io.click := true.B } cycleCounter := period.asUInt pressedCounter := 0.asUInt } otherwise { cycleCounter := cycleCounter - 1.asUInt when (io.buttonInput === pressedIsHigh.B) { pressedCounter := pressedCounter + 1.asUInt } } }

:

class Oscilloscope( clocksPerUs: Int, inputWidth: Int, windowPixelWidth: Int, windowPixelHeight: Int ) extends Module { val io = IO(new Bundle { val signal = Input(UInt(inputWidth.W)) val visualOffset = Input(UInt(16.W)) val start = Input(Bool()) val x = Input(UInt(10.W)) val y = Input(UInt(10.W)) val output = Output(Bool()) }) private val mem = SyncReadMem(1 << 15, UInt(inputWidth.W)) private val physicalPixel = RegInit(0.asUInt(32.W)) when (io.start) { physicalPixel := 0.asUInt } when (physicalPixel < mem.length.asUInt) { mem.write(physicalPixel, io.signal) physicalPixel := physicalPixel + 1.asUInt } private val shiftedX = io.x + io.visualOffset private val currentValue = RegInit(0.asUInt(inputWidth.W)) currentValue := ((1 << inputWidth) - 1).asUInt - mem.read( Mux(shiftedX < mem.length.asUInt, shiftedX, (mem.length - 1).asUInt) ) when (io.x > windowPixelWidth.asUInt || io.y > windowPixelHeight.asUInt) {

— , :

class OscilloscopeController( visibleWidth: Int, createButtonController: () => SimpleButtonController ) extends Module { val io = IO(new Bundle { val button1 = Input(Bool()) val button2 = Input(Bool()) val visibleOffset = Output(UInt(16.W)) val start = Output(Bool()) val leds = Output(UInt(4.W)) }) val controller1 = Module(createButtonController()) val controller2 = Module(createButtonController()) controller1.io.buttonInput <> io.button1 controller2.io.buttonInput <> io.button2 private val offset = RegInit(0.asUInt(16.W)) private val leds = RegInit(0.asUInt(4.W)) io.start := false.B when (controller1.io.longPress && controller2.io.longPress) { offset := 0.asUInt io.start := true.B leds := leds + 1.asUInt }.elsewhen (controller1.io.click) { offset := offset + (visibleWidth / 10).asUInt }.elsewhen (controller2.io.click) { offset := offset - (visibleWidth / 10).asUInt }.elsewhen (controller1.io.longPress) { offset := offset + visibleWidth.asUInt }.elsewhen (controller2.io.longPress) { offset := offset - visibleWidth.asUInt } io.visibleOffset := offset io.leds := leds }

(, ), - : — , — , ( — ). — ! , Verilog ?..

- , FPGA:

— ( IO7, VGA_GREEN R-2R ) :

, — , , . PAL — "Picture At Last (-, !)"

GitHub .

Schlussfolgerungen

Scala + Chisel — , Higher-kinded types. Scala- , Chisel , . . — !

: " -?" — ! ...