Letzte Woche gab Intel die Übernahme von eASIC bekannt, das FPGA-basierte Entwicklungstools für „strukturelle ASICs“ entwickelt. Strukturelle ASICs sind eine Kreuzung zwischen herkömmlichen FPGAs und herkömmlichen ASICs. Mit ihnen können Sie die Zeit für die Vermarktung des Produkts verkürzen und die Kosten senken.

Intel verwendet die eASIC-Technologie

seit 2015 in benutzerdefinierten Versionen von Xeon-Prozessoren. eASIC (120 Personen) wird nun Teil der Intel Programmable Solutions Group (PSG).

Selbst diejenigen, die sich vor langer Zeit mit FPGA und ASIC „angefreundet“ haben, werden sich nicht weigern, zu erklären, was „strukturelle ASICs“ sind. Die Rechenleistung des Computers ist nicht auf die CPU oder GPU beschränkt, es gibt andere Prozessorklassen, wie zum Beispiel FPGA - sie werden von Altera entwickelt und von Intel erworben. In FPGAs können Millionen von Gates flexibel programmiert werden, um die erforderliche Funktionalität zu implementieren. Tatsächlich werden die meisten CPUs und GPUs zunächst auf FPGAs simuliert, um die Leistung zu testen. FPGAs sind eine einfache Möglichkeit, Verbindungsschaltungen zu modellieren, und ihr Anwendungsbereich ist breit. FPGAs können auch handelsübliche Hardwareeinheiten wie ARM-Kerne oder Transceiver für die externe Kommunikation enthalten.

Ein weiteres Beispiel ist ASIC (Application Specific Integrated Circuit), ein Chip, der zur Ausführung genau definierter Aufgaben entwickelt wurde. ASIC ist maximal für seine Aufgaben optimiert und die Logik seiner Arbeit kann nicht geändert werden. Oft werden CPU und GPU als ASICs in dem Sinne klassifiziert, dass ihre Mikroarchitektur ebenfalls festgelegt ist. Sie dienen jedoch der Lösung verschiedener Probleme und sind universell, während ASICs für klar definierte Arten von Berechnungen erstellt werden. Merkmale von ASIC: Sie sind schnell, wirtschaftlich, aber relativ teuer und schwer herzustellen.

Die strukturellen ASICs von EASIC können als halbherzige Lösung bezeichnet werden. Ingenieure erstellen einen Prototyp mit FPGA, verschwenden jedoch keine Zeit mit der Optimierung seiner Schaltkreise, sondern stellen einen Chip mit einer festen Architektur auf seiner Basis her. Aus diesem Grund arbeitet es schneller als ein Beispiel mit benutzerdefinierten Blöcken, obwohl es die Vorteile der Energieeffizienz verliert. Die Zeit für die Entwicklung ist jedoch vergleichbar mit FPGA, nicht mit ASIC - es spart bis zu 6 Monate. Der Beitrag von eASIC besteht darin, dass die Single-Layer-Layer-Optimierung verwendet wird, um das SRAM-Routing durch End-to-End zu ersetzen, wodurch die Produktionskosten erheblich gesenkt werden. eASIC bietet auch feste Zellbibliotheken, auch einschichtig, was den Verbrauch, die Kristallgröße und die Markteinführungszeit weiter reduziert. Außerdem können Entwickler die Standardverfahren beim Erstellen von ASICs überspringen, z. B. Ausgleichssynchronisation, Signalintegritätsanalyse, Leistungsdämpfungstest und andere. Daher können "strukturelle ASICs" als FPGAs beschrieben werden, die nicht mehr programmiert werden können und die die besten Eigenschaften sowohl von FPGAs als auch von ASICs aufweisen.

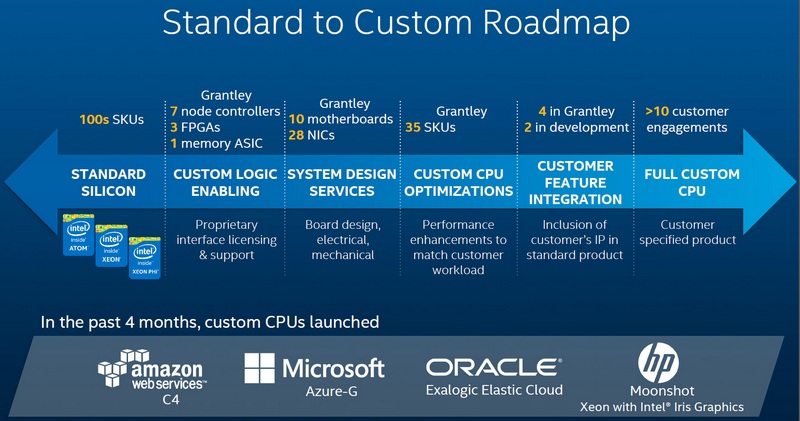

Die Grafik zeigt den aktuellen Stand und die Aussichten im Bereich der kundenspezifischen Intel Xeon-Prozessoren

Die Grafik zeigt den aktuellen Stand und die Aussichten im Bereich der kundenspezifischen Intel Xeon-ProzessorenIntel benötigt die eASIC-Technologie, um programmierbare Logik in Xeon-Prozessoren zu integrieren und so Leistung, Stromverbrauch und Preis zu verbessern. Zusammen mit dem Standard-Xeon veröffentlicht Intel jetzt benutzerdefinierte Optionen für seine größten Kunden. Wie aus dem Diagramm ersichtlich, nimmt die Anpassungstiefe zu. Mit der Akquisition von eASIC wird dieser Prozess beschleunigt und erweitert. Es scheint, dass der Ansatz „CPU als ASIC“ uns viele interessante Dinge bringen kann.