1. Einleitung

Wir alle kennen das Problem von Hühnchen und Eiern: Arbeitgeber möchten keine Absolventen ohne Berufserfahrung einstellen, aber wo können Absolventen dann Berufserfahrung sammeln? In der Mikroelektronik ist dieses Problem angesichts der enormen Menge an spezifischer Erfahrung besonders akut. Seit der Sowjetzeit sind unsere Universitäten für ihre breiteste theoretische Ausbildung bekannt, die dem Absolventen in jeder schwierigen Lebenssituation helfen soll. Die moderne Industrie erfordert jedoch praktische Erfahrung. Wir fügen hier den Mangel an Motivation hinzu, der dazu führt, dass 15% der Absolventen in der Fachrichtung arbeiten, und wir bekommen den größten Personalmangel in der Branche, der sehr hohe Anforderungen an die Qualität des Personals stellt. Wenn jedoch jeder Schüler eine Glühbirne aus seinem eigenen Kristall „blinken“ könnte, könnte sich die Situation auf eine völlig andere Weise entwickeln.

Abbildung 1. KDPV

Was hindert solche Giganten der Ausbildung inländischer Mikroelektronik wie MEPhI und MIET daran, sich ähnlich wie ihre ausländischen Kollegen (z. B. MIT oder UZH) zu verhalten, indem sie es Doktoranden ermöglichen, ihre eigenen Kristalle herauszugeben? Natürlich kann davon ausgegangen werden, dass die Herstellung des eigenen Kristalls eine extrem lange, komplizierte und teure Aufgabe ist und daher für das Institut teuer und für den Studenten unmöglich ist. Dies ist jedoch nicht so. Werfen wir einen Blick auf eine der verfügbaren Technologien auf dem heimischen Markt für Mikroelektronik, deren Bekanntschaft es dem Studenten ermöglicht, im Hinblick auf künftige Beschäftigungsverhältnisse viel attraktiver zu werden, und deren Angebot es dem Studenten ermöglicht, seine Bewertung in den Augen von Bewerbern und Arbeitgebern deutlich zu verbessern.

2. Was ist BMK?

BMK ist ein basischer Matrixkristall. Ist es nicht klarer geworden? Machen Sie dann einen Schritt zur Seite und sehen Sie sich den stark vereinfachten Produktionszyklus für die Herstellung von kundenspezifischen Chips (ASIC) an:

- Schema Beschreibung Entwicklung

- Topologieerstellung

- Übertragen von Technologiedateien in die Anlage und Warten auf die Bereitschaft der Kristalle

- Messungen der erhaltenen Kristalle

- Gehäuse

- Zu verkaufen

Hier gibt es zwei sehr „lange“ Punkte - die Entwicklung des Schemas und die Erwartung der Ergebnisse der Anlage. Verschiedene Methoden werden verwendet, um die Entwicklungszeit zu verkürzen. In einer Studentenumgebung ist Teamwork die beste Lösung. Wir interessieren uns jedoch für den zweiten Punkt - die Arbeitszeit der Anlage. Aufgrund der Tatsache, dass die mikroelektronische Anlage eine sehr inerte Produktion ist, sollte alles nach Plan verlaufen. Nicht rechtzeitig zum Produktionsstart? Der nächste Versuch ist durch das Quartal. Die Produktion selbst kann je nach Komplexität des Produkts bis zu sechs Monate dauern. Darüber hinaus sind diese sechs Monate der genehmigte Produktionszyklus auf hochautomatisierten Maschinen und nicht die Schlamperei des Personals. Wie können diese Bedingungen reduziert werden? Durch die Einführung einer bestimmten gemeinsamen Basis in allen erstellten Schemata, so dass die Einführung von Unterschieden schnell vonstatten geht.

Diese gemeinsame Basis ist das BMK - ein Kristall mit vorab angeordneten Transistoren, dessen funktionaler Zweck durch die Metallisierungsschichten bestimmt wird, mit denen Transistoren miteinander verbunden werden können. Diese Verbindungen bilden die einzigartige Funktionalität des Kristalls.

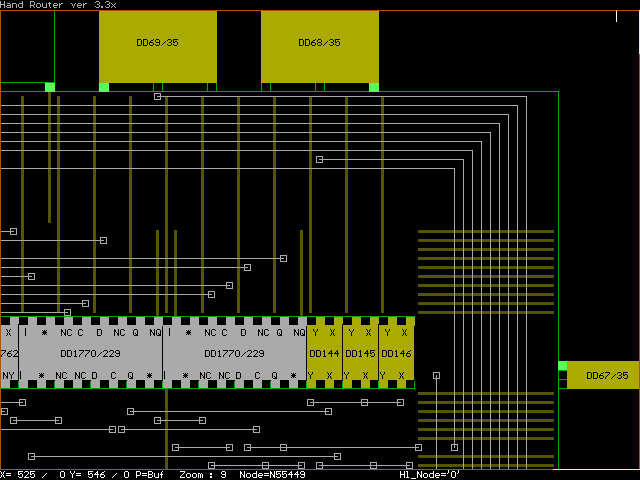

Abbildung 2. Hand Router v3.3, ursprünglich aus dem Darm von NICEVT, erstellt in den 1980er bis 1990er Jahren.

Auf einem BMK können unter Verwendung verschiedener Metallisierungsschemata Hunderte verschiedener Mikroschaltungen für verschiedene Organisationen hergestellt werden. In diesem Fall wird BMK selbst zu einem Massenproduktionsprodukt für die Anlage, und die Endbearbeitungsstufen - Metallisierungsschichten - können schnell nach Kundenwunsch geändert werden. So werden neue Produkte häufiger in die Produktion eingeführt und die Preise gesenkt. Für die studentische Entwicklung sind beide Punkte äußerst relevant.

3. Warum BMK?

Vergleichen wir die Vorteile der Verwendung verschiedener Trainingsmethoden und sehen, was bei geringsten Kosten den größten Effekt erzielt.

Tabelle 1. Vergleich der pädagogischen Wirkung des Lernens mit verschiedenen Methoden

Header-Codierung Andernfalls passt es nicht in die Breite des Layouts.

A - FPGA-orientierte Entwicklung

B - BMK ohne Verwendung von FPGAs und mit einer echten Version

C - BMK mit FPGA und mit echtem Release

D - ASIC ohne FPGA und ohne echte Freigabe

E-ASIC mit FPGA und ohne echte Veröffentlichung

F - ASIC mit FPGA und Real Release

G - Aktuelles Trainingsprogramm bei MEPhI, kaf. 27

| Routenkomponente | A. | B. | C. | D. | E. | F. | G. |

|---|

| Erklärung des Problems | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| RTL-Programmierung | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| ASIC-basierte RTL-Programmierung | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Arbeiten Sie mit modernem CAD | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| Grundlegendes zum FPGA-spezifischen Code | ■ | □ | ■ | □ | ■ | ■ | ○ |

| Grundlegendes zum Synthesizer | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Grundlegendes zu den Einschränkungen | ○ | ■ | ■ | □ | □ | ■ | □ |

| Die Bedeutung von Platzierung und Rückverfolgung verstehen | ○ | ■ | ■ | □ | □ | ■ | □ |

| Testen | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Erstellung einer Verifizierungsumgebung | ■ | ■ | ■ | □ | ■ | ■ | □ |

| Multi-Corner-Simulation | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Extraktionsmodellierung | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Gehäuse | □ | ■ | ■ | □ | □ | ■ | □ |

| Analoge Schaltung | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Arbeiten Sie mit Messanlagen | □ | ■ | ■ | □ | □ | ■ | ○ |

| Arbeit im Labor | ■ | ■ | ■ | □ | □ | ■ | ○ |

| Kosten | 1 | 2 | 3 | 0 | 1 | 4 | 0 |

■ - ist im Programm vorhanden;

□ - im Programm abwesend;

○ - Optionen sind möglich.

Diese Tabelle wird ausschließlich aus meiner Vision gefüllt, wie sich das Vorhandensein einer bestimmten Phase in einem sphärischen Abschlussprojekt in einem Vakuum auf die Sorgfalt der Schüler auswirkt. In Wirklichkeit kann jemand die gesamte Route ohne Unterrichtshilfe beherrschen, während jemand keinen Multiplexer auf Verilog schreiben kann. Die Zeile "Kosten" spiegelt die Positionierung oben wider, jedoch in keinem Fall Multiplikatoren. Außerdem berücksichtigen die „Kosten“ aus verschiedenen Gründen nicht die tatsächlichen Kosten von CAD.

Jetzt wird klar, dass die Route, die auf die Veröffentlichung von BMK unter Verwendung von FPGAs und mit der tatsächlichen Veröffentlichung abzielt, zu geringeren zusätzlichen Kosten genau die gleichen Fähigkeiten umfasst, die für die Veröffentlichung von ASIC erforderlich sind. Der Rest der Routen deckt zwar nominell ein breites Spektrum an Fähigkeiten ab, wird jedoch in der Praxis von den Schülern nicht gewissenhaft durchgeführt, da sie nicht motiviert sind, große Anstrengungen zu unternehmen, ohne dass ein sichtbares Ergebnis erzielt wird.

4. Market Watch

Bisher ist das Design von Mikroschaltungen für Einsteiger zu einer relativ einfachen Aufgabe geworden: Jeder hat von FPGAs (Integrated Circuits mit programmierbarer Logik), Synthesizern einer Schaltung aus Code, Programmen zum Anordnen von Komponenten und der anschließenden Verfolgung einer Mikroschaltung gehört. Gleichzeitig haben viele unerfahrene Entwickler Schwierigkeiten, sich vorzustellen, was BMK ist, wie man damit arbeitet und welche Vorteile es bietet. Leider führt diese Situation für BMK-Hersteller zu folgenden Ergebnissen:

"Die Analyse von 2009 zeigt den Abfluss einiger Verbraucher aufgrund der Ausweitung des Anwendungsbereichs importierter FPGAs auf der Grundlage erteilter Genehmigungen." (C) den Jahresbericht von Anstrem OJSC für 2009.

Auf dem modernen Mikroelektronikmarkt gibt es viele BMK-Hersteller: sowohl im Inland als auch im Ausland. Insbesondere im Unionsstaat Russland und in Weißrussland gibt es mindestens sechs Hersteller von Mikroschaltungen, die ihre BMCs zur Entwicklung anbieten: Angstrem OJSC, IEC NN, Progress NIIMA JSC, Wissenschafts- und Produktionszentrum für Technologie, Physikphysik OJSC und Integral Minsk ".

Normalerweise werden spezialisierte CAD-Systeme bekannter Unternehmen wie Cadence, Synopsis oder Mentor Graphics für die Entwicklung von Mikroschaltungen verwendet, aber bei BMC ist alles etwas komplizierter. Diese Software bietet keine offizielle Unterstützung für BMK als separate Art von Mikroschaltung, aber es ist möglich, sie mit verschiedenen Tricks im richtigen Modus arbeiten zu lassen. In dieser Situation müssen BMK-Entwickler ihre eigenen einzigartigen Entwurfsrouten entwickeln, die manchmal OpenSource-Software, beispielsweise Yosis, zusammen mit unabhängig entwickelter Software verwenden.

- Im Fall von Angstrom OJSC ist es sehr schwierig, die genauen Informationen und den verwendeten CAD zu finden. Es gibt jedoch Voraussetzungen, um zu glauben, dass ihr CAD „Nevod“ nicht mehr verwendet wird und der Übergang zur Verwendung von Cadence-Produkten abgeschlossen ist.

- IEC NN, OJSC NPO Fizika, JSC NIIMA Progress und Integral liefern keine Informationen zum verwendeten CAD. Integral verfügt jedoch über PDK unter Cadence, sodass wir den Schluss ziehen können, dass der Rest der Route ebenfalls vorhanden ist.

- Das NPK "Technological Center" verwendet seine CAD "Ark", die fast die gesamte Konstruktionsroute implementiert. In jedem Fall wird dies auf ihrer Website genehmigt.

5. Wie viele Ventile reichen für alle?

Ein beliebter Grund für die mangelnde Bereitschaft, mit BMK zu arbeiten, ist die Unsicherheit darüber, ob das entwickelte Schema in dieses BMK passt und mit welcher Geschwindigkeit dies alles funktionieren wird. Natürlich ist es gut, wenn es eine BMK-Serie mit einer einzigen Designbibliothek gibt, und Sie können bei Bedarf zu einem größeren oder schnelleren Kristall springen, aber dies ist nicht immer möglich. Hier ist zum Beispiel alles über TSMC klar: Es gibt viele Unternehmen, die offen die Geschwindigkeit ihrer Schaltungen angeben, die auf der einen oder anderen dieser Schaltungen ausgeführt werden. Prozess. Was ist mit unserem BMK? Wo kann ich eine Liste der Produkte erhalten, die auf der Grundlage von BMK erstellt wurden, und deren Leistung sehen?

Einige Beispiele:

- Digital-Analog-BMK. Über 300 Gates + 8 Leistungstransistoren. Ein Timer-Schema für 2 Minuten mit zwei Schutzstufen ist implementiert. Lastüberwachung an Stromspiegeln, Leistungstransistoren zur Steuerung der Last. Reduzierter Stromverbrauch, arbeiten mit Quarz 32,768 kHz, der Bereich der Versorgungsspannungen von 1,8V bis 9V.

- Digital froh. anhaltende BMK. 100.000 Ventile. Logik-Specials. Ziel + NCO (numerisch gesteuerter Oszillator). Batteriephase 40 Bit, Sinus - 12 Bit. Zwei Register steuern die Sinusfrequenz, die parallele und die serielle Steuerung. Die Ausgabe erfolgt parallel.

- Digital-Analog-BMK. Über 400 Tore + DAC von 10 Kategorien. 7-Bit-Sinusgenerator mit Stromausgang.

- Digitales BMK. Von 1500 bis 3000 Ventile. Verschiedene Anschlüsse des Multiplexkanals GOST 26765.52-87.

- Digitales BMK. Über 500 Tore. Ein Achtkanalgenerator zur Steuerung der Primärwicklungen von Transformatoren.

- Digitales BMK. Über 3000 Tore. Mehrheitsschaltung für 8-Bit-Bus.

Leider führen die Besonderheiten des Marktes dazu, dass die überwiegende Mehrheit der Entwicklungen bei BMK der Öffentlichkeit unbekannt bleibt. Öffentliche Daten geben keine klare Vorstellung von der Geschwindigkeit, und die in den Broschüren angegebenen Zahlen sind nicht eindeutig. Für das Kennenlernen der Technologie ist jedoch nicht viel erforderlich, und es ist viel einfacher, bereits eine gewisse Erfahrung dahinter zu haben, um eine ungefähre Schätzung der Komplexität eines bestimmten Schemas abzugeben.

6. Entwicklungsprozess

Kommen wir zum interessantesten. Wir haben: BMK für ~ 3k Gates (1 Ventil = 2 CMOS-Transistoren) mit Kanalarchitektur, Verdrahtung in einer Metallschicht und einer Polysilicium-Unterschicht; Begeisterung; Genehmigung der Unternehmensführung zur Selbstschulung der Mitarbeiter.

Die Idee des zukünftigen Kristalls entstand aus dem Nichtstun, nämlich aus dem Lesen eines Forums, in dem insbesondere über schaltungskompakte Lösungen zur Berechnung von Sinuscodes gesprochen wurde. Dieses Thema erschien mir interessant und ich beschloss zu sehen, was in dieser Richtung getan werden kann.

Nun wollen wir sehen, was getan wurde, was nicht, welche Fehler und welche Schlussfolgerungen gezogen wurden.

6.1 Design

Oberflächenstudien haben gezeigt, dass es einen Algorithmus zur Berechnung von Sinuswerten gibt, der aus mathematischen Operationen nur Summation, Subtraktion und Verschiebung nach rechts erfordert. Es stellte sich heraus, dass dies nicht nur ein Algorithmus ist, sondern eine ganze Familie namens CORDIC (Coordinate Rotation Digital Computer). Diejenigen, die an den Details des Algorithmus interessiert sind, können sich auf die Referenzliste am Ende des Artikels beziehen, aber ich werde nur klarstellen, dass Sie mit diesem Algorithmus nicht nur den Sinus, sondern auch den Cosinus berechnen können, die Tangente biegen, die Argumente multiplizieren und dividieren und einige hyperbolische Funktionen zählen können.

Nachdem ich viele Veröffentlichungen zu diesem Algorithmus studiert und dieses Wissen in meinem Kopf systematisiert hatte, stellte ich fest, dass Sie versuchen können, diesen Algorithmus auf einem BMK mit einer Kapazität von etwa 3.000 Ventilen zu implementieren.

Was haben wir also in der Schaltungsarchitektur?

- Erweiterter Pipeline-CORDIC-Algorithmus zur Berechnung des Sinus.

- 4 zusätzliche Bits in internen Datenbussen, um Rundungsfehler zu kompensieren.

- Kumulativer 11-Bit-Summierer für den Phasenwert.

- Das Phaseninkrement wird über den Parallelbus eingestellt.

- Ausgangsdatenformat: 7 Bit + Vorzeichen, Parallelbus.

Alles scheint in Ordnung zu sein, aber was passiert, wenn Sie Rundungsfehler nicht kompensieren? Und hier ist was (Vergleich des internen Busses 11bit und 8bit):

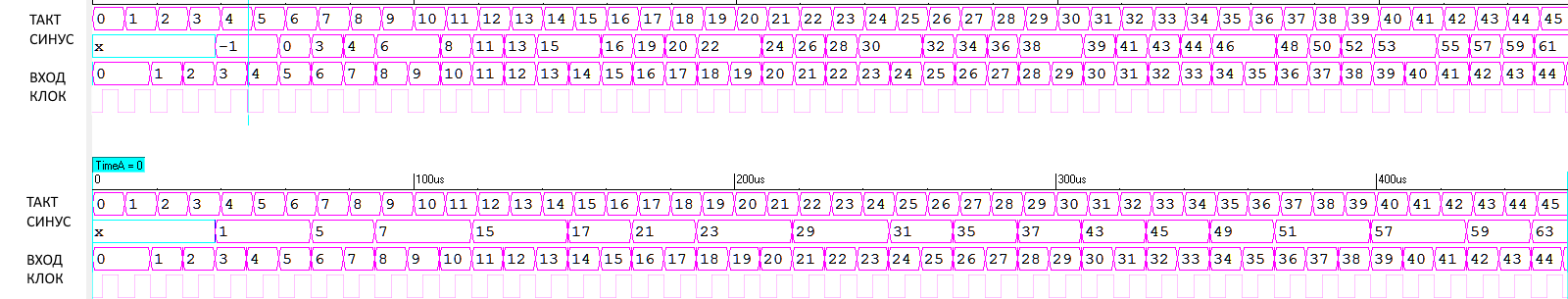

Abbildung 3. Vergleich der Ausgabe des CORDIC-Algorithmus bei Verwendung interner Busse mit 11 Bit bzw. 8 Bit.

Wenn Sie auf die zweiten Datenzeilen achten, können Sie feststellen, dass Rundungsfehler die Qualität Ihrer Berechnungen effektiv beeinträchtigen können.

Wenn wir diesen Chip in Zukunft an den 7-Bit-DAC anschließen, erhalten wir einen vollständig geeigneten Sinusgenerator (DDS, unserer Meinung nach - direkte digitale Synthese). In diesem Fall haben wir die Möglichkeit zur Frequenzmodulation des Sinus, aber es gibt keine Möglichkeit zur Phasenmodulation.

Im Allgemeinen unterscheidet sich die Route für die Arbeit mit kleinen BMCs etwas von der aktuellen Entwurfsroute. Wenn Sie darüber nachdenken, werden die Unterschiede offensichtlich: Bei einem so kleinen Ventilvolumen ist es notwendig, jedes Ventil äußerst effizient einzusetzen, und das Hauptparadigma des modernen Designs ist überhaupt nicht das. Sie sagt, dass das Produkt in jeder Phase architektonisch mit modernen Systemen zur automatisierten Prüfung, Verifizierung und Messung kompatibel sein sollte. In diesem Fall bleibt die Frage des Ventilwirkungsgrads als notwendiger Overhead außerhalb der Klammern. In den Jahren der dynamischen Entwicklung von Produktionstechnologien war es überflüssig, über Effizienz nachzudenken. Wenn wir also (und wenn) immer noch die physikalische Grenze erreichen und aufhören, die Dichte der Transistoren auf dem Kristall zu erhöhen, werden die Probleme der Effizienz der Nutzung des Bereichs bei vollem Wachstum auf uns zukommen. Nun, mit kleinen BMKs stehen sie sowieso auf voller Höhe, und daher die Schlussfolgerung: In der BMK von kleinen Tanks können und sollten Sie komplexe Designs verwenden, die verschiedene knifflige Blockgenerierungsschemata, verschiedene Latches, Rückmeldungen und andere Dinge verwenden, für deren Verwendung auf der modernen Route Ein leitender Ingenieur hätte sich die Hände gerissen.

Das Hauptproblem bei der Verwendung solcher Dinge besteht darin, dass der Ingenieur genau wissen muss, was er tut und warum. Wenn es jedoch Verständnis gibt, kann der Gewinn fantastisch sein. Wenn es kein Verständnis gibt ... nun, Sie können mit einer Million verschiedener effektiver Methoden in das Bein schießen.

Wie sah die Designroute in meinem Fall aus:

- Manuelles Diagramm als Diagramm von Bibliothekselementen

- Schätzung des resultierenden Schaltungsvolumens

- Verarbeitung der Schaltung, bis das Schaltungsvolumen 80% der BMK-Kapazität überschreitet

- Dazu gehören auch Arbeiten zur Erstellung neuer Bibliothekselemente, deren Prüfung und Integration in die Entwurfsroute

- Erstellung von Tests für die Schaltung

- Manuelle Schaltungsverfolgung

Erfahrene Designer hier mögen sofort einwenden, dass einige wichtige Schritte übersehen wurden, aber ich habe wirklich vergessen, etwas zu erwähnen.

Das manuelle Design zeigt sehr gut, wie wichtig eine hochwertige Komponentenbibliothek ist. Die ersten Varianten der Schaltung passten nicht einfach durch das Volumen der Logik in den Kristall, sondern im Fall eines Kanal-BMC - einer, bei dem die Verdrahtung durch die zwischen den "Reihen" von Transistoren verlegten Kanäle verläuft - werden ungefähr 30% des Schaltungsvolumens durch Verbindungen belegt. Daher musste ich die Bibliothek etwas erweitern, basierend auf der Topologie, die in diesem speziellen Projekt erhalten wurde. Dieser Ansatz ermöglichte es, eine beträchtliche Anzahl von Toren zu retten und sogar alle Routen mehr oder weniger frei zu legen.

Die endgültige Kristallfüllung beträgt 72%, ein weiteres Drittel des Kristalls ging an die Verkabelung. Dann wurden die Dateien in die Fabrik übertragen und ich kehrte zu meinen aktuellen Arbeitsprojekten zurück.

Bei der „manuellen“ Entwurfsmethode müssen folgende Punkte beachtet werden:

- Sie können Bibliothekselemente nicht gedankenlos basierend auf ihrer Funktion verwenden. Es ist notwendig zu untersuchen, woraus dieses Element auf Transistorebene besteht, ob es digital oder analog ist. Was sind seine Tragfähigkeiten in Bezug auf Ein- und Ausgänge, ob er nun reine CMOS-Logik oder TG oder etwas anderes ist.

- Es ist notwendig, die Leistung der Elemente und ihre Belastung zu berücksichtigen und zu koordinieren.

- Wenn Sie einen synchronen Trigger haben, müssen Sie ihn mit Signalen gleicher Leistung takten.

- Wenn Sie ein Signal ohne Zwischenverstärkung verwenden und es bei vielen Verbrauchern geladen ist, kann das Signal sehr stark ausfallen. Dies mag unter normalen Bedingungen unbedeutend sein, ist jedoch beim Testen auf WWF (externe Faktoren) von entscheidender Bedeutung.

Kein Modellierungssystem kann Ihr eigenes Gehirn ersetzen. Im Allgemeinen können Sie keine Simulation ausführen, wenn Sie selbst nicht verstehen, wie die Schaltung funktioniert.

6.2 Messungen

Ein äußerst wichtiger Schritt bei der Arbeit mit einem Kristall sind seine Messungen. Drei Arten von Messungen können unterschieden werden: technologische, funktionale, elektrische. Die ersten bestätigen, dass die Anlage nicht hochgezogen ist und der Kristall technologisch korrekt hergestellt wurde. Letztere bestätigen, dass die Theorie (d. H. Modellierung) mit der Praxis konvergiert (realer Kristall). , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

. 4 (!) . , , . , ?) " ".

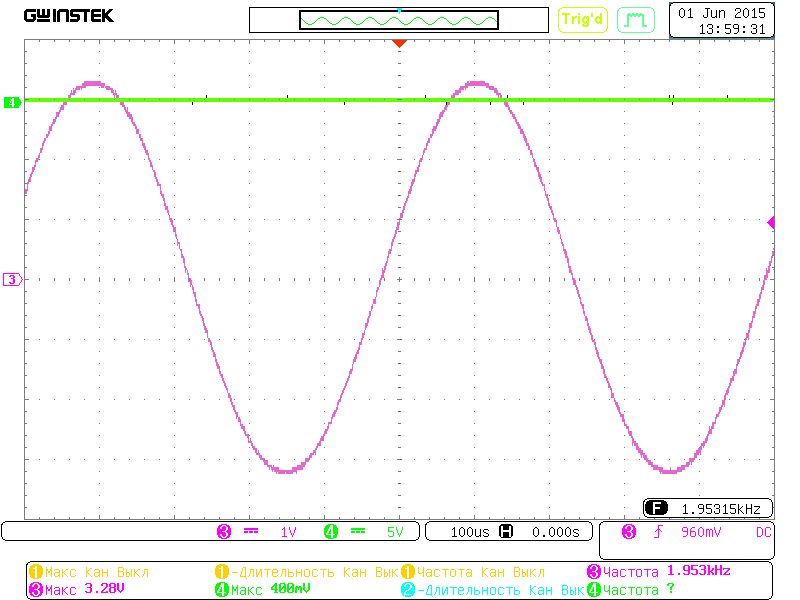

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

Hinweis .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

Literatur

- Google

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf