Hallo!

Der Artikel beschreibt die Architektur des virtuellen Speichersystems ARMv7.

Spoiler ÜberschriftDie Feinheiten von Caching, DMA, LPAE und dergleichen werden hier nicht berücksichtigt. Eine detailliertere Beschreibung finden Sie in der Literatur am Ende des Artikels.

Einführung

Das virtuelle Speichersystem führt mehrere Aufgaben aus. Erstens können Sie Benutzerprozesse in getrennten, voneinander isolierten Speicherbereichen platzieren. Auf diese Weise können Sie die Zuverlässigkeit des Systems erhöhen. Fehler eines Prozesses wirken sich nicht auf den Betrieb anderer Prozesse aus. Zweitens kann das Betriebssystem dem Prozess mehr Speicher zur Verfügung stellen als das System. Nicht verwendete Speicherseiten werden in einen permanenten Speicher verschoben, und die erforderlichen Seiten werden von dort geladen, wodurch die Illusion einer größeren Speichermenge entsteht, als sie tatsächlich ist. Drittens erleichtert der kontinuierliche virtuelle Raum das Schreiben von benutzerdefinierter Software. Alle Prozesse werden im selben Bereich ausgeführt, das Betriebssystem verbirgt die tatsächliche Speicherkonfiguration im System.

Definitionen

Die folgenden Definitionen werden im Artikel verwendet:

Virtuelle Adresse - Die vom Prozessorkern verwendete Adresse. Der Stapelzeiger, der Befehlszähler und das Rückgaberegister verwenden eine virtuelle Adresse.

Physische Adresse - Die Ausgangsadresse auf dem Prozessorbus.

Eine Seite ist eine Einheit zur Adressierung des virtuellen Speichers.

Abschnitt - ein Analogon der Seite, hat eine größere Größe.

Ein Rahmen ist eine Adressierungseinheit für den physischen Speicher.

Seitentabelle - Ein Array von Datensätzen zum Übersetzen von Adressen.

ASID ist die Adressraumkennung.

TLB - Puffer für die schnelle Übersetzung von Adressen.

MMU ist eine Speicherverwaltungseinheit.

TLB

TLB ist ein sehr schneller Hardware-Puffer, der die Ergebnisse der neuesten Adressübersetzungen enthält. Die Kernelanforderung zum Übersetzen der Seitenadresse und der aktuellen ASID kommt im TLB an. Wenn dort ein gültiger Eintrag vorhanden ist, werden die Berechtigungen zum Zugriff auf diesen Speicher überprüft, die Zugriffsmethode und die entsprechende Rahmenadresse an die MMU zurückgegeben. Wenn der Speicherzugriff verweigert wird, wird eine Hardware-Ausnahme ausgelöst. Wenn ein TLB-Fehler aufgetreten ist (es wurde kein Datensatz gefunden), unterscheidet das weitere Verhalten von TTBCR zwischen Groß- und Kleinschreibung. Eine Suche kann in den Seitentabellen durchgeführt werden oder eine Ausnahme wird ausgelöst.

Es ist wichtig zu beachten, dass Sie beim Bearbeiten von Seitentabellen den TLB korrekt zurücksetzen müssen, da Dort können irrelevante Informationen gespeichert werden.

Das Aktualisieren von Einträgen im TLB ist für den Round-Robin-Programmierer transparent.

Es ist auch möglich, einige Einträge in den TLB hochzuladen und zu sichern, um deren Verdrängung zu verhindern.

Abbildung 1. TLB

Abbildung 1. TLBSeitentabellen

ARMv7 ist eine 32-Bit-Architektur, daher verfügen wir über 4 GB adressierbaren virtuellen Speicher.

Die Seitentabellen sind in zwei Ebenen unterteilt - L1 und L2.

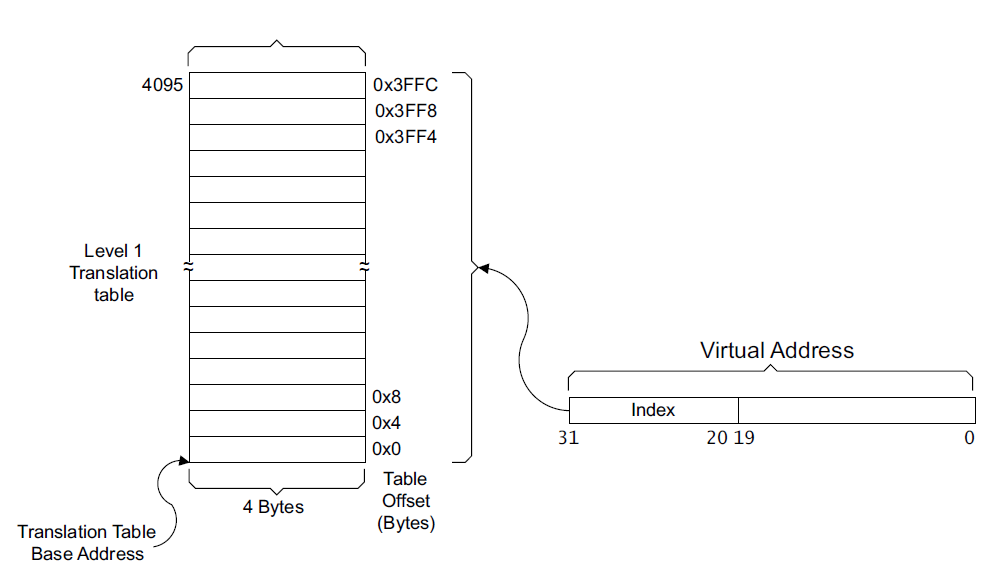

Tabelle L1 beschreibt alle 4 GB Adressraum. Es besteht aus 4096 32-Bit-Datensätzen, von denen jeder 1 MB beschreibt. Einträge in der Tabelle werden durch die hohen 12 Bits der virtuellen Adresse ausgewählt.

Abb. 2 Suchen Sie nach Einträgen in Tabelle L1

Abb. 2 Suchen Sie nach Einträgen in Tabelle L1Tabelle L1 befindet sich im physischen Speicher und ist an einem 16-KB-Rand ausgerichtet. Für diese Einträge gibt es 4 Optionen: zum Beschreiben von Seiten, Abschnitten und Unterabschnitten. Nun, ein leerer Datensatz für Speicher, der noch nicht zugeordnet ist.

Abb. 3 Arten von Einträgen in L1

Abb. 3 Arten von Einträgen in L1Die Bits 0 und 1 geben den Datensatztyp 00b-Fehler an, 01b ist der Seitendeskriptor, 10b ist der Abschnittsdeskriptor (und der Überabschnitt).

Wenn der physische Speicher paginiert ist, speichert die Tabelle L1 die Adresse der Tabelle L2 (physisch, ausgerichtet auf 1 KB). Bit 9 wird vom Hersteller bestimmt (Implementierung definiert), Bits [8: 5] - für den Domänenmechanismus (in ARMv7 veraltet), SBZ - Nullen.

Wenn wir den Speicher in Abschnitte unterteilen möchten, muss in L1 die entsprechende physikalische Adresse geschrieben werden. Der Abschnitt bezieht sich direkt auf den ausgerichteten physischen Speicherbereich von 1 MB. Keine Notwendigkeit für Tabelle L2. Supersection ist ein Sonderfall der Partitionierung. Der Eintrag in der L1-Tabelle sollte 16 Mal wiederholt werden. Die Ausrichtung der zugewiesenen Blöcke des physischen und virtuellen Speichers beträgt ebenfalls 16 MB.

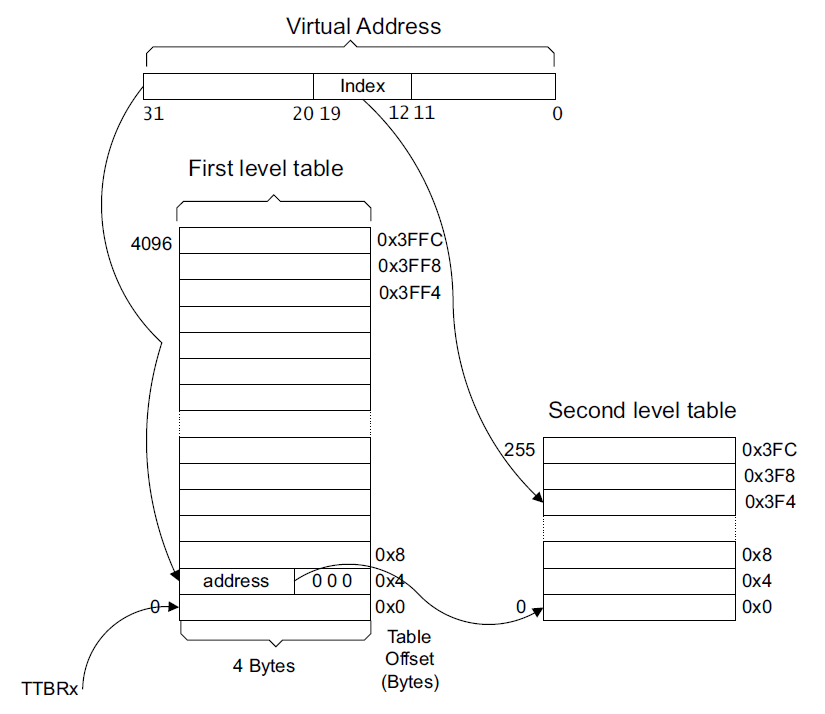

Tabelle L2 besteht aus 256 Einträgen mit 32 Bit. Es sollte auf 1 KB ausgerichtet sein.

Abb. 4 Suchen Sie nach Einträgen in Tabelle L2

Abb. 4 Suchen Sie nach Einträgen in Tabelle L2Die Indizes in Tabelle L2 werden aus den durchschnittlichen 8 Bits [19:12] der virtuellen Adresse gebildet. Jeder Tabelleneintrag enthält die Adresse des Frames.

Abb. 5 Arten von Einträgen in L2

Abb. 5 Arten von Einträgen in L2Seiten können zwei Größen haben: 64 KB (große Seite) und 4 KB (kleine Seite).

Die AP- und APX-Bits setzen Lese- / Schreibberechtigungen im privilegierten / nichtprivilegierten Modus (Kernel / Benutzer). Die TEX-, C-, B-, S-Bits sind für den Speichertyp, dessen Caching und Lese- / Schreibpufferung verantwortlich. Das nG - nonGlobal-Bit ermöglicht den Zugriff auf die Seite für alle Prozesse oder nur für eine bestimmte ASID.

Durch die Verwendung großer Seiten wird die Anzahl der Einträge im TLB reduziert. Anstelle von 16 Einträgen (4Kb * 16 = 64Kb) wird dort nur einer gespeichert. In Tabelle L2 müssen jedoch 16 identische Einträge eingetragen werden.

Die Fähigkeit, unterschiedliche Blockgrößen zu adressieren, ermöglicht es einerseits, Speicher mit der gewünschten Granularität zuzuweisen, andererseits die Anzahl der Aufrufe von Seitentabellen in einem relativ langsamen Speicher zu reduzieren.

Register

Zur Steuerung des Systems (einschließlich der MMU) in der ARM-Architektur wurde ein spezieller CP15-Coprozessor entwickelt. Zur Speicherverwaltung gehören anderthalb Dutzend seiner Register. Wir sind an mehreren interessiert - Control, TTBR0 / 1, TTBCR, ContextID.

Im Steuerregister ist das niedrigstwertige Bit für das Ein- und Ausschalten der MMU verantwortlich, alles ist einfach.

Das Registerpaar TTBR0 / 1 enthält die physikalischen Adressen der Tabellen der ersten Ebene. An diesen Adressen beginnt die MMU mit der Suche nach der gewünschten Seite.

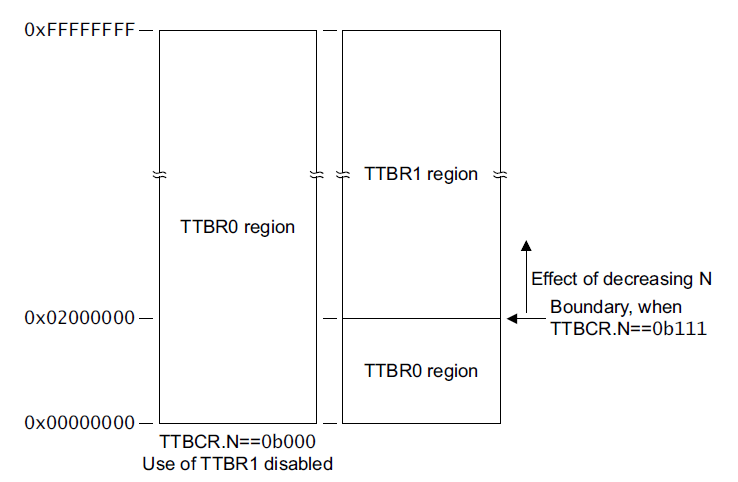

Mit dem TTBCR-Register können Sie den gesamten Adressraum in zwei Teile zwischen TTBR0 und TTBR1 aufteilen. Jeder von ihnen sendet seinen Teil der Adressen. Bits [2: 0] werden zum Einstellen der Größe verwendet. Die aufgezeichnete Zahl (von 0 bis 7 Dezimalstellen) maskiert den älteren Teil der virtuellen Adressen. Wenn der Wert "0" ist, werden alle Adressen über TTBR0 gesendet. Wenn "1", werden 31-Bit-Adressen maskiert und die unteren 2 GB virtuellen Speicherplatzes durchlaufen TTBR0, die oberen über TTBR1. "2" - 31 und 30 Bit werden maskiert und die Aufteilung in 1 GB bzw. 3 GB wird erhalten. Somit kann der untere Teil der Adressen für Benutzeranwendungen verwendet werden, wodurch das TTBR0-Register für einen neuen Prozess überlastet wird, und der obere Teil kann für Systemanforderungen belassen werden.

Abb. 6 Adressraum teilen

Abb. 6 Adressraum teilenBits [5: 4] sind für das TLB-Fehlerverhalten verantwortlich - Suche in Seitentabellen oder eine Ausnahme.

Das ContextID-Register enthält das ASID-Feld für den aktuellen Prozess. Sie muss zusammen mit dem Inhalt des Registers TTBR0 geändert werden, wenn der Kontext geändert wird.

Adressübersetzung

Der Algorithmus zum Konvertieren virtueller Adressen in physische Adressen lautet wie folgt:

- Suchen Sie im TLB-Puffer nach der angeforderten virtuellen Adresse und ASID

- Wenn der TLB nicht die erforderliche Adresse hat, wird in den Seitentabellen eine Hardware-Suche durchgeführt

Wenn der Kernel zuvor eine virtuelle Seite angefordert hat, wird diese im TLB gespeichert. In diesem Fall holt die MMU es aus dem Cache und es muss nichts getan werden. Wenn die Seite zum ersten Mal angefordert wird (oder von dort herausgedrückt wurde - der TLB ist nicht sehr groß), wird die Suche in den Tabellen L1-L2 durchgeführt. Somit ist die Zuordnung der virtuellen und physischen Adressen wie folgt:

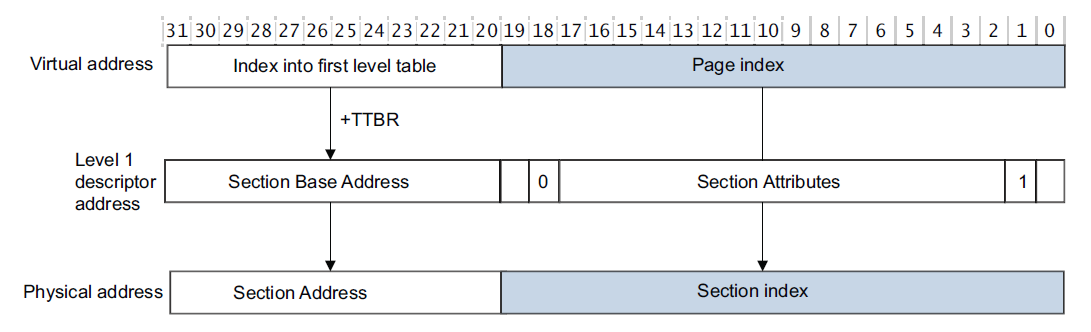

- Im Register TTBR0 \ TTBR1 wird die Adresse der Tabelle L1 gesucht.

- Die oberen 10 Bits der virtuellen Adresse bilden einen Index in der Tabelle.

- a) Wenn der Datensatz dem Abschnitt (Überabschnitt) entspricht, werden die Attribute des Abschnitts überprüft, und wenn alles in Ordnung ist, setzt sich die resultierende physikalische Adresse aus der Basisadresse des Abschnitts (Überabschnitt) und den mindestens 20 (24) Bits der virtuellen Adresse zusammen.

Spoiler Überschrift Abb. 7 Adressübersetzung in Supersection

Abb. 7 Adressübersetzung in Supersection

b) Wenn der Datensatz eine Tabelle L2 ist, wird die Suche darin fortgesetzt. Der mittlere Teil der virtuellen Adresse der Seite bildet den Index der Tabelle.

Spoiler Überschrift Abb. 8 Adressübersetzung in Tabelle L2

Abb. 8 Adressübersetzung in Tabelle L2

- TLB-Update läuft

Insgesamt besteht das virtuelle Speichersubsystem aus folgenden Teilen:

- Mehrere CP15-Steuerregister

- Seitentabellen mit Adressübersetzungsregeln

- TLB - Cache erfolgreicher Sendungen

- MMU ist eine Adressübersetzungseinheit.

Literatur

ARM Architecture Referenzhandbuch ARMv7-A und ARMv7-R Edition

Programmierhandbuch für die ARM Cortex-A-Serie