Jetzt veröffentlicht der Verlag von DMK-Press 2013 eine

russische Übersetzung des japanischen Mangas über digitale Schaltkreise, die von Amano Hideharu und Meguro Koji erstellt wurden. Trotz der leichtfertigen Form der Präsentation ist die Essenz dieses Buches sehr solide. Zum Beispiel geht es von alten Mikroschaltungen mit einem geringen Integrationsgrad aus und bindet sie schnell an die moderne Verilog-Hardwarebeschreibungssprache und integrierte programmierbare Logikschaltungen (FPGAs). Außerdem definiert der Manga klar, warum kombinatorische und sequentielle Schemata benötigt werden, und gibt eine Vorstellung von Optimierungsmethoden.

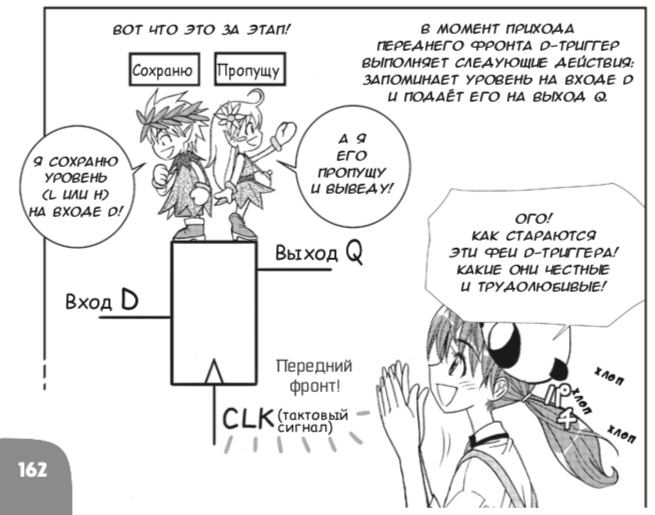

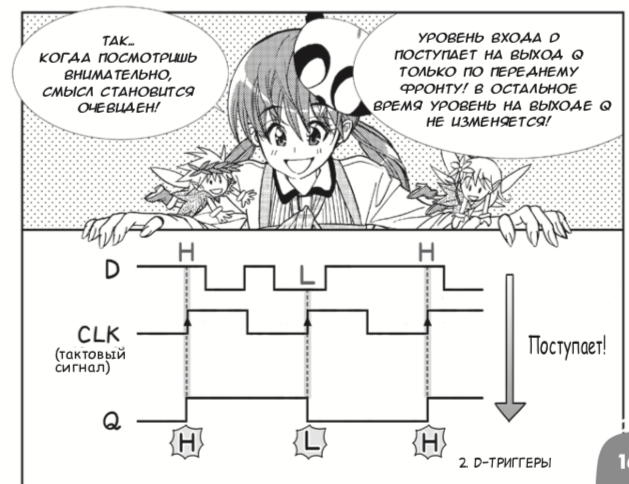

Manga vermeidet die Fehler vieler seiner Vorgänger. Einer dieser Fehler wurde von Charles Petzold in dem Buch „Code“ gemacht, in dem sequentielle Logik nicht für D-Trigger eingeführt wurde, die von der Flanke des Taktsignals gesteuert werden (flankengetriggertes D-Flip-Flop), sondern für D-Trigger mit Pegelbetrieb (Latches, pegelsensitiver D-Latch), obwohl später auf die richtigen Trigger umgeschaltet wurde. Der Fehler war wahrscheinlich darauf zurückzuführen, dass Charles Petzold, der als Autor von Lehrbüchern zur GUI-Programmierung in Microsoft Windows berühmt wurde, kein praktizierender Elektronikentwickler war und Latches für ihn „einfacher“ waren als frontmontierte Trigger. Das Problem ist, dass Latches mit der statischen Analyse von Verzögerungen bei der logischen Synthese, der Haupttechnologie für den Entwurf digitaler Schaltungen der letzten 30 Jahre, schlecht kompatibel sind. Systeme auf einem Chip in Gadgets wie einem iPhone verwenden in 99% der Fälle zustandsgesteuerte D-Trigger als Statuselemente, und Latches werden nur in ganz besonderen Fällen verwendet. Anfängern die Möglichkeit zu geben, Schaltkreise auf Riegeln zu bauen, bedeutet, sie irrezuführen.

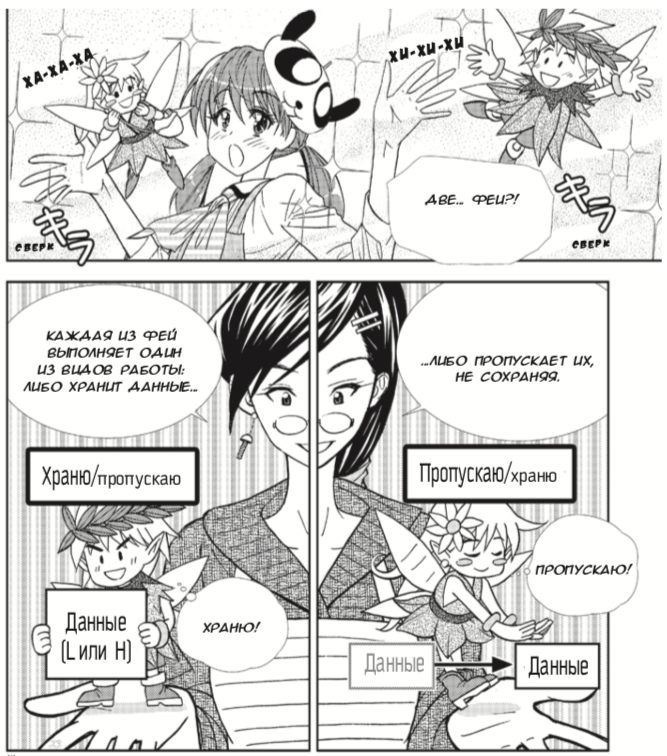

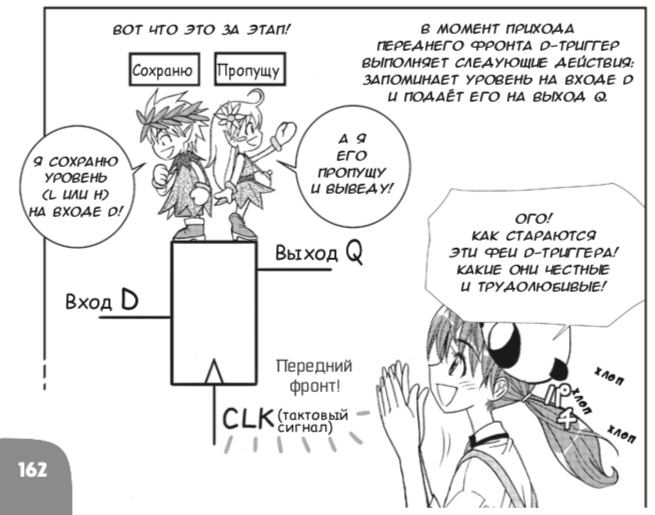

In diesem Sinne ist Manga besser als Petzold. So erklärt der Manga elegant den zweistufigen Master-Slave-D-Trigger, der von der Uhrfront gesteuert wird. Dies geschieht mit Hilfe der Feen „Hee hee hee“ und der Feen „Ha ha ha“:

Als nächstes hebe ich meine Kommentare blau hervor, damit sie nicht mit Zitaten aus dem Manga verschmelzen:

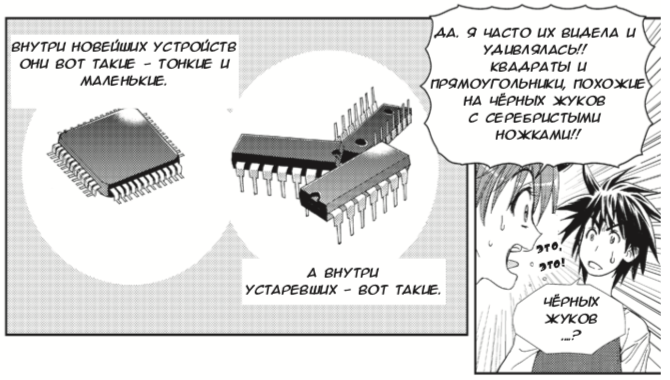

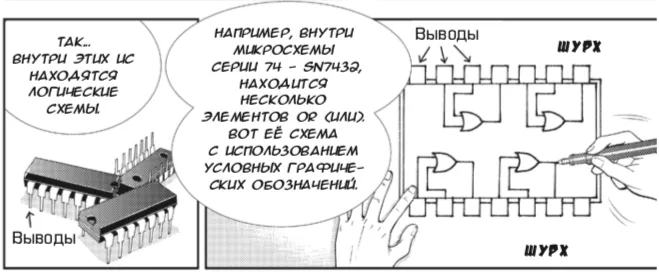

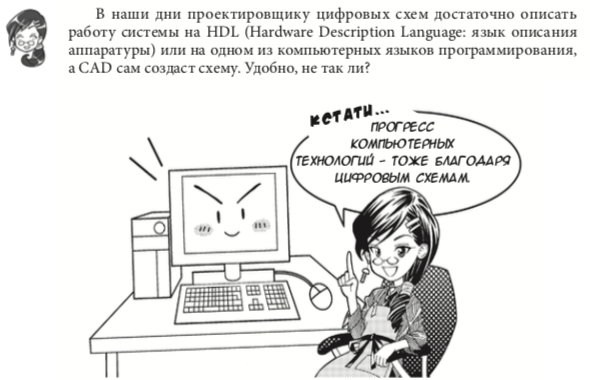

Aber fangen wir in der richtigen Reihenfolge an. Der Manga über digitale Schaltungen beginnt mit Mikroschaltungen, und sie erwähnt sofort sowohl alte Mikroschaltungen mit geringem Integrationsgrad mit mehreren logischen Elementen als auch moderne mit Millionen und Milliarden von Transistoren:

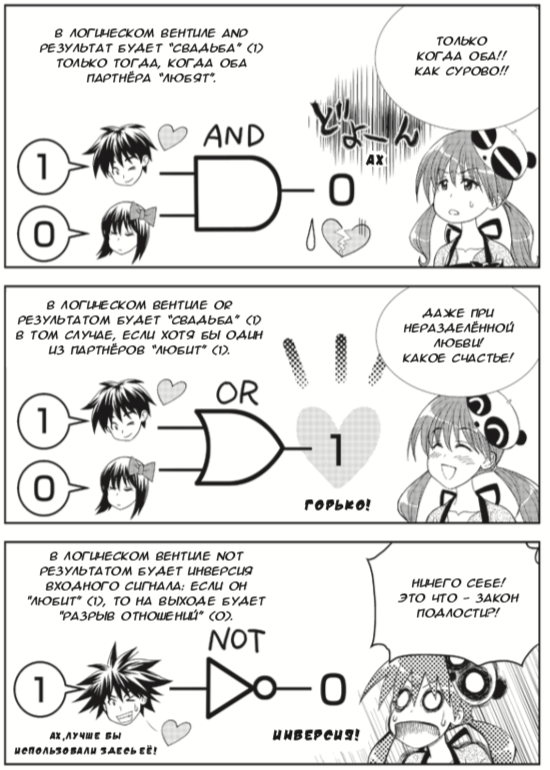

Der Manga erklärt die Arbeit logischer Elemente anhand einfacher und angenehmer Analogien für Jugendliche:

Warum überhaupt Mikroschaltungen mit geringem Integrationsgrad erwähnen, die vor 50 Jahren veraltet sind? Tatsache ist, dass Übungen auf einem Steckbrett mit solchen Mikroschaltungen trotz ihres ehrwürdigen Alters die intuitivste Möglichkeit sind, den Schülern zu zeigen, wie ein logisches Element funktioniert. Sie müssen keine Software zur Modellierung oder Synthese für FPGAs installieren. Alles was Sie brauchen ist ein Steckbrett, eine 9 Volt Batterie, eine Mikroschaltung, Kabel, LEDs und Tasten:

Einige Lehrer in Schulkreisen glauben, dass alle diese Übungen durch Arduino ersetzt werden sollten. Diese Meinung entstand in den 1970er und 1980er Jahren, als Mikrocontroller und eingebettete Prozessoren in die Formation kamen. Ein typischer Schüler im Jahr 1988 konnte nicht Hunderttausende von Dollar für die Herstellung seiner eigenen Mikroschaltung in der Fabrik ausgeben, und alte Mikroschaltungen mit einem geringen Grad an Integration in echte Industrieprodukte wurden immer weniger verwendet. Deshalb winkten sie damals der digitalen Logik für Schulkinder zu und steckten ihre ganze Energie in den Programmierunterricht. Hier ist ein Facebook-Kommentar, der diese Meinung in diesen Tagen beschreibt:

30 Jahre später änderte sich jedoch alles wieder:

1. Zunächst erschien im selben Jahr 1988 eine Technologie zum Entwerfen von Mikroschaltungen unter Verwendung der logischen Synthese aus dem Code in den Hardwarebeschreibungssprachen - Verilog und VHDL.

2. Gleichzeitig erschienen in den 1980er Jahren programmierbare integrierte Logikschaltungen (FPGAs) - Matrizen rekonfigurierbarer Logikelemente, mit denen Sie digitale Schaltungen kosten können, indem Sie einfach den Inhalt des Konfigurationsspeichers im FPGA ändern.

3. In den neunziger Jahren wurde der Unterricht in HDL, logischer Synthese und FPGAs in die Programme aller Abteilungen für Elektronik an westlichen Universitäten aufgenommen, obwohl dieser Prozess in Russland und der Ukraine aufgrund des Chaos nach der Perestroika langsamer war.

4. In den 2000er Jahren hörte die Geschwindigkeit traditioneller Prozessoren auf zu wachsen, und Vermarkter begannen, die Fragmentierung des Marktes für eingebettete Prozessoren (was geschah - Cloud, IoT) sowie das Auftreten von Kombinationen von Prozessoren und Spezialcomputern für verschiedene Aufgaben (was passierte - zuerst ist es schnell) vorherzusagen mobile Grafik, dann spezialisierte Chips für den Abbau von Kryptowährungen, Computer Vision und Beschleunigern für neuronale Netze).

5. Jetzt, im Jahr 2010, fielen die Preise für FPGA-Boards auf das Niveau, als sie Schulkindern zur Verfügung standen. Gleichzeitig benötigt die Industrie eine große Anzahl neuer Ingenieure, um riesige Mikroschaltungen mit neuronalen Netzen herzustellen. Selbst wenn Sie Ihr ganzes Leben lang in der Programmierung arbeiten, müssen Sie zum Verständnis neuer Systeme die Prinzipien des Gerätebetriebs kennen: kombinatorische und sequentielle Schaltungen, Zustandsmaschinen, Timing, Pipelining usw. Dann können Sie verstehen, ob es sich lohnt, die Daten mit einem normalen Programm oder einer Hardwareeinheit zu verarbeiten.

Mit Mikroschaltungen mit geringem Integrationsgrad können Sie also die Hardware-Grundelemente direkt "berühren". Unmittelbar nach der Erläuterung von Schemata mit geringem Integrationsgrad führt der Manga sowohl die Hardwarebeschreibungssprachen als auch das FPGA ein:

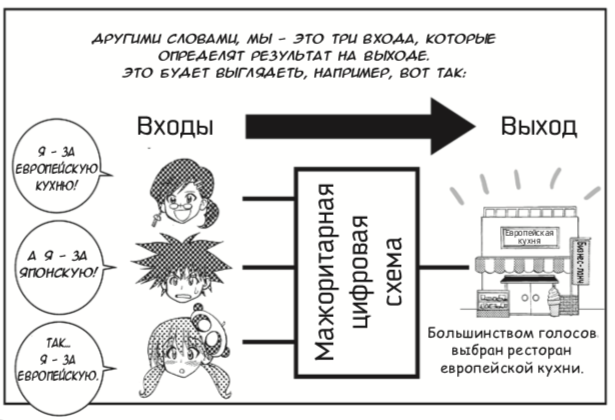

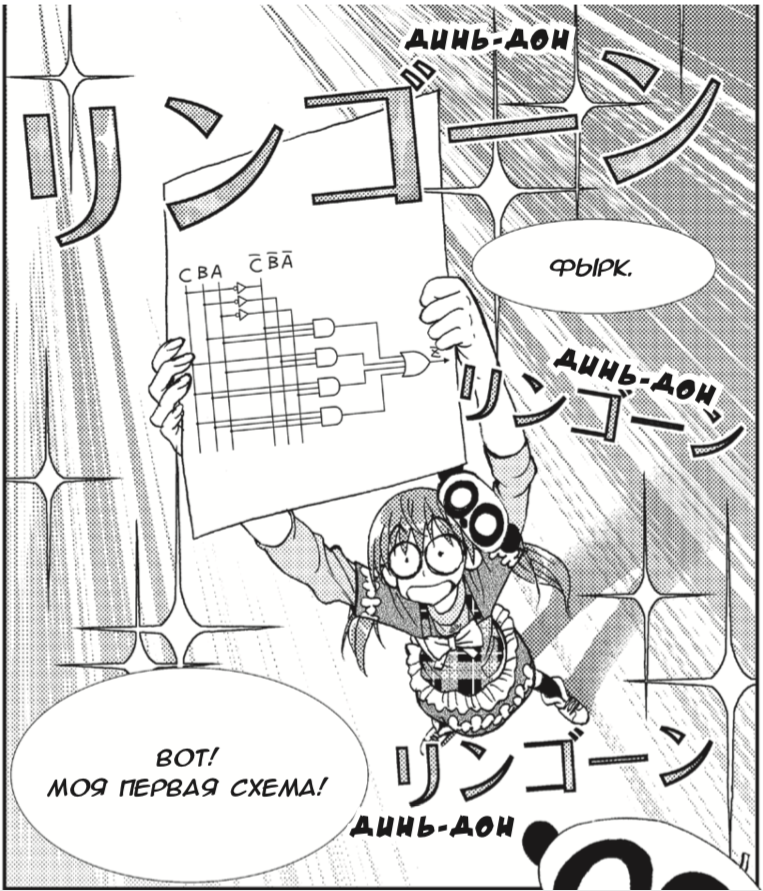

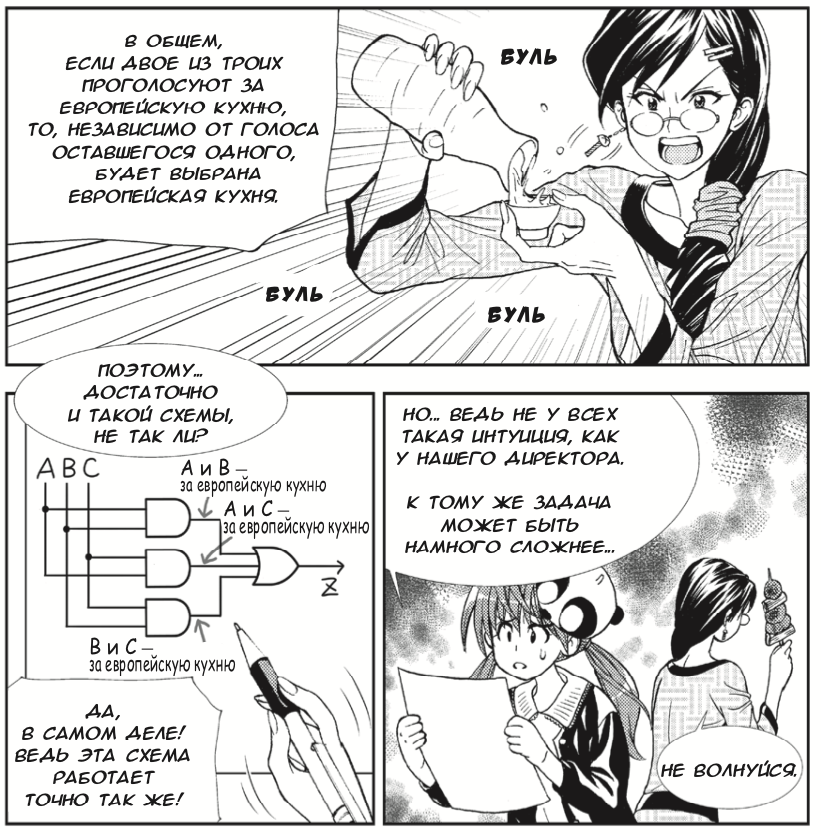

Nach der Beschreibung der logischen Elemente zeigt der Manga, wie ein nützliches kombinatorisches Schema für die Hauptabstimmung erstellt werden kann:

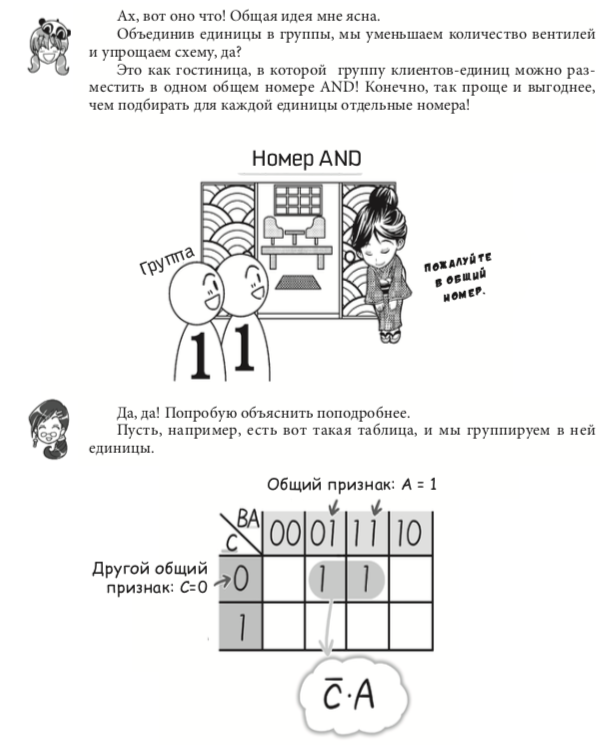

Dann wird dieses Schema optimiert. Meiner Meinung nach widmet Manga zu viel Zeit der kombinatorischen Optimierung. Aber es ist erwähnenswert, dass die Japaner den Manga geschrieben haben und ein Prinzip in der Kultur haben (Takuma-Sitzung) - etwas (wie ein Schwert) zu polieren, bis es perfekt wird. Daher gibt es im Manga sowohl eine Optimierung auf der Grundlage des gesunden Menschenverstandes als auch eine Optimierung auf der Grundlage von Carnot-Diagrammen. Die logische Synthese von Hardwarebeschreibungssprachen führt solche Optimierungen automatisch durch:

Der Manga hat auch ein romantisches Schema, das heißt eine Szene:

Das Mehrheitsentscheidungsschema kann leicht auf Mikroschaltungen mit einem geringen Integrationsgrad zusammengesetzt werden. Gleichzeitig kann man argumentieren, dass das Beobachten der kombinatorischen Elemente UND-ODER-NICHT / UND-ODER-NICHT auf dem Steckbrett nicht sehr interessant ist, da die Boolesche Algebra auch in der üblichen Programmierstunde erklärt wird. Es kann argumentiert werden, dass 7-Jährige zwar UND-ODER-NICHT verstehen können, einige Schulkinder jedoch beim Versuch, D-Trigger zu verstehen, auf eine mentale Barriere stoßen. In diesem Fall wird eine visuelle Demonstration wertvoller.

Leider kann der Schüler seine Hände nicht direkt mit D-Triggern im FPGA „berühren“. Es gibt Zehntausende von ihnen in FPGAs. Auf Arduino entsteht ein solches Objekt überhaupt nicht. Und auf einer Platine mit einem Mikroschaltkreis mit geringem Integrationsgrad ist der D-Trigger folgendermaßen zu spüren:

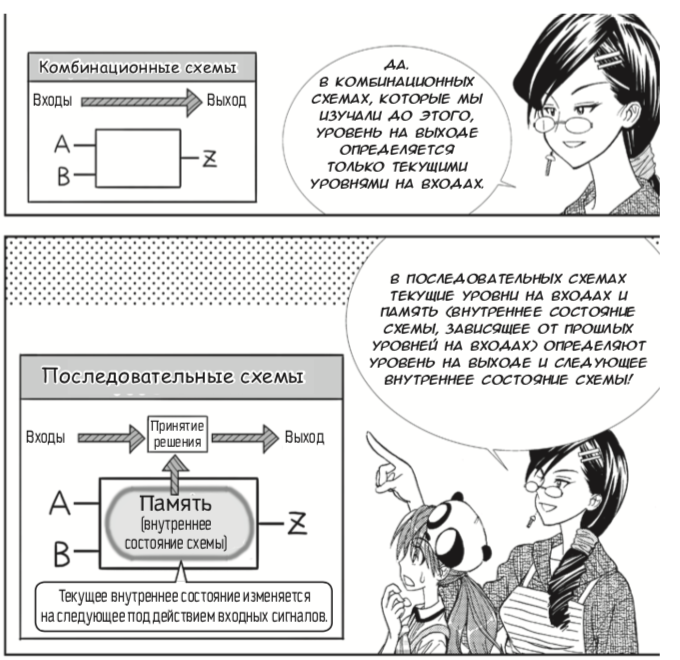

Und hier erfahren Sie, wie Sie sequentielle Schaltkreise und den D-Trigger-Manga erklären. Beachten Sie, dass der japanische Übersetzer das Wort "sequentiell" verwendete, um "sequentiell" zu übersetzen, obwohl der Begriff "sequentiell" in der russischen Literatur über digitale Schaltkreise festgelegt wurde:

Hier könnte genauer geschrieben werden, dass sequentielle Schemata im Gegensatz zu kombinatorischen Schemata das Wiederholen von Aktionen und das Erwarten von Ereignissen ermöglichen. Mit anderen Worten, sie machen den Computer „intelligent“. Ohne sie könnten Sie mit einem Computer nur die Werte einfacher arithmetischer Ausdrücke berechnen:

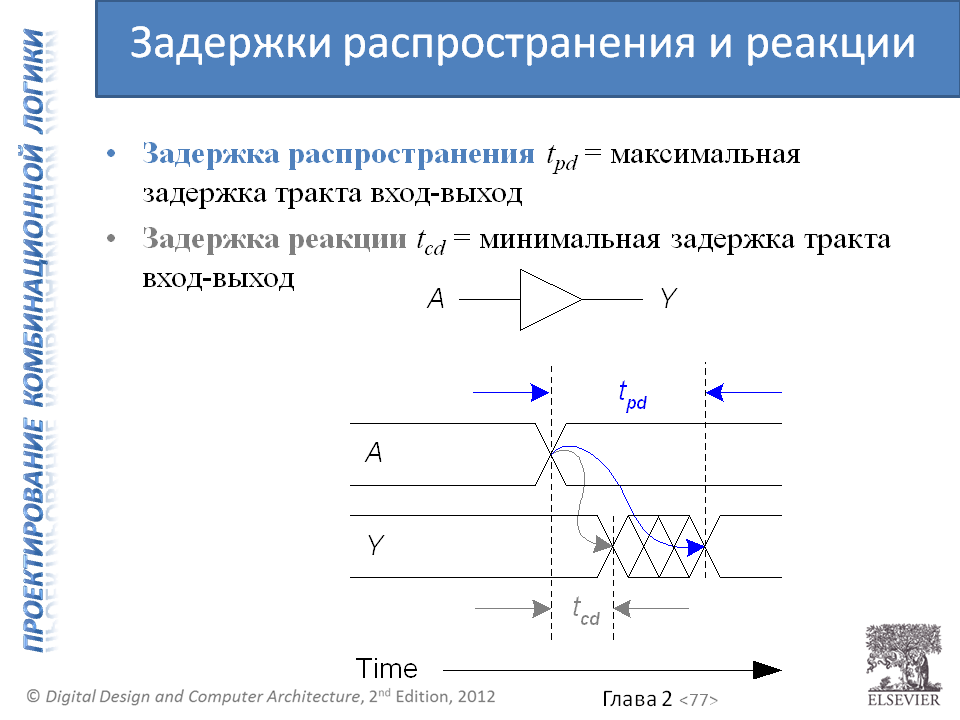

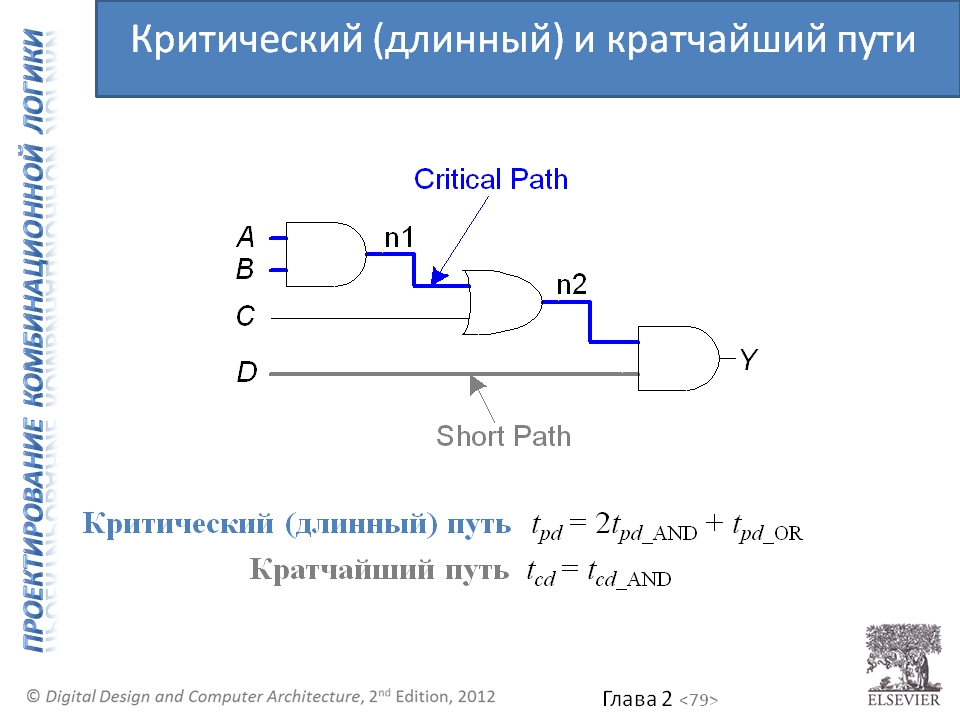

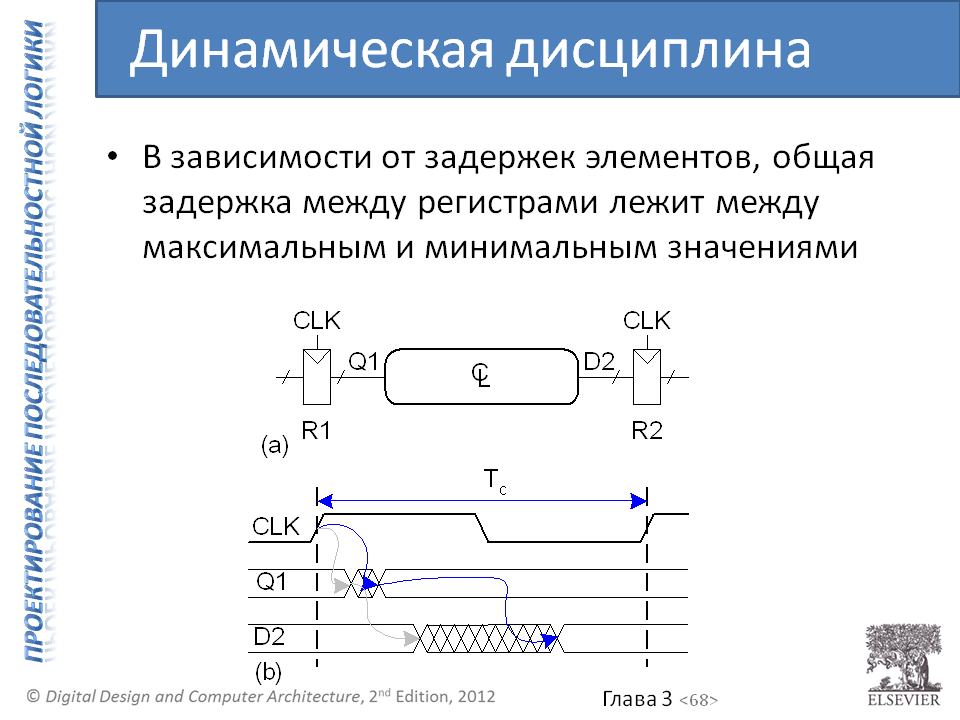

Es ist bedauerlich, dass der Manga nichts über Zeitverzögerungen in kombinatorischen Schaltkreisen und die Berechnung der maximalen Taktfrequenz sagt. Dies könnte hier an dieser Stelle eingefügt werden:

Ich hoffe, dass dieser Manga in Russland Nachfolger haben wird, die mit Ivan Tsarevich und Vasilisa the Beautiful eine Art Cartoon machen, der zu Verzögerungen bei der Verteilung und einem kritischen Pfad führen würde, zum Beispiel basierend auf Informationen aus dem Lehrbuch Harris & Harris. Hier sind die entsprechenden Folien aus zusätzlichen Materialien für das Lehrbuch:

Hier ist eine direkte Folie, die besagt, dass für fast alle Zustandselemente ein D-Trigger verwendet wird [mit Ausnahme von Fällen, in denen Anfänger überhaupt nicht auf einen Latch zum Empfangen eines Gate-Takts ohne Impulsstörung in Energiesparschaltungen stoßen - pegelsensitive D- Verriegelung für störungsfreie, getaktete Uhr, die in stromsparenden Designs verwendet wird

Denken Sie daran, dass Petzold für seine Einführung D-Latches verwendet hat, was falsch ist. Aber nicht nur Petzold macht hier Fehler. Ich habe einmal einen Beitrag in LiveJournal mit einem solchen Bild des Zählers unten vom Addierer und dem D-Trigger gemacht, wonach mir ein russischer Programmierer aus dem Bundesstaat Colorado zwei Tage später sagte, dass es einfacher sei, Zähler auf T-Triggern zu bauen. Ich sagte ihm, dass er sich korrekt an T-Trigger aus seiner Kindheit in den 1970er Jahren erinnerte, aber jetzt, im 21. Jahrhundert, bauen iPhone-Entwickler Zähler aus D-Triggern, weil die Zählersituation bei T-Triggern liegt, bei denen das Datensignal als Taktsignal verwendet wird passt nicht gut zur Analyse des Timings in Chips für Milliarden von Transistoren (wenn Sie mir nicht zustimmen, teilen Sie meine Meinung bitte mit Links zu ASIC-Bibliotheken von TSMC, Synopsys Design Compiler usw.):

Jetzt haben wir bereits eine Reihe von Bildern über die Arbeit eines zweistufigen (Master-Slave) D-Triggers mit Feen gesehen:

Mit einem leicht verständlichen Zeitdiagramm werden Daten nur zum Zeitpunkt einer positiven Flanke des D-Triggers aufgezeichnet, der Rest der Zeit werden sie ignoriert:

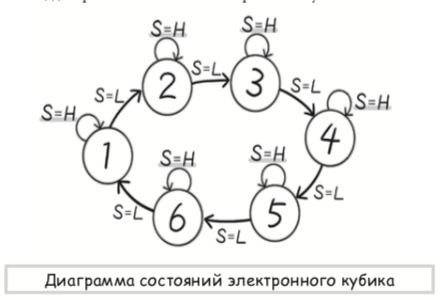

Nun geht der Manga zum Beispiel der Verwendung eines D-Triggers über, um eine einfache Zustandsmaschine zu bauen - ein Gerät zum Werfen elektronischer Knochen. Ehrlich gesagt bin ich mit diesem Teil des Buches nicht ganz zufrieden. Wir werden dies sagen, eine entartete endliche Zustandsmaschine, in der Zustände in einem Kreis laufen und um ein Bit gestoppt werden - die Stopptaste. Wenn das Beispielbuch mehrere Automaten enthalten würde, wäre alles in Ordnung, aber die Einstellung als einziges Beispiel ist falsch. Es wird nicht die gesamte Klasse von Problemen angezeigt, die mit Finite-State-Maschinen gelöst werden können. Im Folgenden werde ich zeigen, wie ich es ergänzen würde.

Zustandsdiagramm 0-1-2-3-4-5:

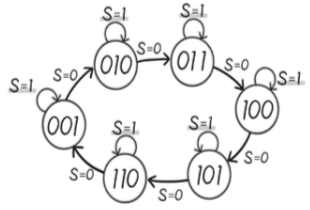

Binärzustände, die in drei D-Flip-Flops geschrieben sind:

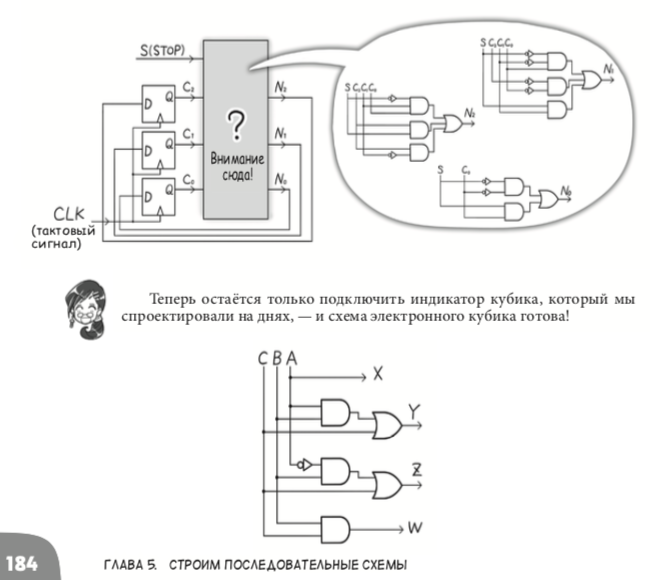

Ein kombinatorisches Schema, das vom alten einen neuen Zustand erhält:

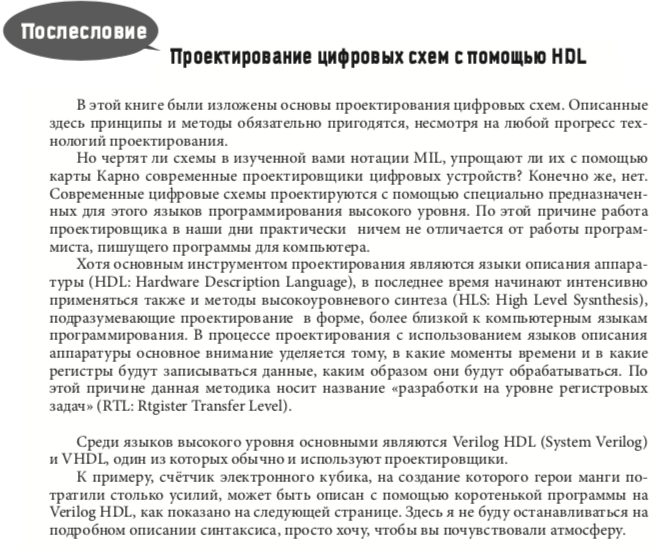

Und schließlich zeigt der Manga, wie man dasselbe Schema nicht durch Zeichnen mit der Maus auf dem Bildschirm, sondern durch Synthetisieren der Verilog-Hardwarebeschreibungssprache entwirft. Obwohl dieser Code wie ein Programmiersprachencode wie Pascal oder Java aussieht, hat dieser Code einen grundlegend anderen Charakter. Der Code auf dem Veril dient dazu, sich in eine Schaltung mit Drähten und Transistoren zu verwandeln. Und der Code in der Programmiersprache wird in eine Kette von Anweisungen, Nullen und Einsen kompiliert, die im Speicher gespeichert sind [es ist klar, dass sowohl Verilog als auch Java interpretiert werden können + der Code in Verilog kann in Nullen umgewandelt werden und Einsen für die FPGA-Konfiguration + Java kann in Verilog und übersetzt werden werden auch zu einem Diagramm, aber dies sind Details, die nicht zum anfänglichen Verständnis beitragen]:

Nun habe ich sozusagen das Beispiel über die Finite-State-Maschine I ergänzt. Ich würde ein interaktiveres Beispiel für eine endliche Zustandsmaschine machen, zum Beispiel unter Verwendung der Analogie zum sogenannten "chinesischen Raum". Hier ist meine Beschreibung des chinesischen Raums, die der Herausgeber vor einem Jahrzehnt in The New Times aus meinem Artikel gelöscht hat (in dieser Zeitschrift geht es nicht nur um Politik, sondern auch um beliebte Technologie):

1980 brachte einer der Kritiker der künstlichen Intelligenz, John Searle, ein elegantes Argument vor, das als "chinesisches Zimmer" bezeichnet wurde. Angenommen, es gab in Zukunft eine Version des Eliza-Programms, die so gut Chinesisch sprach, dass die Chinesen einen Computer nicht von einer Person unterscheiden konnten. Angenommen, jemand würde dieses Programm in ein dickes Buch mit mechanischen Anweisungen für eine Person kopieren. Wenn Sie das Zeichen A sehen und zuvor das Zeichen B gesehen haben, entfernen Sie das Zeichen C aus der Box. Jetzt stellen wir eine bestimmte Person, die kein Chinesisch kann, in einen geschlossenen Raum mit dieses Buch und wird ihn unter die Türschilder mit Hieroglyphen stecken, die Fragen auf Chinesisch enthalten. Nach den mechanischen Anweisungen aus dem Buch findet eine Person in einer Schachtel andere Schilder mit Hieroglyphen und schiebt sie zurück. Aus der Sicht eines externen Beobachters wird der Raum auf Chinesisch "verstehen" und "sprechen". Aber wer ist der Träger dieses Geistes? Immerhin versteht der Darsteller kein Chinesisch?

John McCarthy und andere Veteranen der künstlichen Intelligenz erklärten sofort, dass sich Vernunft und sogar Bewusstsein in einer „virtuellen Persönlichkeit“ oder in einem „Prozess“ manifestieren würden, der in diesem Raum durchgeführt wird. Eines der eleganten Argumente gegen John Searle wurde von den Philosophen Paul und Patricia Churchland vorgebracht. Wie wir aus der Physik wissen, ist Licht eine elektromagnetische Welle, argumentierte Churchlands. Angenommen, ein Skeptiker beginnt, einen Magneten mit seiner Hand zu bewegen, sieht das Licht nicht und behauptet, dass Licht unmöglich ist. Um das Licht zu erhalten, müssen Sie einen Magneten mit einer Geschwindigkeit von 450 Milliarden Hüben pro Sekunde bewegen. So würde rationales Bewusstsein, argumentierte Churchlands, im "chinesischen Raum" entstehen, wenn der Darsteller ausreichend agil wäre.

Es ist interessant, dass der ukrainische Science-Fiction-Autor Anatoly Dneprov das Analogon von „The Chinese Room“ in den 1950er Jahren in der Geschichte „The Game“ beschrieb.

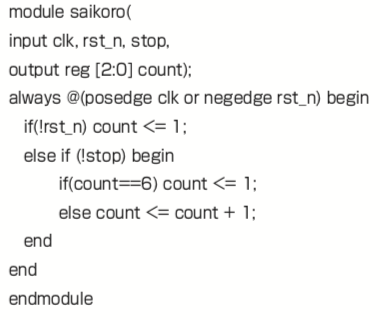

Also. Für meine eigenen Vorlesungen und Materialien habe ich ein Beispiel entwickelt, in dem eine Finite-State-Maschine (FSM) als Antwort auf eine Folge einer beliebigen Anzahl von Zeichen „Bär“ und „Baum“ mit dem Endzeichen „Wissenschaft“ eine Folge von Zeichen „Sibirien“ erzeugt. Dies ist das einfachste "chinesische Zimmer":

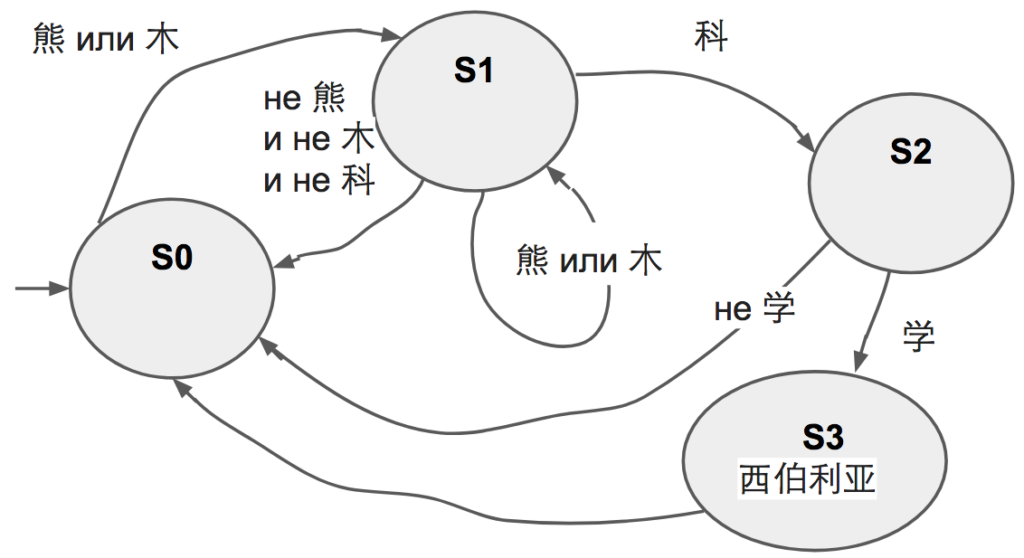

Hier ist ihr Zustandsdiagramm:

Aus diesem Diagramm können Sie eine Schaltung erstellen und auf einer Karte mit FPGA implementieren.

Neulich habe ich Auszüge aus diesem Manga von Amano Hideharu und Meguro Koji verwendet, als ich 150 Studenten von Kazan Innopolis einen Skype-Vortrag aus Kalifornien hielt. Die Schüler beginnen mit dem Studium der Computerarchitektur und müssen die Barriere des anfänglichen Missverständnisses der digitalen Logik überwinden. Dafür ist der Manga sehr gut, besonders wenn Sie ihn in Kombination mit Lehrbüchern wie Harris & Harris "Digital Circuitry and Computer Architecture" verwenden.

Hier ist das Video von dieser Vorlesung:

Folien für diese und die nächste Vorlesung können hier heruntergeladen werden:

http://bit.ly/2018-01-25-verilog-1-innopolis-yuri-panchulhttp://bit.ly/2018-02-01-verilog-2-innopolis-yuri-panchulNun haben viele Leser von Posts über FPGAs oft die Frage: "Warum ist das notwendig, weil es mehr Arbeiten auf Java gibt?"

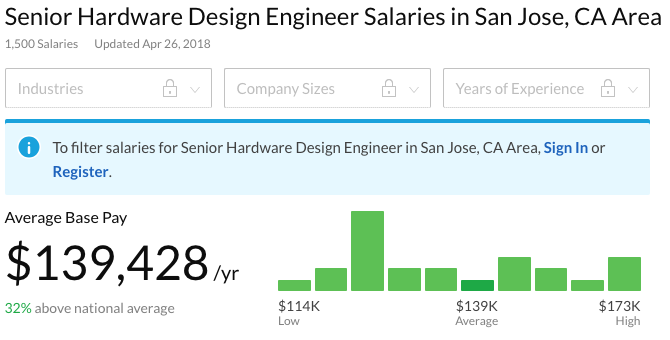

Dies kann beantwortet werden: Laut der Glassdoor-Website in San Jose, Kalifornien, werden Designer digitaler Schaltungen mehr geschätzt als Java-Entwickler:

Und wenn der Leser sagt: „Und was brauche ich San Jose? Ich bin in Russland und drohe nicht, nach San Jose zu gehen. “Sie können ein neues Beispiel dafür anführen, dass das Brautpaar aus St. Petersburg beim Intel InnovateFPGA-Wettbewerb in Europa den ersten Platz belegt hat, danach beim Weltfinale in San Jose den zweiten Platz belegt hat. Hier sitzen sie vor ein paar Tagen in Intels Büro in San Jose. Für das Projekt auf FPGA. Vielleicht hat Intel für ein Projekt auf Java jemanden mit der Preisverleihung nach San Jose gebracht, aber ich persönlich kenne solche Beispiele nicht.

Vladislav Sharshin, Andrey Papushin und Yelena Kirichenko -

www.innovatefpga.com/cgi-bin/innovate/teams.pl?Id=EM076