Moderne mikroelektronische Technologien - wie „Ten Little Indians“. Die Kosten für Entwicklung und Ausrüstung sind so hoch, dass bei jedem neuen Schritt jemand abfällt. Nach den Nachrichten über GlobalFoundries, die sich weigerten, 7 nm zu entwickeln, waren noch drei übrig: TSMC, Intel und Samsung. Und was genau sind „Designstandards“ und wo ist diese sehr geschätzte Größe von 7 nm? Und ist er überhaupt da?

Abbildung 1. Transistor Fairchild FI-100, 1964.Die allerersten seriellen MOS-Transistoren kamen 1964 auf den Markt und unterschieden sich, wie anspruchsvolle Leser aus der Zeichnung ersehen können,

fast nicht von mehr oder weniger modernen - abgesehen von der Größe (siehe Draht für Maßstab).

Warum die Größe von Transistoren reduzieren? Die naheliegendste Antwort auf diese Frage heißt Moores Gesetz und besagt, dass alle zwei Jahre die Anzahl der Transistoren auf einem Chip verdoppelt werden sollte, was bedeutet, dass die linearen Abmessungen der Transistoren um den Faktor zwei abnehmen sollten. "Muss" - nach den Beobachtungen von Gordon Moore (und einigen anderen Ingenieuren) in den siebziger Jahren. Nach dem Mooreschen Gesetz gibt es viele andere Faktoren, die die Roadmap für die ITRS-Mikroelektronik ausmachen. Die einfachste und gröbste Formulierung von Methoden zur Umsetzung des Moore'schen Gesetzes (auch als Dennard'sches Miniaturisierungsgesetz bekannt) ist, dass eine Erhöhung der Anzahl der Transistoren auf einem Chip nicht zu einer Erhöhung der Dichte des Stromverbrauchs führen sollte, dh bei einer Verringerung der Größe der Transistoren sollten die Versorgungsspannung und der Betriebsstrom proportional verringert werden.

Der Strom durch den MOS-Transistor ist proportional zum Verhältnis seiner Breite zu Länge, was bedeutet, dass wir den gleichen Strom aufrechterhalten können, wobei beide Parameter proportional reduziert werden. Darüber hinaus reduzieren wir durch Verringern der Größe des Transistors auch die Gatekapazität (proportional zum Produkt aus Kanallänge und -breite), wodurch die Schaltung noch schneller wird. Im Allgemeinen gibt es in einer digitalen Schaltung praktisch keinen Grund, Transistoren größer als die Mindestgröße zu machen. Als nächstes beginnen die Nuancen, dass in logischen p-Kanal-Transistoren normalerweise etwas breiter als n-Kanal-Transistoren sind, um den Unterschied in der Mobilität von Ladungsträgern zu kompensieren, und im Speicher im Gegensatz dazu sind n-Kanal-Transistoren breiter, so dass der Speicher normal über einen nicht komplementären Schlüssel geschrieben werden kann, aber es ist wirklich so Nuancen und global - je kleiner der Transistor - desto besser für digitale Schaltungen.

Aus diesem Grund war die Kanallänge in der Topologie der Mikroschaltung immer die kleinste Größe und die logischste Bezeichnung.

Es ist hier zu beachten, dass die obigen Überlegungen zur Größe für analoge Schaltungen nicht gelten. Zum Beispiel befindet sich derzeit auf dem zweiten Monitor meines Computers ein abgestimmtes Transistorpaar mit 150-nm-Technologie, 32 Stück mit einer Größe von jeweils 8/1 Mikrometern. Dies geschieht, um die Identität dieser beiden Transistoren trotz der technologischen Variation der Parameter sicherzustellen. Das Gebiet ist von untergeordneter Bedeutung.Technologen und Topologen haben das sogenannte Lambda-System mit typischen Topologiegrößen. Es ist sehr praktisch, um Design zu studieren (und wurde an der Universität von Berkeley erfunden, wenn ich mich nicht irre) und um Designs von Fabrik zu Fabrik zu übertragen. In der Tat ist dies eine Verallgemeinerung typischer Größen und technologischer Einschränkungen, aber ein wenig aufgeraut, so dass es in jeder Fabrik genau funktioniert. In ihrem Beispiel ist es zweckmäßig, die typischen Größen der Elemente im Chip zu betrachten. Die Prinzipien im Kern des Lambda-Systems sind sehr einfach:

- Wenn die Verschiebung von Elementen auf zwei verschiedenen photolithografischen Masken katastrophale Folgen hat (z. B. ein Kurzschluss), sollte der Größenbereich zur Vermeidung von Inkonsistenzen mindestens zwei Lambdas betragen.

- Wenn die Verschiebung von Elementen unerwünschte, aber keine katastrophalen Folgen hat, muss der Größenabstand mindestens ein Lambda betragen.

- Die minimal zulässige Größe der Fotomaskenfenster beträgt zwei Lambdas.

Aus dem dritten Absatz folgt insbesondere, dass Lambda in alten Technologien die Hälfte der Entwurfsnorm ist (genauer gesagt, die Transistorkanallänge und die Entwurfsnormen sind zwei Lambdas).

Abbildung 2. Ein Beispiel für eine Topologie, die von einem Lambda-System ausgeführt wird.Das Lambda-System funktionierte perfekt nach den alten Designstandards und ermöglichte es Ihnen, die Produktion bequem von Fabrik zu Fabrik zu verlagern, Lieferanten von Zweitchips zu organisieren und viel nützlichere Dinge zu tun. Mit zunehmender Konkurrenz und der Anzahl der Transistoren auf einem Chip bemühten sich die Fabriken jedoch, die Topologie etwas kompakter zu gestalten. Daher können Sie die Konstruktionsregeln für ein „sauberes“ Lambda-System nur noch in Situationen erfüllen, in denen Entwickler sie unter Berücksichtigung der Wahrscheinlichkeit der Produktion unabhängig aufrauen Chip in verschiedenen Fabriken. Im Laufe der Jahre hat die Industrie jedoch eine direkte Verbindung „Designstandards = Transistorkanallänge“ entwickelt, die erfolgreich bestand, bis die Transistoren mehrere zehn Nanometer erreichten.

Abbildung 3. Schematischer Ausschnitt des Transistors.Diese Abbildung zeigt einen SEHR vereinfachten Abschnitt eines herkömmlichen planaren (flachen) Transistors, der den Unterschied zwischen der topologischen Kanallänge (Ldrawn) und der effektiven Kanallänge (Leff) zeigt. Woher kommt der Unterschied?

In Bezug auf die Mikroelektronik wird die Photolithographie fast immer erwähnt, aber viel seltener sind andere, nicht weniger wichtige technologische Operationen: Ätzen, Ionenimplantation, Diffusion usw. usw. Für unser Gespräch mit Ihnen ist eine Erinnerung daran, wie Diffusion und Ionenimplantation funktionieren, nicht überflüssig.

Abbildung 4. Vergleich von Diffusion und Ionenimplantation.Mit der Diffusion ist alles einfach. Sie nehmen einen Siliziumwafer, auf den im Voraus (mit Hilfe der Fotolithografie) eine Zeichnung aufgebracht wird, die die Stellen, an denen die Verunreinigung nicht benötigt wird, mit Siliziumoxid bedeckt und die Stellen öffnet, an denen sie benötigt wird. Als nächstes müssen Sie die gasförmige Verunreinigung in dieselbe Kammer mit dem Kristall legen und auf eine Temperatur erwärmen, bei der die Verunreinigung beginnt, in Silizium einzudringen. Durch Einstellen der Temperatur und Dauer des Prozesses ist es möglich, die gewünschte Menge und Tiefe an Verunreinigungen zu erreichen.

Das offensichtliche Minus der Diffusion ist, dass die Verunreinigung in alle Richtungen auf die gleiche Weise in das Silizium eindringt, auf dieser Seite nach unten, wodurch die effektive Kanallänge verringert wird. Und wir sprechen jetzt über Hunderte von Nanometern! Während die Designstandards in zehn Mikrometern gemessen wurden, war alles in Ordnung, aber natürlich konnte dieser Zustand nicht lange anhalten, und die Diffusion wurde durch Ionenimplantation ersetzt.

Während der Ionenimplantation beschleunigt sich ein Verunreinigungsionenstrahl und wird auf einen Siliziumwafer gerichtet. In diesem Fall bewegen sich alle Ionen in eine Richtung, wodurch ihre Ausbreitung zu den Seiten praktisch ausgeschlossen ist. Theoretisch natürlich. In der Praxis breiten sich die Ionen dennoch etwas auseinander aus, wenn auch in viel kürzeren Abständen als während der Diffusion.

Wenn wir jedoch zum Transistormuster zurückkehren, werden wir sehen, dass der Unterschied zwischen der topologischen und der effektiven Kanallänge genau aufgrund dieses kleinen Kriechens beginnt. Sie könnte im Prinzip vernachlässigt werden, aber sie ist nicht der einzige Grund für den Unterschied. Es gibt immer noch kurze Kanaleffekte. Es gibt fünf davon, und auf verschiedene Weise ändern sie die Parameter des Transistors, wenn sich die Kanallänge verschiedenen physikalischen Einschränkungen nähert. Ich werde nicht alle beschreiben, sondern auf das für uns relevanteste eingehen - DIBL (Drain-Induced Barrier Lowering, Drain-induzierte Abnahme der potenziellen Barriere).

Um in die Senke zu gelangen, muss ein Elektron (oder Loch) die Potentialbarriere des Senken-pn-Übergangs überwinden. Die Gate-Spannung reduziert diese Barriere und steuert so den Strom durch den Transistor. Wir möchten, dass die Gate-Spannung die einzige Steuerspannung ist. Wenn der Transistorkanal zu kurz ist, beginnt der Drain-pn-Übergang leider, den Transistor zu beeinflussen, was zum einen die Porenspannung verringert (siehe Abbildung unten), und zum anderen wirkt sich die Spannung am Transistor nicht nur auf die Gate-Spannung aus , aber auch am Drain, weil die Dicke des Drain-pn-Übergangs proportional zur Spannung am Drain zunimmt und dementsprechend den Kanal verkürzt.

Abbildung 5. DIBL-Effekt (Drain-Induced Barrier Lowering).

Quelle - Wikipedia.Darüber hinaus führt eine Verringerung der Kanallänge dazu, dass Ladungsträger beginnen, frei von der Source zum Drain zu gelangen, den Kanal zu umgehen und einen Leckstrom (in der folgenden Abbildung schlechter Strom) zu erzeugen, der auch ein statischer Stromverbrauch ist, dessen Fehlen einer der wichtigen Gründe für den frühen Erfolg von CMOS war -Technologien, eher hemmend im Vergleich zu den bipolaren Konkurrenten dieser Zeit. Tatsächlich steht jedem Transistor in der modernen Technologie ein parallel stehender Widerstand, dessen Wert umso kleiner ist, je kleiner die Kanallänge ist.

Abbildung 6. Der Anstieg des statischen Verbrauchs aufgrund von Lecks in Kurzkanaltechnologien.

Quelle - Synopsys.Abbildung 7. Der Anteil des statischen Stromverbrauchs von Mikroprozessoren bei verschiedenen Entwurfsstandards.

Quelle - B. Dieny et. al., "Spin-Transfer-Effekt und seine Verwendung in Spintronic-Komponenten", International Journal of Nanotechnology, 2010Wie Sie in der obigen Abbildung sehen können, übersteigt der statische Verbrauch die Dynamik erheblich und ist ein wichtiges Hindernis für die Erstellung von Stromkreisen mit geringem Stromverbrauch, beispielsweise für tragbare Elektronik und das Internet der Dinge. Tatsächlich begann ungefähr zu der Zeit, als dies zu einem wichtigen Problem wurde, die Vermarktung von Muhlezh mit Designstandards, weil die Fortschritte in der Lithographie die Fortschritte in der Physik zu übertreffen begannen.

Um den unerwünschten Effekten des Kurzkanals bei Designstandards von 800 bis 32 Nanometern entgegenzuwirken, wurden viele verschiedene technologische Lösungen erfunden, und ich werde sie nicht alle beschreiben, da der Artikel sonst sehr unanständig wird, aber mit jedem neuen Schritt musste ich neue Lösungen einführen - zusätzliche Dotierung von Bereichen neben pn-Übergängen, Tiefen-Dotierung zur Vermeidung von Lecks, lokale Umwandlung von Silizium in Transistoren in Silizium-Germanium ... Es wurde kein einziger Schritt zur Reduzierung der Größe von Transistoren unternommen. ach so.

Figure 8. Die effektive Kanallänge in Technologien von 90 nm und 32 nm. Die Transistoren werden im gleichen Maßstab aufgenommen. Die Halbkreise in den Figuren sind eine Form der zusätzlichen schwachen Anpassung der Abflüsse (LDD, leicht dotierter Abfluss), um die Breite der pn-Übergänge zu verringern.

Quelle - Synopsys.Typische Metallisierungsgrößen und die Abstände zwischen Elementen während des Übergangs von 90 nm auf etwa 28 nm nahmen proportional zu einer Verringerung des Konstruktionscodes ab, dh die typische Größe der nächsten Generation betrug 0,7 gegenüber der vorherigen (so dass nach dem Moore'schen Gesetz eine zweifache Flächenverringerung vorliegt). Gleichzeitig verringerte sich die Kanallänge bestenfalls um 0,9 gegenüber der vorherigen Generation, und die effektive Kanallänge änderte sich praktisch überhaupt nicht. Aus der obigen Abbildung ist klar ersichtlich, dass sich die linearen Abmessungen der Transistoren von 90 nm auf 32 nm überhaupt nicht dreimal geändert haben, und alle Spiele der Technologen befassten sich mit der Verringerung der Verschlussüberlappung und der dotierten Bereiche sowie mit der Kontrolle statischer Lecks, die nicht durchgeführt werden durften Der Kanal ist kürzer.

Infolgedessen wurden zwei Dinge klar:

- unter 25-20 nm zu gehen, ohne dass ein technologischer Durchbruch nicht funktioniert;

- Für Vermarkter ist es zunehmend schwieriger geworden, ein Bild des technologischen Fortschritts mit dem Moore'schen Gesetz zu zeichnen.

Das Mooresche Gesetz ist im Allgemeinen ein kontroverses Thema, da es kein Naturgesetz ist, sondern eine empirische Beobachtung einiger Fakten aus der Geschichte eines bestimmten Unternehmens, die auf den zukünftigen Fortschritt der gesamten Branche hochgerechnet werden. Tatsächlich ist die Popularität von Moores Gesetz untrennbar mit Intel-Vermarktern verbunden, die es zu ihrem Banner gemacht und die Branche viele Jahre lang vorangetrieben haben und sie gezwungen haben, Moores Gesetz einzuhalten, wo es sich vielleicht ein wenig lohnen würde, darauf zu warten.Wie haben Vermarkter aus der Situation herausgefunden? Sehr elegant.

Die Länge des Transistorkanals ist gut, aber wie können Sie die Verstärkung in der Fläche daraus abschätzen, die den Übergang zu neuen Designstandards ermöglicht? Vor langer Zeit nutzte die Industrie den Bereich einer Sechs-Transistor-Speicherzelle, dem beliebtesten Mikroprozessor-Baustein. Es sind diese Zellen, die normalerweise aus einem Cache-Speicher und einer Registerdatei bestehen, die einen halben Kristall belegen können, und deshalb werden das Schema und die Topologie einer Sechs-Transistor-Zelle immer sorgfältig bis an die Grenzen geleckt (oft spezielle Leute, die genau das tun), also ist dies eine wirklich gute Maßnahme Packungsdichte.

Figure 9. Schema einer statischen Speicherzelle mit sechs Transistoren.Abbildung 10. Verschiedene Topologieoptionen für eine statische Speicherzelle mit sechs Transistoren. Quelle - G. Apostolidis et. al., „Entwurf und Simulation von 6T-SRAM-Zellarchitekturen in 32-nm-Technologie“, Journal of Engineering Science and Technology Review, 2016Bei der Beschreibung von Technologien wurde die Anzahl der Entwurfsstandards lange Zeit von der zweiten Zahl begleitet - dem Bereich der Speicherzelle, der theoretisch aus der Kanallänge abgeleitet werden sollte. Und dann gab es eine interessante Substitution von Konzepten. Zu einer Zeit, als die direkte Skalierung nicht mehr funktionierte und die Kanallänge nach dem Moore'schen Gesetz nicht mehr alle zwei Jahre abnahm, vermuteten Vermarkter, dass es nicht möglich war, den Speicherzellenbereich aus den Entwurfsnormen abzuleiten, sondern die Anzahl der Entwurfsnormen aus dem Speicherzellenbereich abzuleiten!

Das heißt natürlich: „Früher hatten wir eine Kanallänge von 65 nm und eine Speicherzellenfläche von X, und jetzt beträgt die Kanallänge 54 nm, aber wir haben die Metallisierung zusammengedrückt, und jetzt ist die Zellfläche X / 5 geworden, was ungefähr einem Übergang von 65 auf 28 nm entspricht. Sagen wir also allen, dass wir Designstandards von 28 nm haben und wir niemandem von der Kanallänge von 54 nm erzählen werden. " Fairerweise ist auch die "stechende Metallisierung" eine wichtige Errungenschaft, und für einige Zeit nach dem Beginn von Problemen mit der Miniaturisierung der Transistoren selbst entsprachen die minimale Metallisierungsbreite, die Größe des Kontakts zum Transistor oder eine andere Zahl in der Topologie den angegebenen Entwurfsstandards. Aber dann begannen die Tänze mit FinFET-Transistoren, bei denen die Schlüsseldimensionen nichts mit der Auflösung der Lithographie, den Miniaturisierungsraten der Transistoren und allem anderen zu tun hatten, und der Speicherzellenbereich blieb die einzige normale Zahl, auf deren Grundlage wir jetzt über „10“ informiert sind. 7 "und" 5 "Nanometer.

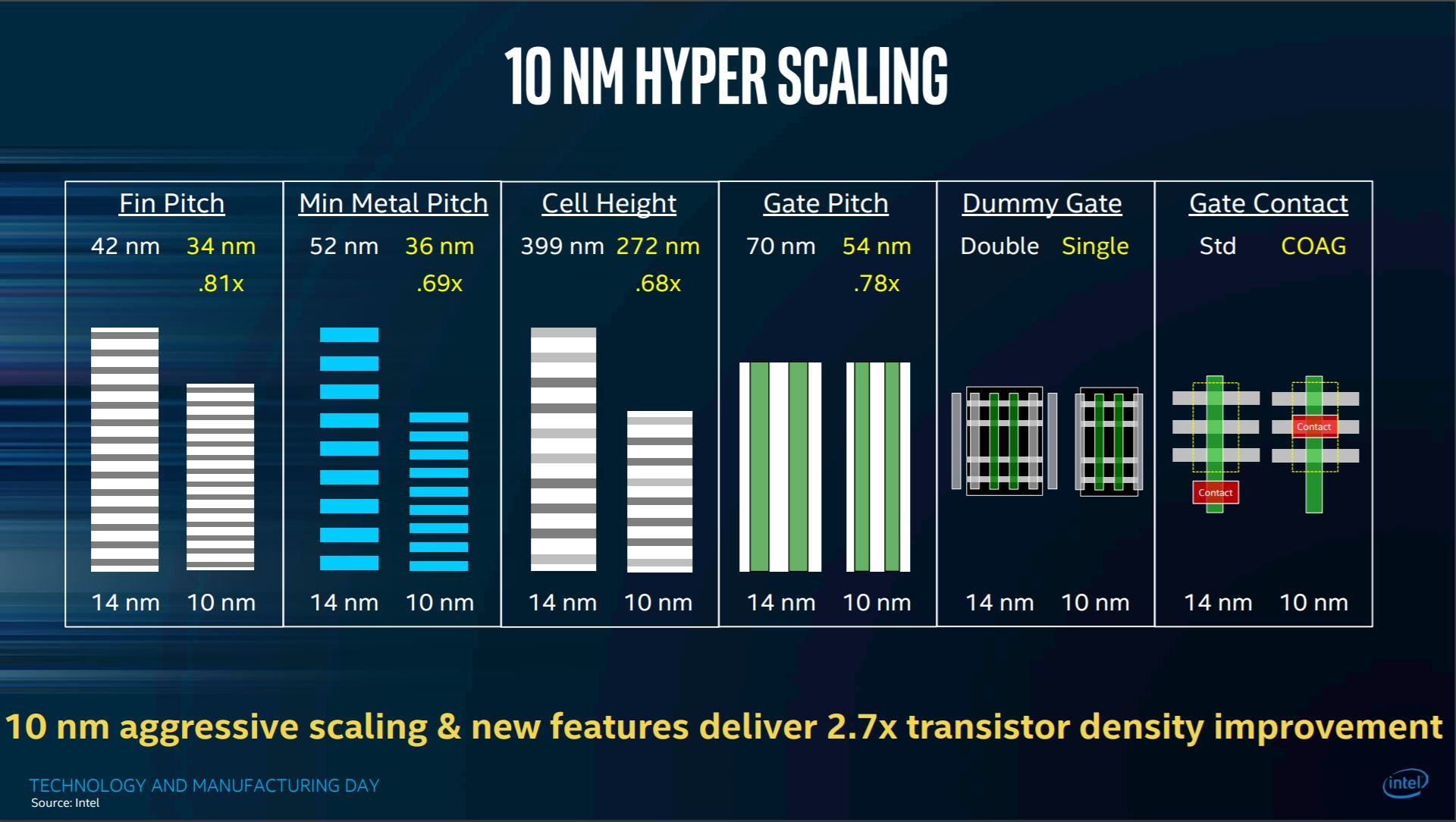

Quelle - Intel.Hier ist ein gutes Beispiel für diese „neue Skalierung“. Es wird gezeigt, wie sich die charakteristischen Größen in der Speicherzelle geändert haben. Viele Parameter, aber kein Wort über die Länge und Breite des Transistorkanals!

Wie haben sie das Problem der Unmöglichkeit gelöst, die Länge des Kanals zu reduzieren und die Leckage der Technologie zu kontrollieren?

Sie fanden zwei Wege. Die erste ist in der Stirn: Wenn die Ursache für Undichtigkeiten eine große Implantationstiefe ist, reduzieren wir sie, vorzugsweise radikal. Die SIC-Technologie (Silicon on a Insulator) ist seit langem bekannt (und wurde in all den Jahren aktiv eingesetzt, z. B. in 130-32-nm-AMD-Prozessoren, 90-nm-Sony Playstation 3-Set-Top-Box-Prozessoren sowie in der Hochfrequenz-, Leistungs- oder Weltraumelektronik) Mit einem Rückgang der Designstandards bekam sie einen zweiten Wind.

Abbildung 12. Vergleich von Transistoren, die mit herkömmlichen volumetrischen und FDSOI-Technologien (Full Depleted SOI) hergestellt wurden.

Quelle - ST Mikroelektronik .Wie Sie sehen können, ist die Idee mehr als elegant - Oxid befindet sich unter einer sehr dünnen aktiven Schicht, wodurch der schädliche Leckstrom an der Rebe beseitigt wird! Gleichzeitig nimmt aufgrund einer Verringerung der Kapazität von pn-Übergängen (vier der fünf Seiten des Abflusswürfels wurden entfernt) die Geschwindigkeit zu und der Stromverbrauch ab. Aus diesem Grund wird die FDSOI 28-22-20 nm-Technologie jetzt aktiv als Plattform für das Internet der Dinge beworben - Mikrochips werden tatsächlich um ein Vielfaches, wenn nicht sogar um eine Größenordnung reduziert. Und doch erlaubt dieser Ansatz in Zukunft, den herkömmlichen Flachtransistor auf ein Niveau von 14-16 nm zu skalieren, was die volumetrische Technologie nicht mehr zulässt.

Trotzdem fällt FDSOI nicht besonders unter 14 nm, und die Technologie weist auch andere Probleme auf (zum Beispiel die schrecklich hohen Kosten von SOI-Substraten), mit denen die Industrie zu einer anderen Lösung kam - FinFET-Transistoren. Die Idee eines FinFET-Transistors ist auch ziemlich elegant. Wollen wir, dass der größte Teil des Raums zwischen Drain und Source vom Verschluss gesteuert wird? Lassen Sie uns diesen Raum also von allen Seiten mit einem Verschluss umgeben! Nun, nicht alle, drei werden ausreichen.

Abbildung 13. FinFET-Struktur.

Quelle - A. Tahrim et al., „Design und Leistungsanalyse von 1-Bit-FinFET-Volladdiererzellen für den Unterschwellenbereich bei 16 nm Prozesstechnologie“, Journal of Nanomaterials, 2015Abbildung 14. Vergleich des Stromverbrauchs verschiedener Addiereroptionen für planare Transistoren und für FinFET.

Quelle - A. Tahrim et al., „Design und Leistungsanalyse von 1-Bit-FinFET-Volladdiererzellen für den Unterschwellenbereich bei 16 nm Prozesstechnologie“, Journal of Nanomaterials, 2015Beim FinFET ist der Kanal nicht flach und befindet sich direkt unter der Oberfläche des Substrats, sondern bildet eine vertikale Rippe (Fin ist die Rippe), die über die Oberfläche hinausragt und an drei Seiten von einem Verschluss umgeben ist. Somit wird der gesamte Raum zwischen dem Drain und der Source durch einen Verschluss gesteuert, und statische Lecks werden stark reduziert. Die ersten FinFETs, die in Massenproduktion hergestellt wurden, waren Intel mit Designstandards von 22 nm, der Rest wurde von anderen Top-Herstellern herangezogen, darunter ein KNI-Apologet wie Global Foundries (ehemals AMD).

Die Vertikalität des Kanals in FinFET ermöglicht es Ihnen unter anderem, Zellenfläche einzusparen, da FinFET mit einem breiten Kanal in der Projektion ziemlich eng ist, was wiederum den Vermarktern bei ihren Geschichten über die Fläche der Speicherzelle und deren zweifache Abnahme mit jeder neuen half Schritt "Designstandards", nicht mehr an die physikalischen Abmessungen des Transistors gebunden.Abbildung 15. Topologien verschiedener Optionen für Speicherzellen (5T-9T) in der Technologie mit FinFET. Quelle - M. Ansari et. al., "Eine 7T-SRAM-Zelle nahe der Schwelle mit hohen Schreib- und Lesespannen und geringer Schreibzeit für FinFET-Technologien unter 20 nm", VLSI Journal on Integration, Band 50, Juni 2015.Hier sind Beispiele für verschiedene Optionen für Speicherzellen in der Technologie mit FinFET. Sehen Sie, wie die geometrische Breite des Kanals viel kleiner als die Länge ist? Sie können auch sehen, dass trotz aller Störungen das Lambda-System unter Topologen immer noch für quantitative Schätzungen verwendet wird. Und was ist mit den absoluten Zahlen?Abbildung 16. Einige Größen von Transistoren in 14-16-nm-Technologien.

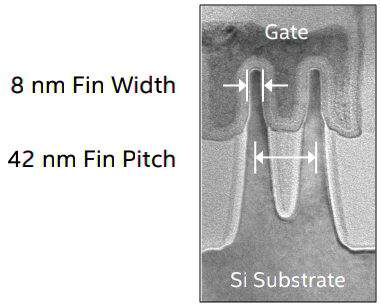

Quelle - das Konferenzprotokoll der ConFab 2016.Wie aus der Figur ersichtlich ist, ist die topologische Kanallänge in 16 nm FinFET-Technologien immer noch größer als 20-25 nm, die oben erwähnt wurden. Und das ist logisch, weil sich die Physik nicht täuschen lässt. Eine andere, interessantere Schlussfolgerung kann aus derselben Abbildung gezogen werden: Wenn Sie genau hinschauen, wird klar, dass die in Transistoren verfügbare Mindestgröße nicht die Kanallänge, sondern die Rippenbreite ist. Und hier erwartet uns eine lustige Entdeckung: Die Lamellenbreite in der Intel-Prozesstechnologie von 16 nm beträgt (Trommelwirbel!) ACHT Nanometer. Abbildung 17. Lamellenabmessungen in der 14-nm-Intel-Prozesstechnologie.

Abbildung 17. Lamellenabmessungen in der 14-nm-Intel-Prozesstechnologie.

Quelle - wikichip.orgWie Sie sehen können, haben sich hier Vermarkter, die an die Größe der Speicherzelle gebunden sind, getäuscht und sind nun gezwungen, die Zahl mehr auszusprechen, als sie könnten. Unter den Bedingungen einer grundlegenden Änderung der Struktur des Transistors und der Erwartung der Benutzer, eine Art Metrik zu hören, war die Verwendung einer Metrik, die die Packungsdichte widerspiegelt, wahrscheinlich die einzig richtige Entscheidung, und die Vermarkter hatten letztendlich Recht, obwohl dies manchmal dazu führt lustige Situationen, in denen die gleichen Designstandards in verschiedenen Unternehmen unterschiedlich genannt werden. Wenn Sie beispielsweise die Nachricht lesen, dass TSMC bereits 7 nm auf den Markt gebracht hat und Intel den Produktionsstart von 10 nm erneut verzögert, sollten Sie bedenken, dass 7 nm TSMC und 10 nm Intel tatsächlich dieselben Designstandards in Bezug auf haben und Packungsdichte und die Größe der einzelnen Transistoren.Was weiter?

Tatsächlich weiß es niemand. Moores Gesetz hat sich vor einiger Zeit erschöpft, und wenn vor zehn Jahren die Antwort auf die Frage "Was kommt als nächstes?" In den Berichten der Forschungszentren wurde zunehmend festgestellt, dass vielversprechende Entwicklungen aufgegeben werden müssen, da sie sich als äußerst schwierig umzusetzen erweisen. Dies ist bereits bei Wafern mit einem Durchmesser von 450 Millimetern geschehen, dies ist teilweise bei der EUV-Lithographie der Fall (die Wissenschaftler zwanzig Jahre lang betrieben haben), und dies wird wahrscheinlich bei Transistoren auf Graphen- und Kohlenstoffnanoröhren der Fall sein. Ein weiterer technologischer Durchbruch ist erforderlich, aber der Weg dorthin ist leider noch nicht sichtbar. Es kam zu dem Punkt, dass der neue Direktor von TSMC Mark Liu anriefDie vielversprechendste Richtung bei der Entwicklung der mikroelektronischen Technologie ist nicht die Verringerung der Größe von Transistoren, sondern die 3D-Integration. Die „echte“ 3D-Integration, anstatt mehrere Chips in einem Paket zu kombinieren, wird in der Tat ein großer Meilenstein in der Entwicklung der Mikroelektronik sein, aber Moores Gesetz als Gesetz zur Reduzierung der Größe von Transistoren scheint vollständig gestorben zu sein.