Die Quad Data Rate (QDR-IV) ist ein Hochleistungsspeicherstandard für Netzwerkanwendungen und ideal für die nächste Generation von Netzwerkgeräten, Kommunikationsgeräten und Computersystemen.

QDR-IV SRAM verfügt über eine integrierte Fehlererkennungs- und -korrektureinheit (ECC), um die Datenintegrität sicherzustellen. Dieses Gerät kann alle Einzelbit-Speicherfehler verarbeiten, einschließlich solcher, die durch kosmische Strahlung und Alpha-Partikel verursacht werden. Infolgedessen haben Speichermodule eine Programmfehlerrate (SER) von nicht mehr als 0,01 Fehlern / MB. QDR-IV ist mit einer programmierbaren Adressparitätsfunktion ausgestattet, die die Datenintegrität auf dem Adressbus sicherstellt.

Besonderheiten des QDR-SRAM-Speichers:

- Das integrierte Fehlerkorrekturmodul stellt die Datenintegrität sicher und eliminiert Softwarefehler

- Die Module sind in zwei Versionen erhältlich: QDR-IV HP (Datenrate 1334 Mtrans / s) und QDR-IV XP (Datenrate 2132 Mtrans / s)

- Zwei unabhängige bidirektionale DDR1-Speicherdatenports

- Businversionsfunktion zur Rauschunterdrückung beim Anschließen von Eingangs- und Ausgangsleitungen

- Das integrierte Verhandlungsschema (ODT) reduziert die Komplexität der Platine

- Schräglauftraining zur Verbesserung des Timings der Signalerfassung

- E / A-Signalstärke: 1,2 V bis 1,25 V (Hochgeschwindigkeits-Transceiver-Logik (HSTL) / Terminierte Logik (SSTL)), 1,1 V bis 1,2 V (POD2)

- 361-poliges FCBGA3-Gehäuse

- Busbreite: x18, x36 Bit

Einführung

Der DDRx-Assistent ist ein benutzerfreundliches Tool in HyperLynx, mit dem Sie zeitliche Wellenformen stapelweise steuern und die Signalintegrität von Standard-DDR-JEDEC-Protokollen analysieren können. Der DDRx-Assistent kann sowohl in der Phase der vor-topologischen Analyse gemäß dem Was-wäre-wenn-Szenario als auch auf einer vollständig verfolgten Karte gestartet werden. Darüber hinaus können Sie mit dem Tool die meisten Modellformate importieren, die von großen Chiplieferanten erstellt wurden.

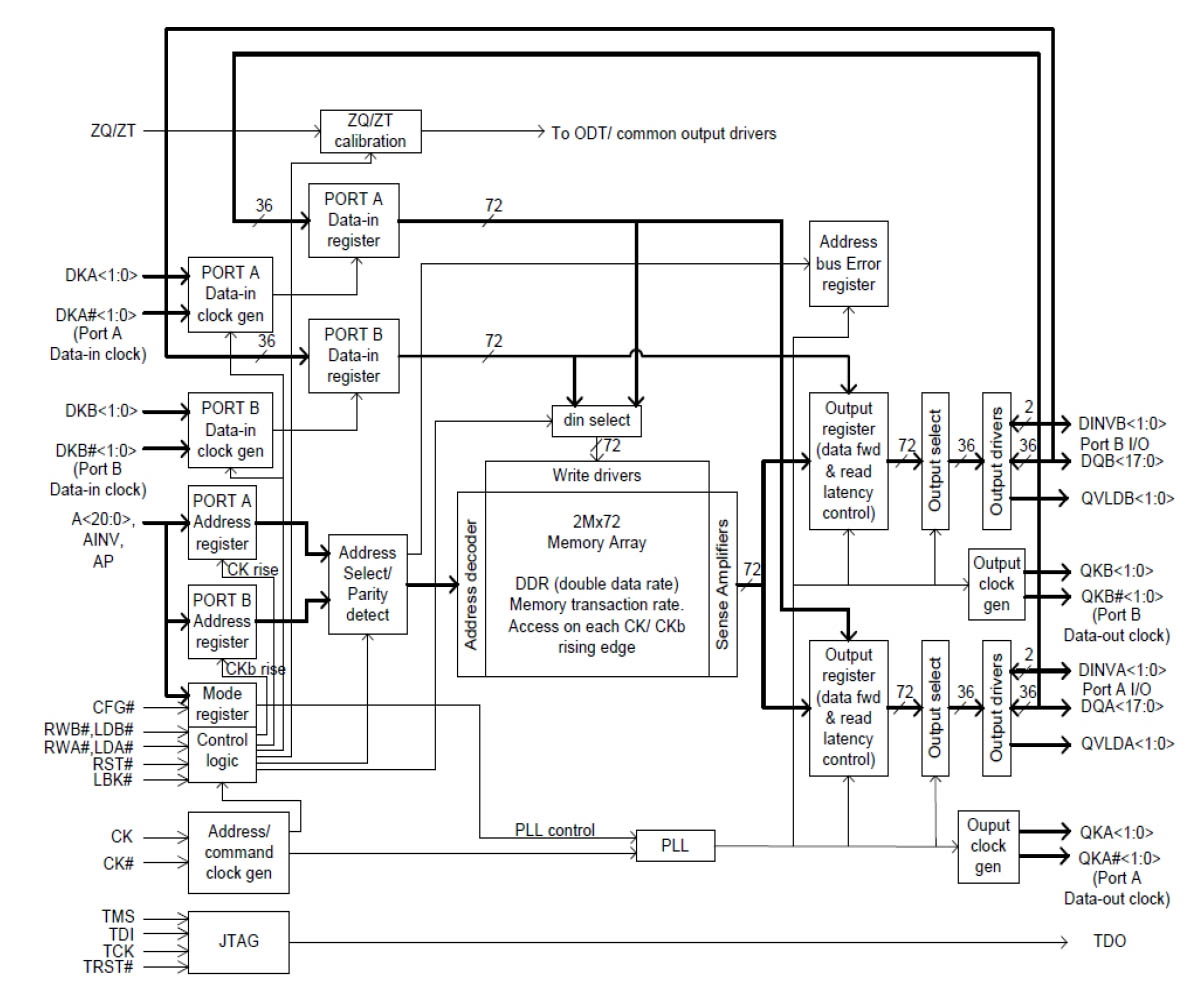

Mit dem DDRx-Assistenten können Sie alle Bits des Speicherbusses auf Übereinstimmung mit der Signalintegrität sowie auf Einhaltung der Anforderungen für die Synchronisation zwischen Signalen überprüfen. In diesem Artikel wird die Verwendung des interaktiven Assistenten zur Analyse von Projekten zur Implementierung des QDR4-Protokolls beschrieben (Abb. 1).

Abb. 1. Die interne Architektur von QDR am Beispiel des Moduls CY7C4142KV13 (anklickbar)

Abb. 1. Die interne Architektur von QDR am Beispiel des Moduls CY7C4142KV13 (anklickbar)Schauen Sie sich zuerst QDR-IV in HyperLynx DDRx WIZARD an

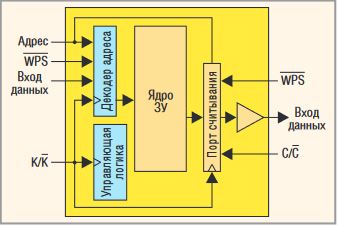

Das QDR-IV-Protokoll definiert zwei unidirektionale Paare eines Daten-Strobe-Signals: eines zum Lesen von Daten, das andere zum Schreiben, die voneinander unabhängige Operationen und gleichzeitige Lese- und Schreiboperationen unterstützen, und die Ports können mit unterschiedlichen Frequenzen arbeiten (Abb. 2). Damit ist das Risiko einer Fehlfunktion vollständig ausgeschlossen.

Abb. 2. Verfügbarkeit separater Lese- und Schreibports in der QDR-SRAM-Architektur

Abb. 2. Verfügbarkeit separater Lese- und Schreibports in der QDR-SRAM-ArchitekturFür dieses Protokoll verwendet der DDRx-Assistent separate Gates zum Lesen und Schreiben von Daten. QDR IV wird normalerweise unter Verwendung eines x36- oder x18-Bit-Busses implementiert (siehe Fig. 3a und 3b).

Der DDRx-Assistent aktiviert die QDR-IV-Simulation in drei Schritten:

- Überprüfung des Datenlesens

- Datensatzprüfung

- Adress- / Steuerbusprüfung

Da Adress- / Steuerbusprüfungen unabhängig von Datenlese- / Schreibprüfungen durchgeführt werden können, können Sie Zeit sparen, indem Sie diesen Schritt mit einem der Datentestschritte kombinieren. Im Folgenden werden alle drei Szenarien für diese Tests beschrieben.

Technologische Merkmale

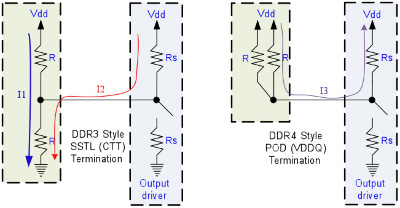

QDR-IV unterstützt die POD-Technologie (Pseudo Open Drain) und die Terminierungslogik SSTL (Stub Series Terminated Logic) (Abbildung 4).

Abb. 4. Unterschiede zwischen POD und SSTL

Abb. 4. Unterschiede zwischen POD und SSTLWählen Sie unabhängig vom verwendeten Logikstandard

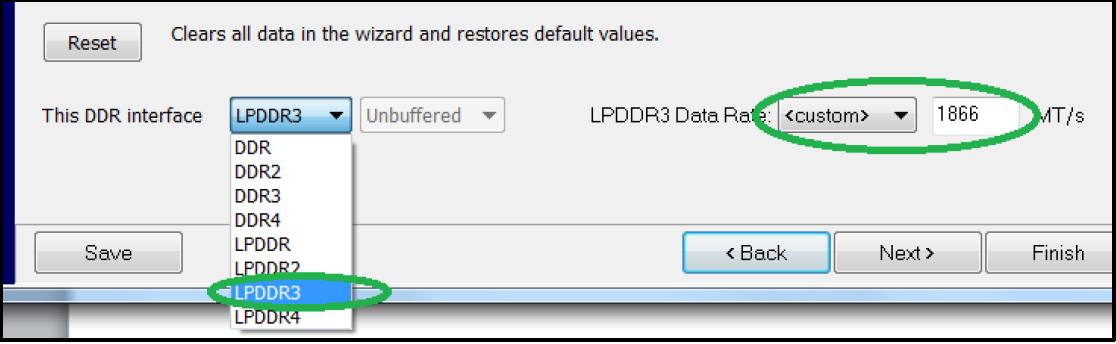

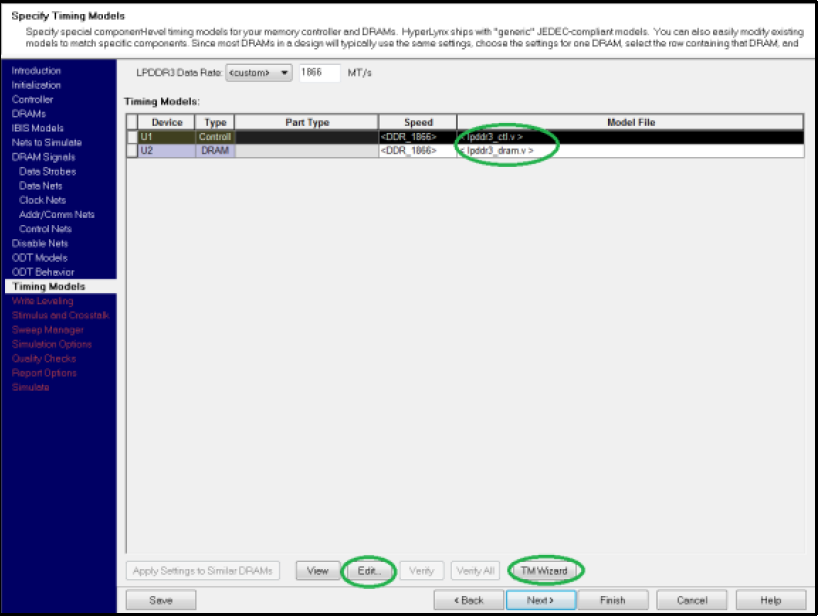

LPDDR3 als Technologie (Abb. 5), da das

Vref-Training nicht unterstützt wird, wie dies beim POD-Modul des DDR4 der Fall ist. Stattdessen werden Vref- und Vinh / Vinl-Festwerte verwendet, ähnlich wie bei DDR3 und LPDDR3. Da QDR-IV für Adressensignale wie LPDDR3 eine doppelte Datenrate verwendet, wird empfohlen, diese Option auszuwählen. Geben Sie als Nächstes die Benutzerdatenübertragungsrate ein, z. B. 1866 MT / s oder 2133 MT / s, wobei MT / s die Anzahl der Megatransfers pro Sekunde (Megatransfers pro Sekunde) ist.

Abb. 5. Die Wahl der Standardlogik

Abb. 5. Die Wahl der StandardlogikDatensignal: Lesevorgang

Für Datensignal-Leseoperationen steuert der DRAM die DQ-Signale in Verbindung mit den Differenz-Strobe-QK-Signalen. Somit konzentriert sich der Aufbau auf den Datenlesevorgang und weist dem entsprechenden QK-Gatter die erforderlichen Schaltungen (Signale) zu.

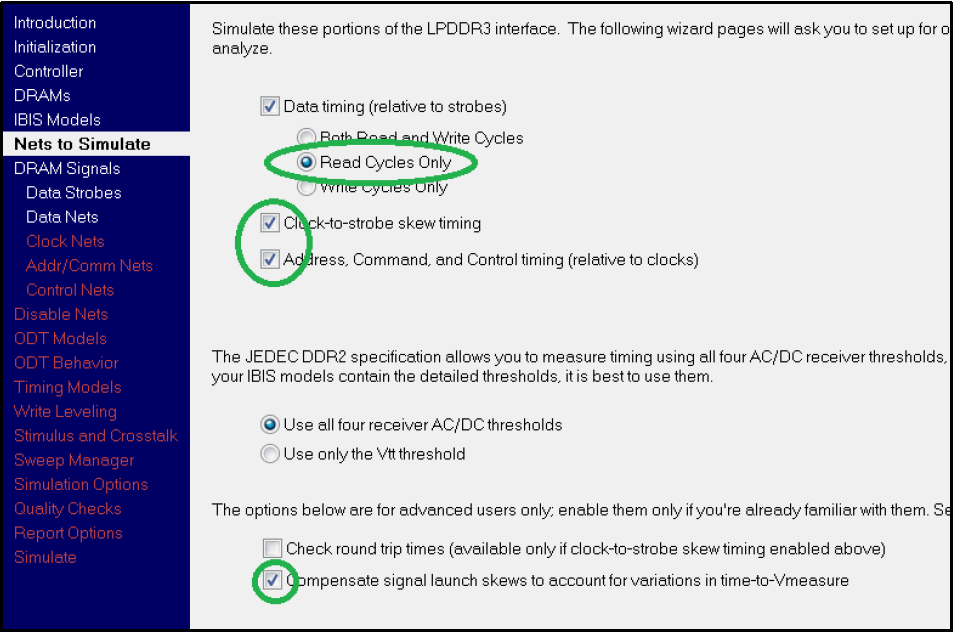

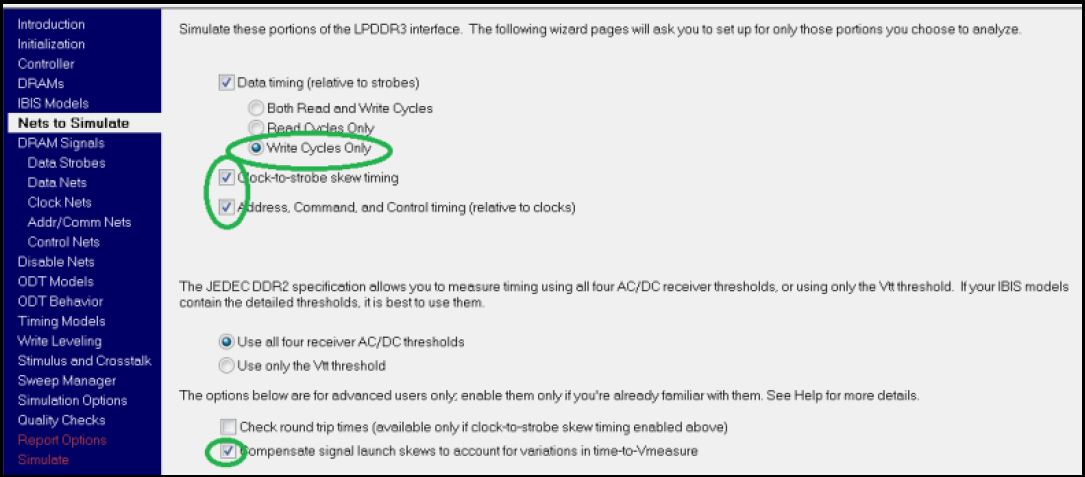

Aktivieren Sie im Abschnitt

Zu simulierende Netze (Abbildung 6) das Kontrollkästchen „

Nur Lesezyklen “. Die

Kontrollkästchen Clock-to-Strobe und Address sind optional.

Überprüfen Sie außerdem die Installation der

Startversuche für das

Compensate-Signal, um Abweichungen im Kontrollkästchen für die

Zeit bis zur Messung zu berücksichtigen .

Abb. 6. Daten lesen

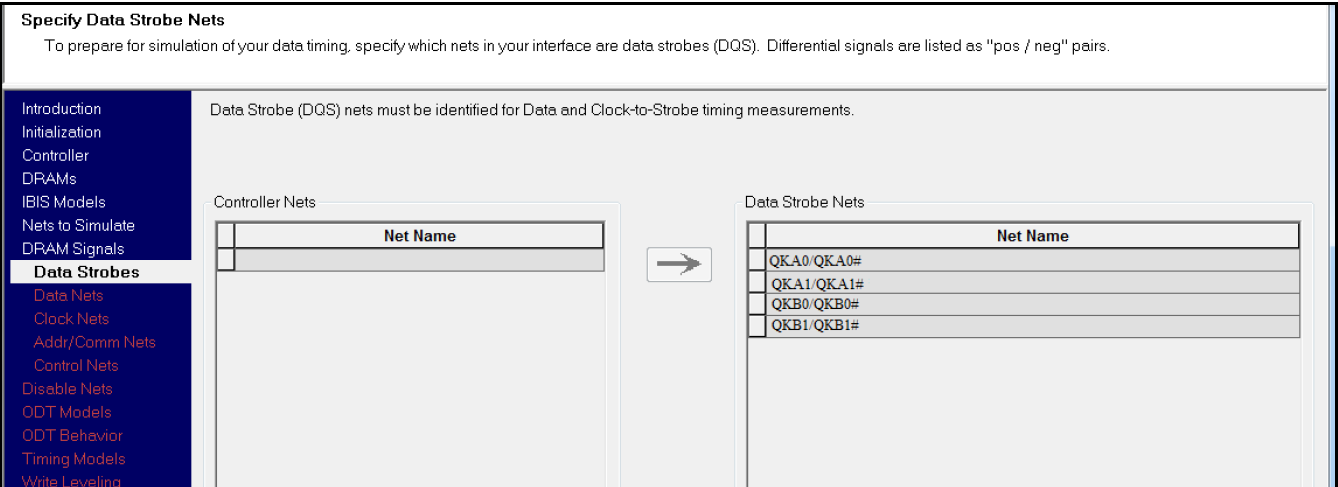

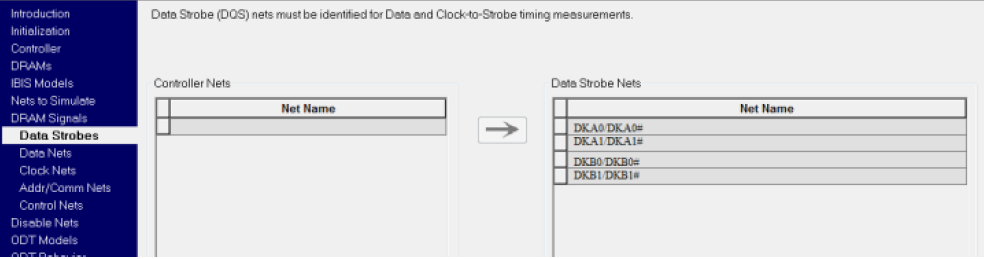

Abb. 6. Daten lesenStellen Sie sicher, dass alle erforderlichen Datenblitze ausgewählt sind (Abbildung 7).

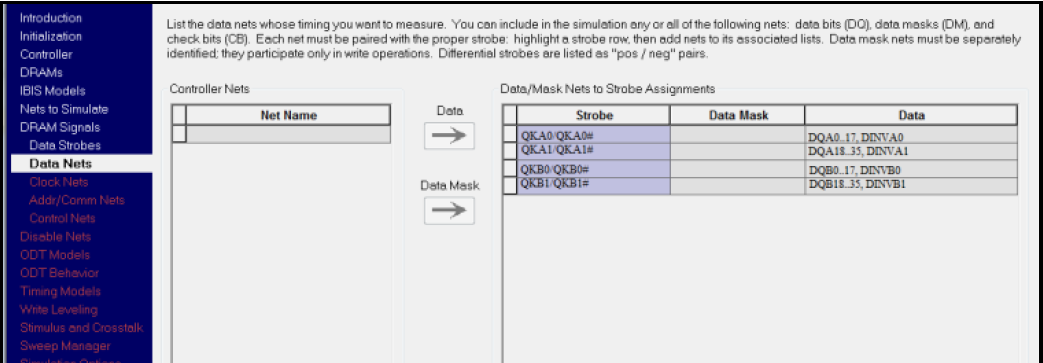

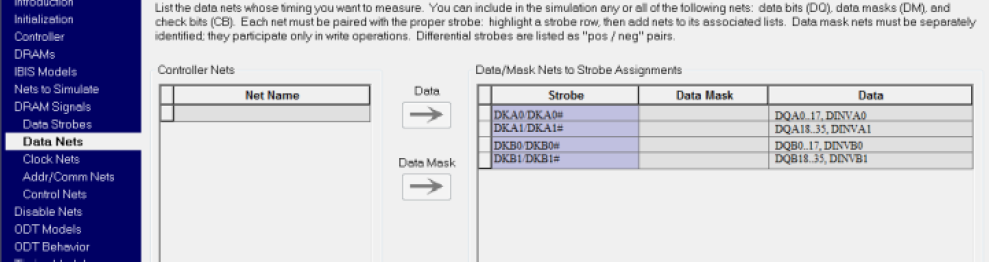

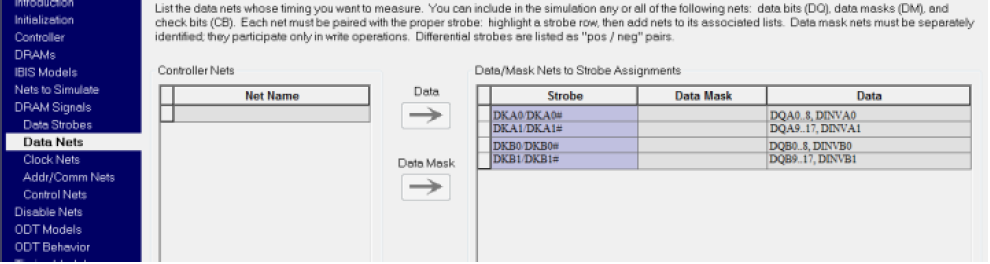

Überprüfen Sie im Abschnitt

Datennetze , ob jedes Signal mit jedem Gate korrekt übereinstimmt. Bitte beachten Sie, dass die Signale für die x18- und x36-Bit-Busse unterschiedlich sind. Stellen Sie daher sicher, dass die Pinbelegung für Ihren speziellen Fall geeignet ist (Abb. 8a und 8b).

Abb. 7. Datenblitz lesen

Abb. 7. Datenblitz lesen Abb. 8a. Signalgruppe für 36-Bit-Bus

Abb. 8a. Signalgruppe für 36-Bit-Bus Abb. 8b. Signalgruppe für den 18-Bit-Bus

Abb. 8b. Signalgruppe für den 18-Bit-BusDer parallele Bustest wird normalerweise durchgeführt, indem die Zeit zwischen dem Blitz und dem Signal eingestellt / gehalten wird. Alle diese Anforderungen sowie andere temporäre Werte werden vom DDRx-Assistenten benötigt, um die Ergebnisse zu überprüfen. Diese Werte können von Mikrochip zu Mikrochip unterschiedlich sein. Daher wird empfohlen, Werte einzugeben, die für ein bestimmtes Speichergerät gelten. Darüber hinaus sind die Standard-Timing-Informationen für LPDDR3 nicht mit QDR-IV kompatibel. Daher sollten alle Timing-Informationen für QDR-IV eingegeben werden und mit der Dokumentation für Ihren Chip übereinstimmen.

Dies kann entweder mit dem

Timing-Assistenten (Abb. 9) erfolgen, der den Benutzer auffordert, mehrere Formulare für die nachfolgende Generierung temporärer Werte auszufüllen, oder Sie können die .V-Synchronisationsdateien bearbeiten, die Ihrem Controller und DRAM entsprechen.

Abb. 9. Timing-Werte einstellenBitte beachten Sie

Abb. 9. Timing-Werte einstellenBitte beachten Sie : Da die Simulation im

LPDDR3- Modus durchgeführt wird, müssen die Ergebnisse entsprechend interpretiert werden.

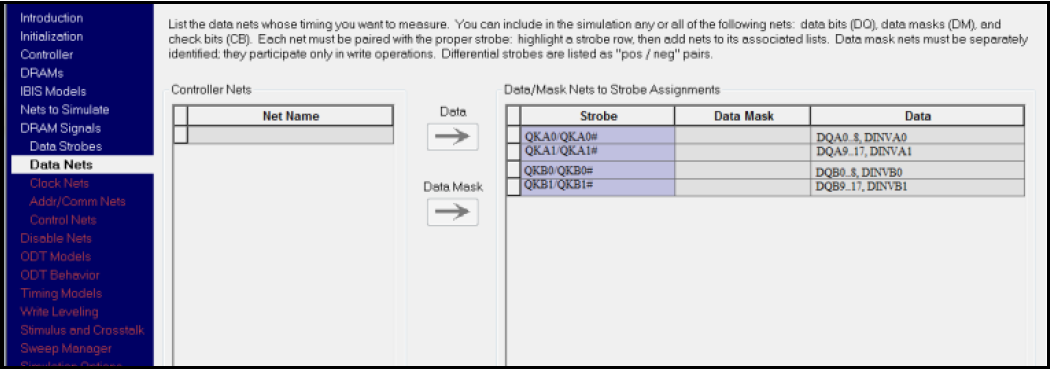

Datensignal: Schreibvorgang

Die Datenschreiboperation und ihre Analyse ähneln der oben beschriebenen Analyse für die Leseoperation. Es gibt jedoch zwei wesentliche Unterschiede, die wir jetzt betrachten werden. Mit Ausnahme dieser beiden Nuancen können die für den Datenlesevorgang unternommenen Schritte wiederholt werden, um das Schreiben von Daten zu simulieren.

Stellen Sie im Abschnitt

Zu simulierende Netze (Abbildung 10) sicher, dass

Nur Schreibzyklen ausgewählt ist.

Es ist auch möglich,

Schreibvorgänge für

Adressensignale zu simulieren. Vergessen Sie nicht, sicherzustellen, dass das

Kontrollkästchen Start des

Kompensationsversatzes aktiviert ist, um Abweichungen in der aktivierten Zeit bis zur Messung zu berücksichtigen .

Abb. 10. Datenaufzeichnung

Abb. 10. DatenaufzeichnungStellen Sie sicher, dass im Abschnitt

Data Strobe die richtigen Gates ausgewählt sind (Abbildung 11). Der Hauptunterschied zwischen einer Lesetransaktion und einer Schreibtransaktion ist der Strobe, der zum Synchronisieren der Daten verwendet wird. Dieser Strobe unterscheidet sich von dem Strobe, der für die Datenleseoperation verwendet wird (Fig. 12 und 13).

Abb. 11. Gates von Datensatzdaten

Abb. 11. Gates von Datensatzdaten Abb. 12. Signal-Strobe-Signalgruppen (36-Bit-Bus)

Abb. 12. Signal-Strobe-Signalgruppen (36-Bit-Bus) Abb. 13. Signal-Strobe-Signalgruppen (18-Bit-Bus)

Abb. 13. Signal-Strobe-Signalgruppen (18-Bit-Bus)Busadresse, Befehl und Steuerung

Der QDR-IV verwendet CK / CK # -Differentialsperren, um Steuersignale, Adressen und Befehlssignale auszuwählen. Die Vorderflanke des CK-Signals wird verwendet, um Informationen über Port A einzugeben, und die Hinterflanke wird verwendet, um Informationen über Port B auszuwählen.

Unter Berücksichtigung der Integrität des Signals müssen die Wellenformen für die Adressleitungen die Installationsanforderungen und Verzögerungen sowohl der Vorder- als auch der Hinterflanke des Taktsignals erfüllen. Dies ist dem Verhalten von LPDDR3 sehr ähnlich.

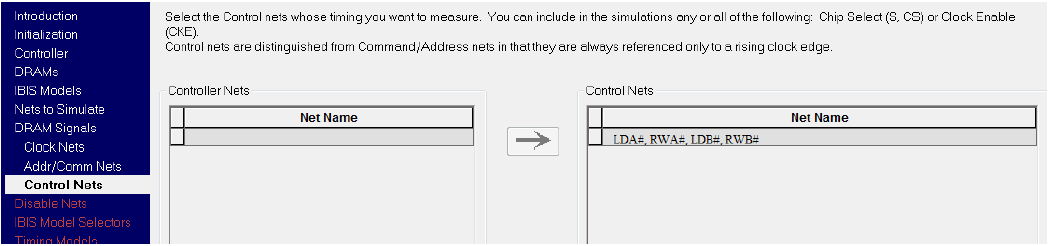

Die Signale

LDA #, LDB #, RWA # und RWB # werden mit derselben Datenrate (Einzeldatenrate) synchronisiert. Dies bedeutet, dass diese Signale nur an einer der beiden Fronten der Taktimpulse synchronisiert werden. Die Signale LDA # und RWA # werden bei der ansteigenden Flanke des Takts synchronisiert, und die Signale LDB # und RWB # befinden sich bei der abfallenden Flanke.

Die Blöcke sind weitgehend symmetrisch - das vordere Differential vorne unterscheidet sich nicht wesentlich vom hinteren. Dies bedeutet, dass zur Gewährleistung der Signalintegrität die Zeitsteuerungswerte für

LDB # und RWB # beim Abtasten an den ansteigenden oder

abfallenden Flanken des Takts nahezu gleich, wenn nicht identisch sein sollten. LPDDR3-Steuersignale werden auch nur bei steigender Flanke synchronisiert.

Die folgenden Schritte sind spezifisch für die Adressbus-, Befehls- und Steuerbussimulation mit QDR-IV.

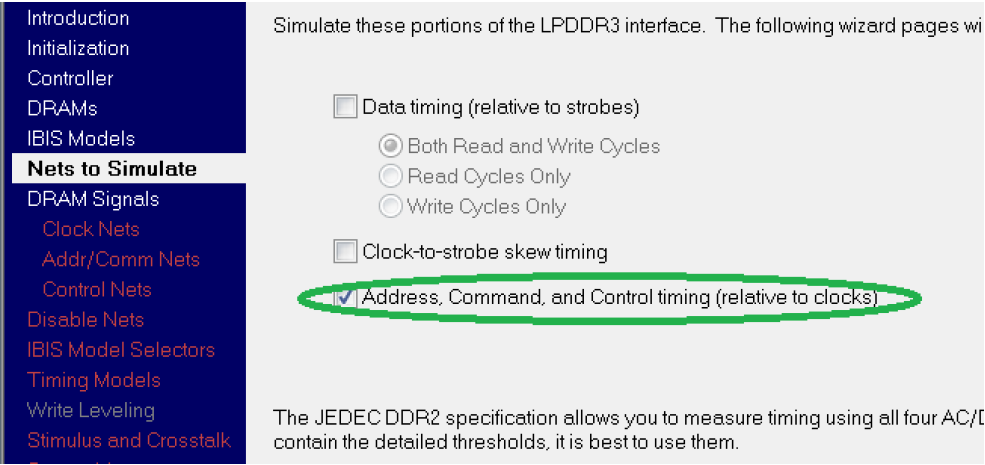

Stellen Sie sicher, dass im Abschnitt

Zu simulierende Netze das

Kontrollkästchen Adress-, Befehls- und Steuerzeitpunkt (relativ zu Uhren) aktiviert ist (Abb. 14).

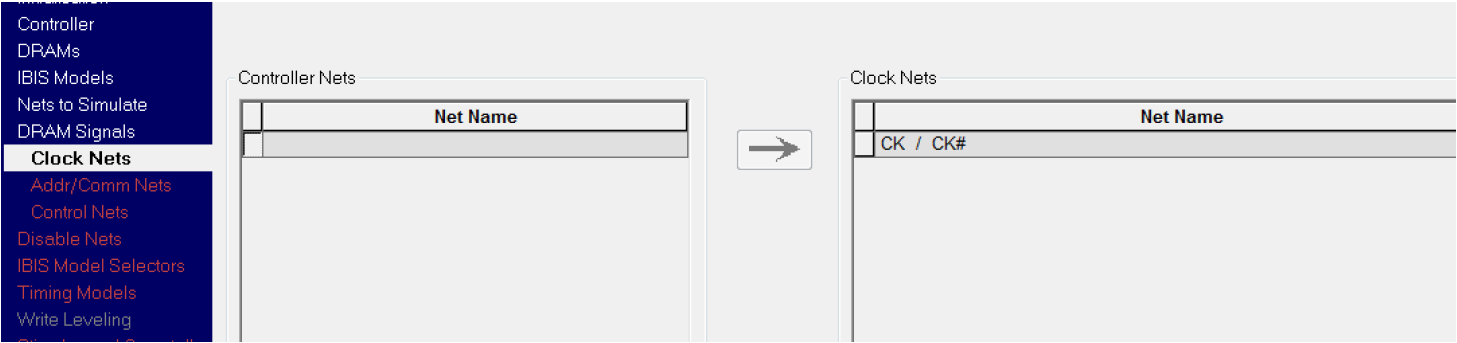

Abb. 14. Aktivieren Sie das Kontrollkästchen Adresse, Befehl und SteuerungStellen Sie im

Abb. 14. Aktivieren Sie das Kontrollkästchen Adresse, Befehl und SteuerungStellen Sie im Abschnitt Taktnetze sicher, dass das Differenzpaar der Taktsignale CK / CK # ausgewählt ist (Abb. 15).

Abb. 15. Die Wahl der DifferenzuhrStellen Sie im

Abb. 15. Die Wahl der DifferenzuhrStellen Sie im Abschnitt

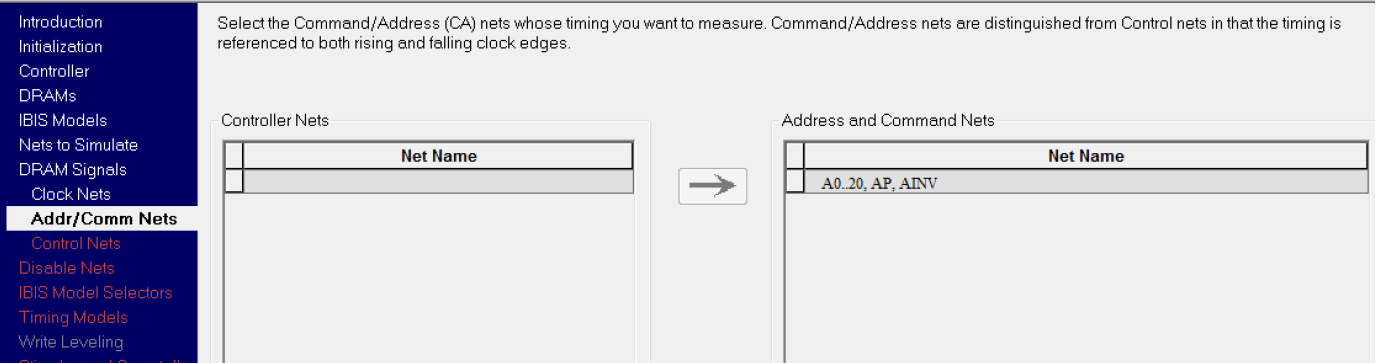

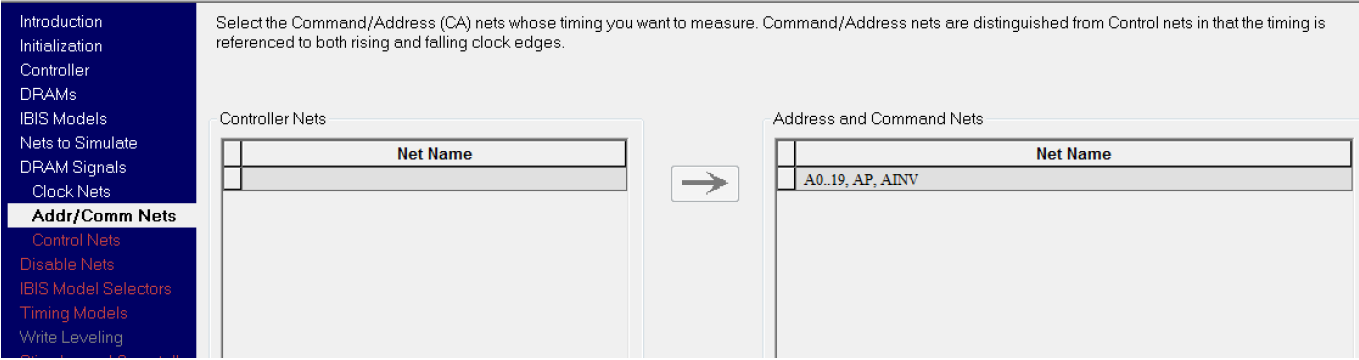

Addr / Comm Nets sicher, dass die Bits

A [20: 0] für Geräte mit x36 Bit und die Bits

A [19: 0] für Geräte mit x18 Bit ausgewählt sind.

Stellen Sie zusätzlich die

AP- und AINV-Signale ein (Abb. 16 und 17).

Abb. 16. Einstellungen für x36-Bit-Busse

Abb. 16. Einstellungen für x36-Bit-Busse Abb. 17. Einstellungen für x18-Bit-Busse

Abb. 17. Einstellungen für x18-Bit-BusseWählen Sie im Abschnitt

Kontrollnetze die Signale LDA #, LDB #, RWA # und RWB # aus (Abbildung 18).

Abb. 18. Steuersignale

Abb. 18. SteuersignaleStellen Sie wie beim Modellieren eines Datensignals sicher, dass Sie die richtigen Dateien mit Timing-Parametern verwenden. Der Rest der Modellierung und Auswertung der Ergebnisse ähnelt LPDDR3.

"Interpretieren der Ergebnisse des HyperLynx DDRx-Berichts"Fazit

Wenn Sie den einfachen Anweisungen in diesem Artikel folgen, können Sie das Hilfspaket des DDRx-Assistenten nutzen und verwenden, um QDR-IV-Busse zu simulieren und zu testen.

Ich hoffe, dieses Handbuch wird jemandem nützlich sein.

Mit freundlichen Grüßen Filipov Bogdan (

pbo ).

Bei dieser Gelegenheit möchte ich die Entwickler der REU zu einem von Nanosoft und Mentor Graphics organisierten Seminar einladen:

"Eine neue Generation von Lösungen für das Design elektronischer Geräte von Mentor Graphics"