Grüße, Habr! Mein Name ist Daniil Smirnov, ich studiere an der Graduiertenschule der ITMO-Universität, wo unser Team im Programmier- und Modellierungslabor mit programmierbarer Elektronik für Projekte im Zusammenhang mit Glasfasersensoren beschäftigt ist. Als Hardware-Basis für Sensoren werden FPGAs verwendet - Field Programmable Gate Array. Vor ein paar Jahren haben wir erfahren, dass FPGA-Hersteller Wettbewerbe unter Entwicklungsstudenten durchführen. Seitdem wird jedes Jahr ein Team aus uns gebildet, um an dieser Veranstaltung teilzunehmen, und da sich dieses Jahr als etwas Besonderes herausstellte, haben wir beschlossen, zu teilen, wie alles von innen war.

Eintrag

Es war Oktober 2017, ich habe eine wöchentliche Routineprüfung durchgeführt: eine Analyse der laufenden Konferenzen zu Themen, die in unserer Abteilung umgesetzt werden. Irgendwann erhalte ich einen Newsletter von Terasic: Ein

neuer Wettbewerb beginnt

mit der Entwicklung von Projekten mit Debug-Boards auf dem FPGA , jetzt weltweit. Die Erfahrung des gleichen Wettbewerbs des letzten Jahres geht mir durch den Kopf und erinnert mich: Verschieben bis zu den letzten zwei Wochen des Monats, langes Debuggen und Optimieren von Algorithmen und Ausgabe aller Kanäle an den Monitor und das Versprechen, ihn nicht bis zum letzten Tag zu verschieben.

Es war eine coole Erfahrung, bei der wir viel über eine Plattform wie SoC FPGA gelernt haben - die Verbindung einer Vielzahl von Logikelementen und dem Cortex-A9-Prozessor sowie deren Interaktion untereinander und mit den Peripheriegeräten auf dem Debugboard.

Neuer Wettbewerb - neue Regeln, neue Anforderungen, ein neues Level. Jetzt findet der Wettbewerb in mehreren Phasen statt: Zuerst werden die regionalen Phasen und dann das Finale in San Jose abgehalten. Das Board wird an alle Teilnehmer gleich

gesendet ,

DE10-Nano , und außerdem können Sie jetzt nicht nur die drei Grundmodule auswählen, sondern auch eine große Version der Boards von Analog Devices! Im Gegensatz zu Wettbewerben in den Vorjahren ist es diesmal jedoch erforderlich, eine Garantie für das Projekt zu unterzeichnen. Im Falle einer Nichterfüllung müssen die Teilnehmer Gebühren zurückschicken. Es ist ziemlich fair, wenn man die Statistiken der letzten Jahre berücksichtigt:

<...> 71 Teams aus 20 europäischen Ländern haben den Wettbewerb registriert. <...> 25 Richter aus Industrie (ALTERA) und Wissenschaft (CNFM) in Frankreich haben die 32 Projekte geprüft [1].

Der wissenschaftliche Berater war wie die Studenten, die an dieser Arbeit teilnehmen wollten, bereits bei verschiedenen Projekten stark belastet, aber die Aufregung während des Wettbewerbs und die Motivation, viele neue Dinge zu lernen, wurden zu wichtigen Argumenten, um wieder am Wettbewerb teilzunehmen. Es blieb ein Projekt, bei dem Sie sich bewerben können.

Idee für ein Projekt

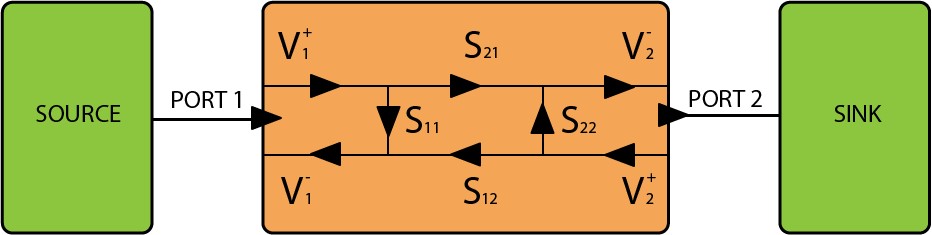

Damit das Projekt nicht beiseite blieb, wurde beschlossen, ein für die Abteilung nützliches Gerät zu implementieren, das später leicht entwickelt und verbessert werden konnte. Basierend auf den Tätigkeitsbereichen der Abteilung gab es verschiedene Optionen: ein optisches Reflektometer, ein stroboskopisches Oszilloskop usw. Bei einem kurzen Blick auf vorhandene Anwendungen und verfügbare zusätzliche Platinen wurde festgestellt, dass das Reflektometer bereits angekündigt war, ein stroboskopisches Oszilloskop jedoch nicht an solchen Elementen zusammengebaut werden konnte. Die einzige Idee, die am Leben bleibt, ist der Vektornetzwerkanalysator. Neulich wurden ein paar Spulen ins Labor gebracht, für die es keine Dokumentation gab. Die Aufgabe bestand darin, zumindest ungefähre Eigenschaften dieser Spulen zu bestimmen. Es war bekannt, dass der Schwingkreis in ihnen zusammengebaut war, daher bestand die Hauptaufgabe darin, die Resonanzfrequenz herauszufinden. Bei solchen Aufgaben kann ein Vektornetzwerkanalysator (VAC oder VNA - Vector Network Analyzer) nur eine Anwendung finden. Mit VNA können Sie eine Dispersionsmatrix definieren, die auch als S-Parameter-Matrix bezeichnet wird. Bei dieser Methode wird das untersuchte Element als Black Box betrachtet, in der die einfallenden und reflektierten Signale von den Anschlüssen dieses Geräts analysiert werden. Für ein Zwei-Port-System lautet die Matrix also wie folgt:

Wobei V1 + V2 + elektromagnetische Wellen sind, die an den Ports ankommen;

V1- V2- - elektromagnetische Wellen, die die Anschlüsse verlassen;

Sij sind Elemente der Mehrwege-Streumatrix. [2]

Messschema der S-Parameter eines Multipols

Messschema der S-Parameter eines MultipolsWir haben die Komponenten und die Schaltung nicht mit einem Röntgenstrahl untersucht (zumindest mit dem Röntgen der U-Bahn), daher wurde die folgende Schaltung auf den Knien aufgebaut: Die Frequenzen wurden abwechselnd mit einem Schritt durch den Zirkulator zum Spuleneingang unter Verwendung eines Generators eingestellt, der zweite Anschluss des Zirkulators wurde mit dem Spuleneingang verbunden und der dritte Eingang zu einem Oszilloskop mit in seiner Software den Amplituden-Frequenz-Analysemodus. Eine solche Schaltung ermöglicht es, den Parameter S11 zu messen, d.h. Reflexion. Am Ende gelang es mir nach viel Angst und Kalibrierung, diese Eigenschaft zu entfernen - aber zu welchem Preis? Die Abteilung hatte lange mit der Anschaffung eines Vektornetzwerkanalysators für solche Aufgaben (Messung der AFC elektronischer Geräte) gerechnet, aber dieser Kauf wurde immer irgendwie verzögert.

Nach der Aufregung mit den Spulen wurde beschlossen, einen eigenen Schaltungsanalysator mit Visualisierung und komfortabler Abstimmung zusammenzustellen. Es ist nicht schwierig, von Studenten und Doktoranden der Abteilung Aufregung und den Wunsch zu finden, etwas Neues für sich selbst zu lernen. Daher wurde das Team schnell aus einem Elektronikingenieur, einem Programmierer und Entwickler von Systemen auf einem Chip, mir und zwei Mentoren zusammengestellt.

Kaum gesagt als getan! Nach zahlreichen Diskussionen über das Frequenzband, Verarbeitungsalgorithmen und andere Parameter des Projekts enthielt die Anwendung Folgendes:

- Das beanspruchte Projekt ist ein Vektorschaltungsanalysator, der auf SoC-FPGA auf einer DE10-Nano-Karte basiert;

- Angeforderte zusätzliche Karten: eine Karte mit einem programmierbaren Frequenzgenerator, einem Hochfrequenzmischer und eine Karte mit einem ADC;

- Betriebsfrequenzbereich: gemäß den angegebenen Parametern zusätzlicher Karten;

- Möglichkeiten zur schnellen Erweiterung der Anzahl der angeschlossenen Ports;

- Die Ausgabe der Amplituden- und Phasenkomponente an den Bildschirm;

- Weitere grundlegende Ein- / Ausgabefunktionen für den Vektornetzwerkanalysator.

Um zur nächsten Stufe überzugehen, war es erforderlich, dass die Projektseite eine ausreichende Anzahl von „Likes“ von Benutzern erhielt, die sich auf der Site registriert hatten. Zuerst lief alles gut, aber dann gewannen einige zweifelhafte Projekte im Vergleich zu anderen Projekten unrealistische und gegensätzliche Werte für Vorlieben und Ansichten. Es stellte sich heraus, dass die Website des Wettbewerbs zu anfällig für Betrug war.

Nach einiger Zeit teilten die Organisatoren mit, dass die Jury immer noch die Finalisten auswählen würde, so dass die Likes der Benutzer tatsächlich ihr Gewicht verloren. Am 31. Januar erschien unser Team in den Listen derjenigen, die zur nächsten Stufe übergingen, und wir begannen, unser Projekt im Vorgriff auf das Debuggen genauer zu überdenken.

Harte Realität

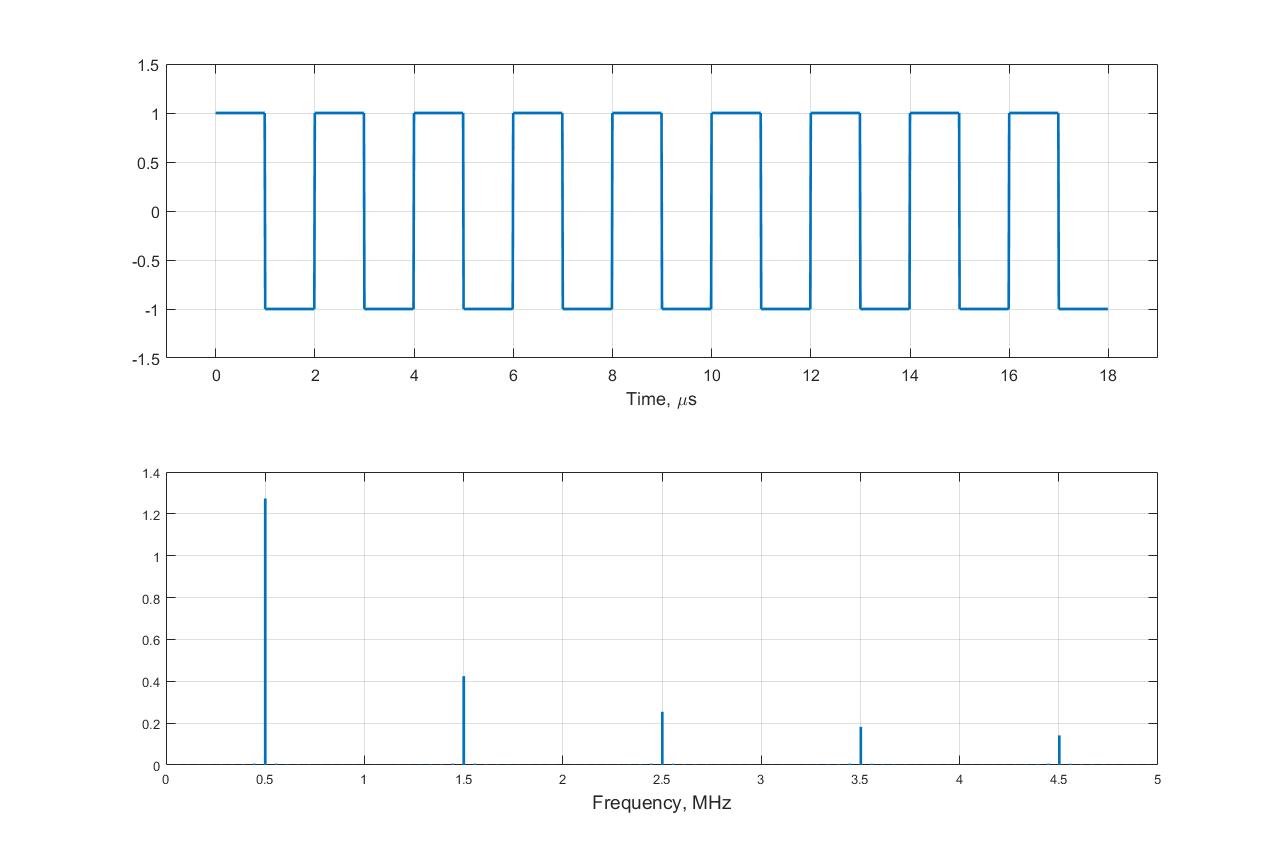

Das erste war das DE10-Nano-Board. Angenehm, aber etwas seltsam: Sie erwarteten, dass die Bretter alle zusammen kommen würden. Ein paar Tage später kommt ein Anruf vom Zoll: Gebühren kamen, alle zusammen überschreiten die Preisschwelle, so dass Sie für die Zollabfertigung einen Betrag zahlen müssen, der ungefähr den Kosten dieser Gebühren entspricht. Eine solche Situation hat uns verärgert, aber nicht zu uns gepasst: Wir haben die Bretter abgelehnt. In Gegenwart von Mischern und Generatoren, die wir nicht hatten, ist es notwendig, neue Lösungen zu finden. Was tun? Das erste, was mir in den Sinn kam, war nicht die genaueste, sondern eine ungewöhnliche Lösung: Verwenden Sie das übliche GPIO-Bein und erzeugen Sie daraus einen Mäander. Am Ausgang dieses Fußes ist ein analoges Tiefpassfilter mit einem Grenzband installiert, das etwas größer als die maximale Mäanderfrequenz ist. Für den Anfang wurde vorgeschlagen, die Analyse ab 1 MHz zu starten (zum Beispiel): Dann würden wir nach dem Filter einen mehr oder weniger reinen Sinus erhalten (die höchsten Harmonischen würden vom Filter abgeschnitten) und so weiter, bis die Frequenz auf die abfällt, bei der das Signal nach dem Filter liegt Es wird zwei Harmonische geben. Der Mäander ist die Summe der ungeraden Harmonischen, und der proportionale Beitrag jeder Harmonischen ist im Voraus bekannt [3].

Ein Beispiel für einen Mäander im Zeit- und Frequenzbereich: Die Komponenten des harmonischen Signals bei 500 kHz, 1,5 MHz usw. sind im Spektrum sichtbar.

Ein Beispiel für einen Mäander im Zeit- und Frequenzbereich: Die Komponenten des harmonischen Signals bei 500 kHz, 1,5 MHz usw. sind im Spektrum sichtbar.Mit einem Filter mit einer Grenzfrequenz von 1 MHz können Sie auf 33 (3) kHz herunterfahren. Nach dieser Frequenz sollten wir die Summe von zwei Sinus hinter dem Filter erhalten. Das proportionale Verhältnis ihrer Amplituden ist bekannt (sinc-Funktion), die Reaktion des gemessenen Geräts auf eine Frequenz von 1 MHz (erste ungerade Harmonische) ebenfalls. Wir müssen also eine Gleichung mit einer Unbekannten erstellen und die Reaktionscharakteristik auf eine Frequenz von 33, (3) kHz berechnen! Anfangs schien diese Lösung zu einfach zu sein, daher wurde sie zunächst allen in der Hoffnung mitgeteilt, dass jemand einen Fehler finden würde. Es wurden keine Fehler gefunden, aber im Verlauf der Diskussion wurden eine Reihe von Einschränkungen festgestellt:

- Der GPIO-Fuß ist nicht die beste Quelle für einen Mäander, insbesondere mit zunehmender Häufigkeit.

- Das Löten eines kompakten Filters auf verfügbare Komponenten ist keine triviale Aufgabe.

- Selbst wenn diese Einschränkungen umgangen werden können, tritt ein Synchronisationsproblem für die Phasendetektion auf.

Angenommen, wir haben alle Probleme auf der analogen Seite gelöst. programmatisch ergeben sich zwei weitere:

- Mit abnehmender Häufigkeit trägt der Fehler jeder vorherigen Erkennung und Berechnung zur nachfolgenden Messung bei.

- Mit abnehmender Häufigkeit erhöht sich die Zeit zur Berechnung der Eigenschaften erheblich.

Und zu guter Letzt. Die beschriebene Schaltung kann verwendet werden, wenn das gemessene Element durch eine lineare Übertragungsfunktion beschrieben werden kann. Wenn wir jedoch eine Black Box mit nichtlinearen Eigenschaften messen, hat die Idee mehr Probleme als gute. Es blieb nicht viel Zeit (das erste Ergebnis sollte zwei Monate nach dem Eintreffen des Boards angezeigt werden). Daher haben wir uns nach einiger Überlegung entschlossen, unsere Bestände mit den vorhandenen Debug-Boards zu überprüfen - und einen

14-Bit-DAC bei 125 Msps gefunden ! Nicht die eleganteste Lösung, aber keine Wahl, wir verwenden sie als Ausgangssignalgenerator.

Erstes Konzept

Der als Generator ausgewählte DAC empfängt Daten am Eingang des Parallelbusses und speichert sie mit einem vom FPGA kommenden Taktsignal. Eine solche Schaltung ist ideal für die Synchronisation in unserer Schaltung. Bei der Entdeckung blieben jedoch Fragen offen.

Ja, auf derselben Karte befindet sich ein 14-Bit-ADC mit 65 Msps. Aber nur die Fähigkeiten des Generators sind möglicherweise höher, und nach dem Satz von Kotelnikov funktioniert dieser ADC nicht mehr bei maximalen Frequenzen.

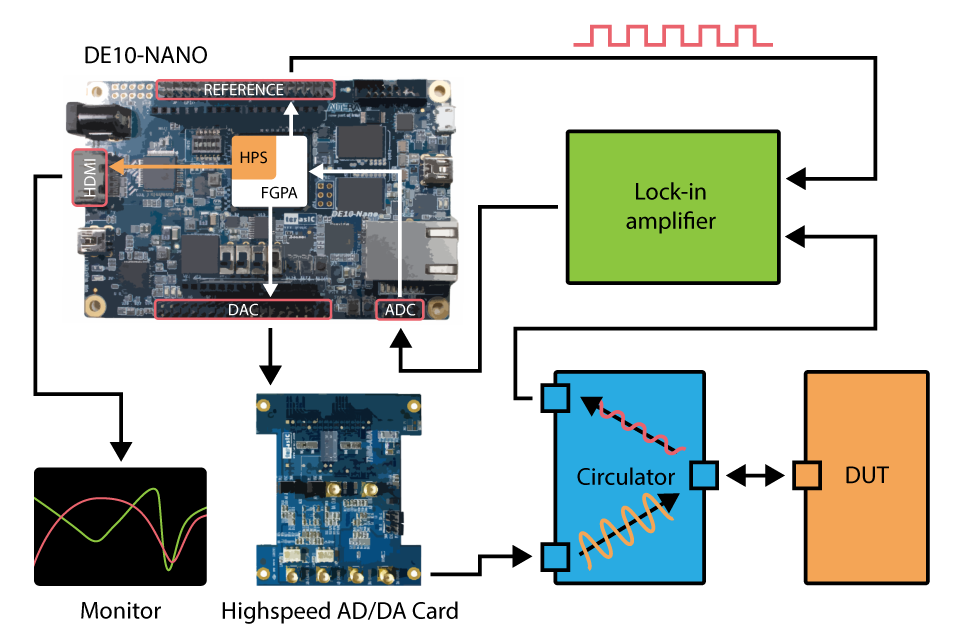

Die Lösung wurde bei einer Diskussion dieses Problems mit erfahrenen Elektronikingenieuren gefunden. Es stellte sich heraus, dass wir für unsere Aufgabe eine Lock-In-Verstärkerschaltung verwenden können: Der Ausgang eines solchen Detektors besteht aus zwei konstanten Werten, Phasen- und Quadraturkomponenten, aus denen Sie die Amplitude und Phase des Signals erhalten können, und da sie konstant sind, können sie erfasst werden auch mit dem langsamen ADC auf dem DE10-Nano! Es wurde beschlossen, die Schaltung zuerst in LTSpice zu modellieren und erst dann die Komponenten auszuwählen und die Schaltung zusammenzubauen, wobei zu berücksichtigen ist, dass der Detektoreingang ein Signal vom Zirkulator ist und die Ausgänge mit dem ADC auf der DE10-Nano-Karte verbunden sind.

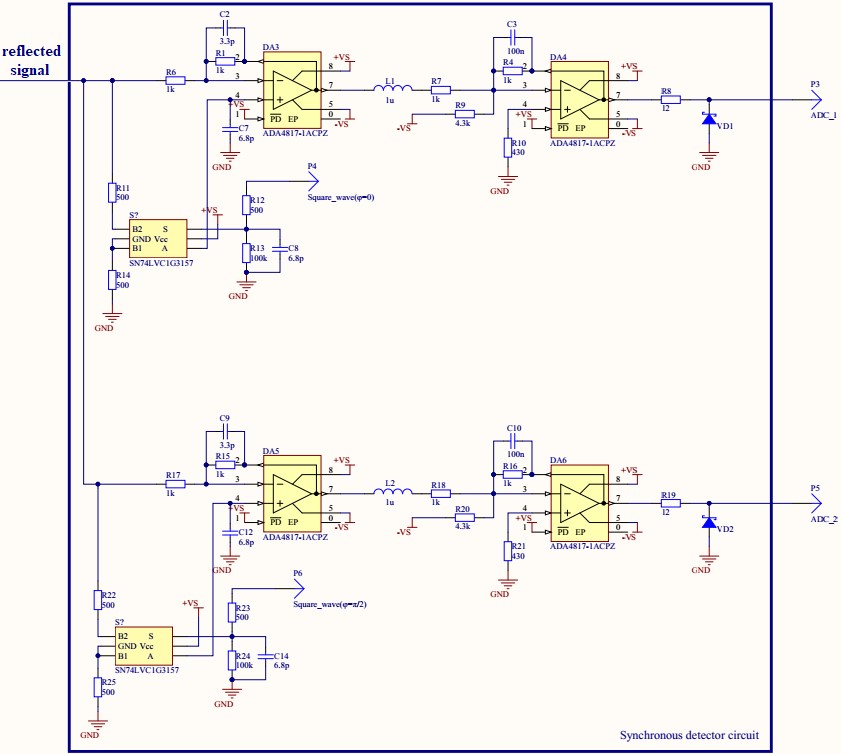

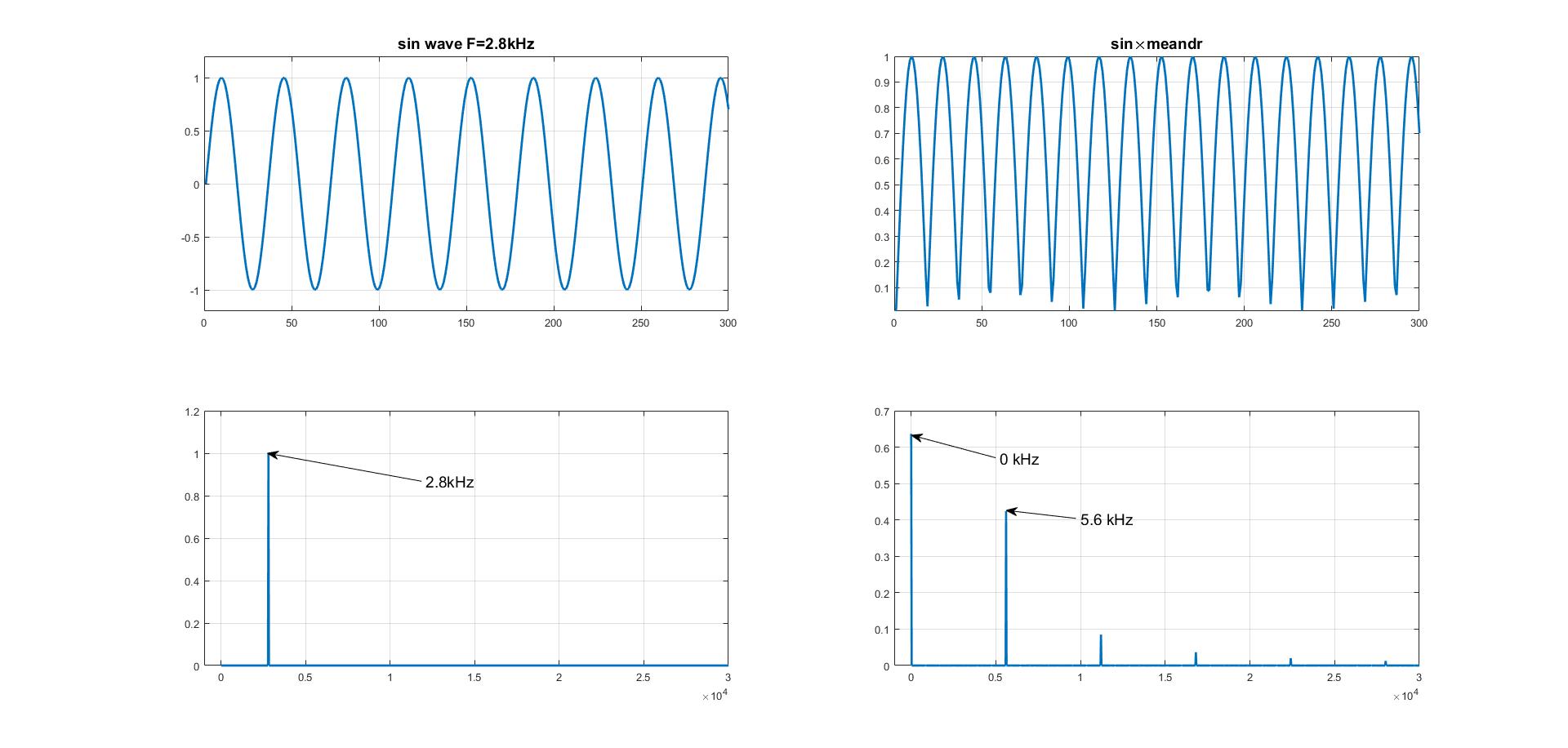

Über Synchrondetektor und ZirkulatorEin Synchrondetektor wird auch bei der digitalen Signalverarbeitung verwendet, um verschiedene Signale vor einem Hintergrund von Rauschen zu erfassen. Zurich Instruments hat eine gute Beschreibung [4], in unserem Fall lautet die Erkennung wie folgt: Das reflektierte Signal bekannter Frequenz wird mit dem Mäander unter Verwendung eines Hochfrequenzschalters und eines Operationsverstärkers multipliziert:

Die Reflexionserkennungsschaltung

Die ReflexionserkennungsschaltungTatsächlich wird die Multiplikation als Umschalten des Betriebsmodus des Operationsverstärkers implementiert, und das Umschalten wird durch zwei Mäander gesteuert, die von der DE10-Nano-Karte kommen: einer von ihnen ist in Phase mit dem ursprünglichen Signal (am Eingang des Geräts empfangen) und der andere mit einer Phasenverzögerung von 90 Grad.

Das Ergebnis der Multiplikation ist die Übertragung des Nutzsignals auf die Gleichstromkomponente, und alle oben genannten Frequenzen sind nicht mehr interessant und können daher herausgefiltert werden:

Signalspektrum vor und nach der Multiplikation: Am Ausgang des Operationsverstärkers können Sie ein einfaches Tiefpassfilter zusammenbauen, um nur die Gleichstromkomponente zu isolieren

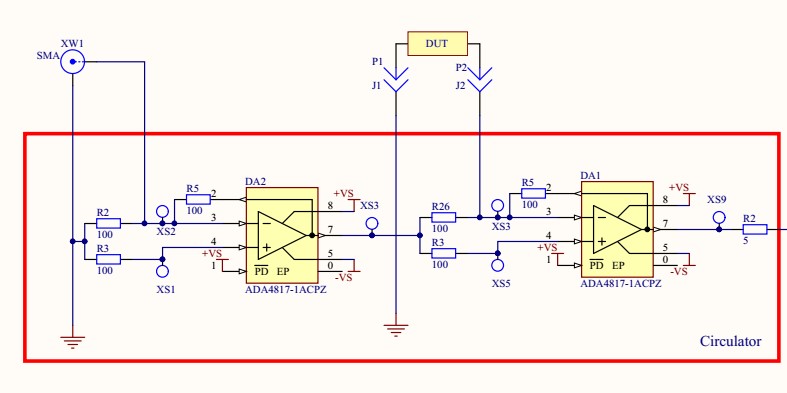

Signalspektrum vor und nach der Multiplikation: Am Ausgang des Operationsverstärkers können Sie ein einfaches Tiefpassfilter zusammenbauen, um nur die Gleichstromkomponente zu isolierenEin Zirkulator an Operationsverstärkern (Operationsverstärkern) ist eine Reihenschaltungsschaltung von Operationsverstärkern, die in einem Ring geschlossen sind. OA-Zirkulatoren werden für viele Zwecke verwendet, insbesondere zum Einstellen von Antennen, Verstärkern, Generatoren, Gigabit-Ethernet usw. im Frequenzbereich bis zu Hunderten von Megahertz. Bei der Erstellung der VAC wurde eine Zirkulatorschaltung verwendet, die auf der Basis von zwei Operationsverstärkern erstellt wurde [5].

Schaltplan zum Anschluss des Messgerätes

Schaltplan zum Anschluss des Messgerätes  Projektkonzept aktualisiert

Projektkonzept aktualisiertSinusförmige Signale mit einer Frequenz von 1 Hz bis 1 MHz mit auf einige Hz eingestellten Schritten wurden dem ersten Anschluss des Zirkulators zugeführt. Das untersuchte Gerät wurde an den zweiten Port angeschlossen, abhängig von dem Frequenzgang, bei dem sich ein Reflexionskoeffizient des Signals änderte. Das reflektierte Signal wurde Port 3 zugeführt, wo eine Synchrondetektorschaltung zusammengebaut wurde, um die Frequenz- und Phaseneigenschaften zu bestimmen. Für einen korrekten Betrieb wurden die Anschlüsse des Zirkulators auf eine Impedanz von 100 Ohm abgestimmt, was mit dem Ausgangswiderstand des DAC und der Wahl der untersuchten Geräte verbunden war.

Es blieb weniger als ein Monat, bis das Projekt abgeschlossen war, und bis zum Ende der Frist mussten Berichtsmaterialien erstellt werden: eine detaillierte Beschreibung des Projekts auf der Wettbewerbsseite, ein öffentlich zugängliches Projekt auf GitHub und ein Videobericht über die geleistete Arbeit.

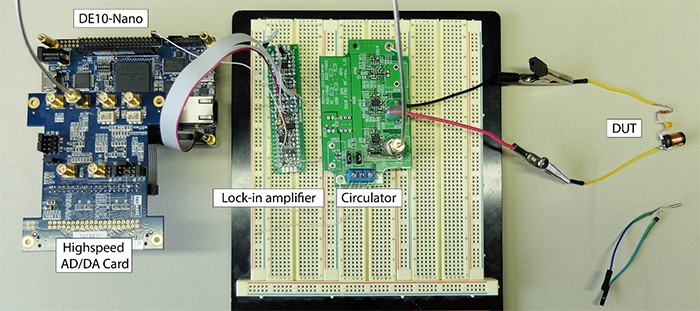

Da wir nun verstanden haben, welche Daten in die Ein- und Ausgänge fließen würden, haben wir mit der Arbeit an einem Projekt für das SoC-FPGA begonnen. Wir haben gesehen, wie das Projekt wie folgt umgesetzt wurde: Der Benutzer legt den Frequenzbereich fest, in dem die Messung geplant ist, das FPGA beginnt in einem bestimmten Intervall mit der Erzeugung von Harmonischen über den DAC, der ADC empfängt die Quadratur- und Phasenkomponenten am Eingang und wandelt sie in die Amplituden- und Phasenwerte bei der aktuellen Frequenz um Die erhaltenen Werte werden in Echtzeit auf dem mit der Debug-Karte verbundenen Monitor angezeigt. Bei der Anzeige von Informationen auf dem Monitor wurden bereits Erfolge erzielt. Der Hauptteil war daher die korrekte Wiedergabe von Daten in Echtzeit und die Ausgabe des Bildes auf HDMI. Wir sind nicht gruppiert. Die erste Gruppe nahm Aufgaben im Programm für den Prozessor auf, um die notwendigen Initialisierungen und Fragen zur Datenvisualisierung genauer zu verstehen. Wir haben sie auch gebeten, die Bildschirmauflösung auf 1024 x 768 zu erhöhen [6]. Die zweite Gruppe hinterließ Details zur Implementierung des Teils auf dem FPGA, das dann über den Schnittstellenbus lightweight_h2f an den Prozessor geliefert werden sollte, sowie einen Test der Funktionsfähigkeit des Synchrondetektors des ersten Prototyps. Nachdem die Mängel beseitigt und die Eigenschaften mehrerer Elemente erfolgreich gemessen worden waren, blieb nicht viel Zeit. In den nächsten zwei Tagen wurden die Systeme miteinander verbunden, Berichte hinzugefügt und das Video bearbeitet.

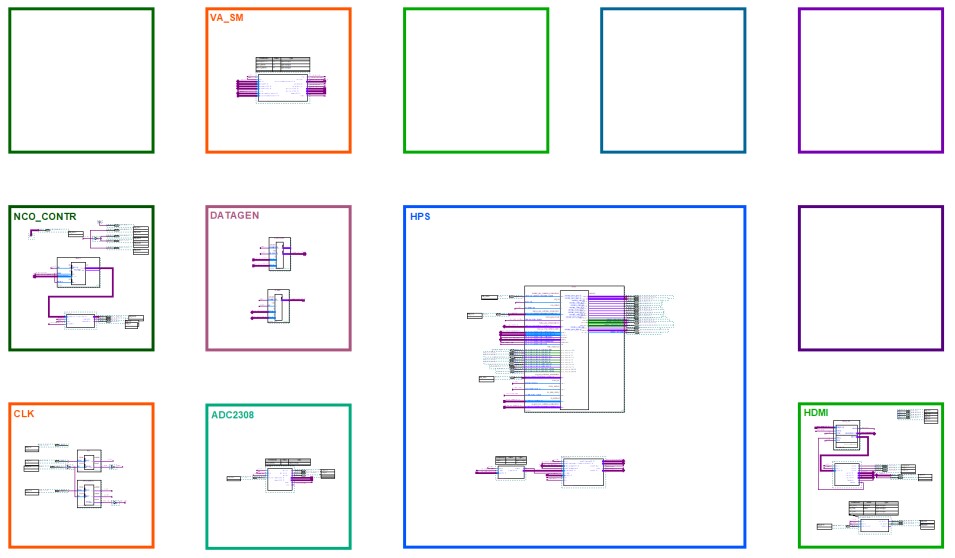

Darstellung der Datei der obersten Ebene in Quartus II

Darstellung der Datei der obersten Ebene in Quartus IILetzte Minuten

Nachdem wir mehr als ein paar Tage im Labor verbracht hatten, bauten wir das gesamte System zusammen. Es funktionierte nicht für den gesamten potenziellen Frequenzbereich, sondern maß nur den S11-Parameter und spiegelte die gemessenen Phasen- und Amplitudeneigenschaften des angeschlossenen Geräts auf dem Monitor wider. Das extern montierte Gerät sah immer noch nicht besonders attraktiv aus - drei separate Platinen, die durch einadrige Drähte verbunden sind, aber dies ist ein

funktionierender Prototyp, und Sie können in der nächsten Phase einen Marafet anlegen. Wir haben den Text geschrieben, die Implementierungsphasen illustriert, ein Video gedreht, alles auf die Site hochgeladen und angefangen zu warten.

Natürlich haben wir einigen Freunden Links zu diesen Materialien gesendet, um leicht Ansichten hinzuzufügen. An einem Tag wuchsen die Ansichten jedoch von selbst, als hätte jemand dies zu einer Beförderung zusammengeführt. Nach einer kleinen Analyse stellte sich heraus: Unser Projekt wurde auf hackaday.io [7] bemerkt und die überwiegende Mehrheit der Ansichten stammte von dort. Es war interessant, die ersten Antworten auf unser Projekt zu sehen. Inspiriert begannen wir auf die Ergebnisse zu warten.

Allerdings

Dies ist nicht das erste Jahr unserer Teilnahme am Wettbewerb. Dieses Projekt war für uns das nachdenklichste unter den zuvor umgesetzten studentischen Arbeiten. Aber es ist nicht zusammengewachsen: Wir sind nicht zur nächsten Stufe übergegangen. Vielleicht liegt das an einem Missverständnis zwischen uns und den Richtern. Vielleicht geht das Projekt einfach nicht vollständig in den Bereich der aktuellen Trends für FPGAs (Kryptographie, paralleles Rechnen, neuronale Netze usw.) ein. Für uns ist dies jedoch ein großer Schritt in der Entwicklung von SoC FPGA, einem neuen Entwicklungszweig und vor allem Erfahrung.

Ps

Herzlichen Glückwunsch an die russischen Vertreter, die im Finale des Wettbewerbs den zweiten Platz belegt haben!

Ich danke meinen Projektkollegen Danila Nikiforovsky und

Yevgeny Vostrikov sowie den Leitern

Ivan Deineku ,

Philipp Shuklin und Artem Aleinik für ihre aktive Teilnahme und Unterstützung.

Referenzen

[1] Innovate Europe 2015-Wettbewerb

www.innovateeurope.org/eu/2015winner.html[2] Leitfaden für Ingenieure zum automatisierten Testen von Hochgeschwindigkeitsschnittstellen, Jose Moreira, Hubert Wekmann, 2010, Anhang F, S. 503

[3] Spektrum einer periodischen Folge von Rechteckimpulsen,

en.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html[4] Grundsätze der Lock-In-Erkennung und Stand der Technik, Zurich Instruments

www.zhinst.com/applications/principles-of-lock-in-detection[5] Niederfrequenzzirkulator / Isolator ohne Ferrit und Magnet

www.cqham.ru/oth9.htm[6] VAC-Projekt für DE10-Nano-Board

github.com/tvShushtov/em078_vector_analyzer[7] Artikel über die VAC auf Hackaday

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga