Intel entwickelte den 8087-Chip 1980, um die Leistung von PCs mit 8086/8088-Linienprozessoren (wie dem IBM-PC) bei Gleitkommaoperationen zu verbessern. Da die ersten Mikroprozessoren für die Ausführung von Operationen mit ganzen Zahlen ausgelegt waren, war die Ausführung von Operationen mit Gleitkommazahlen langsam, dh über die Leistung transzendentaler Operationen wie trigonometrischer Funktionen oder Logarithmen. Der Coprozessor 8087 erhöhte die Geschwindigkeit der Ausführung von Gleitkomma-Aufgaben erheblich, alles wurde fast 100-mal schneller erledigt. Die 8087-Architektur wurde auch in späteren Intel-Prozessoren implementiert, und die 8087-Anweisungen werden weiterhin in modernen x86-PCs verwendet. Intel führte 1980 den 8087-Chip ein, um die Leistung des Gleitkomma-Computing auf 8086- und 8088-Prozessoren zu verbessern.

Da frühe Mikroprozessoren nur mit ganzen Zahlen arbeiteten, war die Gleitkomma-Arithmetik langsam und transzendentale Operationen wie Trigger oder Logarithmen sahen noch schlechter aus. Durch Hinzufügen des mathematischen Coprozessors 8087 zum System konnten wir Gleitkommaoperationen um das 100-fache beschleunigen. Die 8087-Architektur wurde Teil späterer Intel-Prozessoren, und die 8087-Anweisungen (obwohl veraltet) sind immer noch Teil moderner x86-Desktops.

Der 8087-Chip lieferte eine schnelle Gleitkomma-Arithmetik für den ursprünglichen IBM-PC und wurde Teil der heute verwendeten x86-Architektur. Eines der ungewöhnlichen Merkmale des 8087 ist ein mehrstufiger ROM (Nur-Lese-Speicher), der zwei Bits pro Transistor speichern kann, was der doppelten Dichte eines herkömmlichen ROM entspricht. Anstatt Binärdaten zu speichern, speicherte jede Zelle im 8087-ROM einen von vier verschiedenen Werten, die dann in zwei Bits decodiert wurden. Da der 8087 eine große Menge an ROM für den Mikrocode (1) benötigte und die Anzahl der Transistoren auf dem Chip sehr begrenzt war, verwendete Intel eine ungewöhnliche Technologie, um das Problem zu lösen. In diesem Artikel werde ich erklären, wie Intel dieses geschichtete ROM implementiert hat.

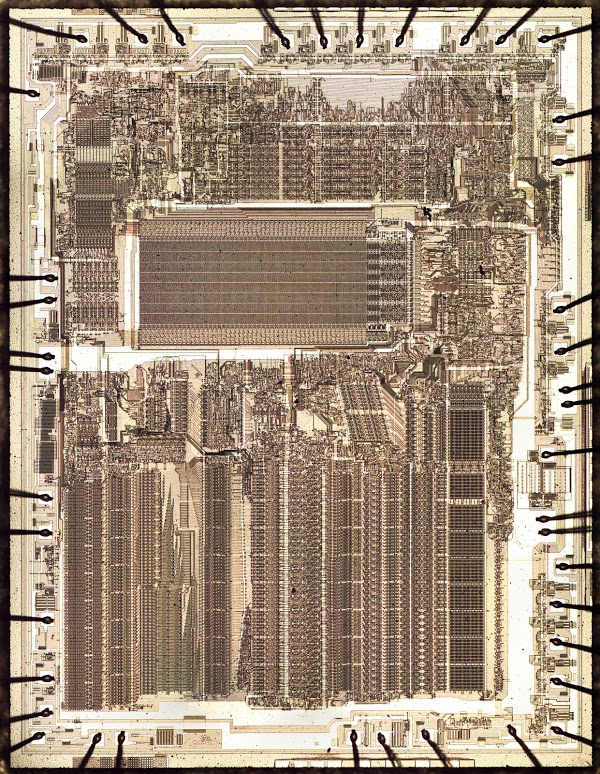

Ich öffnete den 8087-Chip und fotografierte ihn mit einem Mikroskop, wobei ich das Foto unten bekam. Auf dem Foto habe ich die Hauptfunktionsblöcke angegeben, die auf meinem eigenen Reverse Engineering basieren (Klicken, um das Bild zu vergrößern). Die Prozessormatrix 8087 ist mit 40.000 Transistoren (2) recht komplex. Der 8087 verwendet 80-Bit-Gleitkommazahlen: 64 Bit sind für die Mantisse reserviert, 15 Bit sind für den Exponenten und ein weiteres vorzeichenbehaftetes Bit. (Beispiel einer Zahl mit einer Basis von 10: Unter 6,02 × 1023 ist 6,02 die Mantisse und 23 der Exponent). Am unteren Rand des Fotos markiert das Wort "Bruchverarbeitung" einen Teil des Schemas für die Mantisse. Dies umfasst von links nach rechts: konstanten Speicher, 64-Bit-Verschiebung, 64-Bit-Addierer / Subtrahierer und Registerstapel. Etwas höher ist das Schema zur Verarbeitung des Exponenten.

Mathematischer Coprozessorchip für Intel 8087-Gleitkommaoperationen mit der Bezeichnung der HauptfunktionsblöckeDas Ausführen der Anweisung auf 8087 erforderte mehrere Schritte und in einigen Fällen mehr als 1000. Die 8087-Firmware verwendete Mikrocode, um bei jedem Schritt Operationen auf niedriger Ebene zu bestimmen: Verschiebungen, Inkremente, Speicherabtastungen, Lesekonstanten usw. Sie können den Mikrocode als einfaches Programm wahrnehmen. geschrieben in Form von Mikrobefehlen, bei denen jeder Mikrobefehl Steuersignale für verschiedene Komponenten des Chips erzeugt. Das Foto oben zeigt ein ROM mit dem Mikrocode-Programm 8087. Das ROM nimmt einen großen Teil des Chips ein und zeigt deutlich, warum ein kompaktes mehrstufiges ROM erforderlich war. Links vom ROM befindet sich die "Engine", auf der das Mikrocode-Programm gestartet wurde, in der Tat ein einfacher Prozessor.

Der 8087 arbeitete als Coprozessor mit dem 8086-Prozessor. Als der 8086 einen speziellen Gleitkomma-Befehl erkannte, ignorierte der Prozessor diesen und erlaubte dem 8087, den Befehl parallel auszuführen. Ich werde die internen Abläufe von 8087 nicht im Detail erläutern, aber kurz gesagt, Gleitkommaoperationen wurden unter Verwendung von Ganzzahl-Add / Subtraktions- und Verschiebungsoperationen implementiert. Um zwei Gleitkommazahlen zu addieren oder zu subtrahieren, führte 8087 eine bitweise Verschiebung der Zahl durch, bis die binären Begrenzer (dh das Dezimaltrennzeichen ist ein Komma, aber im binären System) gleich sind, und addierten oder subtrahierten dann die Mantisse. Multiplikation, Division und Quadratwurzel wurden durch wiederholte Verschiebungen, Additionen oder Subtraktionen durchgeführt. Transzendentale Operationen (tan, arctan, log, power) verwendeten CORDIC-Algorithmen, die Verschiebungen und das Hinzufügen spezieller Konstanten verwenden und jeweils ein Bit verarbeiten. 8087 stieß auch auf viele Sonderfälle: Unendlichkeit, Überlauf, NaN (keine Zahl), denormalisierte Zahlen und verschiedene Rundungsmodi. Der im ROM gespeicherte Mikrocode steuerte alle diese Vorgänge.

ROM-Implementierung

Der 8087-Chip besteht aus einer winzigen Siliziummatrix, auf der Silizium stellenweise mit Verunreinigungen dotiert ist, um die gewünschten Halbleitereigenschaften zu erhalten. Polysilicium (eine spezielle Art von Silizium) wird auf die Siliziumoberfläche aufgebracht, die Drähte und Transistoren bildet. Und schließlich vervollständigt eine Metallschicht auf Silikon den funktionierenden Stromkreis. Auf dem Foto unten auf der linken Seite ist ein kleiner Teil des Chips dargestellt, der unter dem Mikroskop sichtbar ist und eine gelbliche Metallverdrahtung zeigt. Auf der rechten Seite des Fotos wurde das Metall mit Säure entfernt, wodurch Polysilicium und Silicium freigelegt wurden. Wenn Polysilicium Silizium kreuzt, wird ein Transistor gebildet. Die rosa Bereiche sind dotiertes Silizium und die dünnen vertikalen Linien sind Polysilizium. Kleine Kreise sind die Kontakte zwischen den Schichten aus Silizium und Metall, die sie miteinander verbinden.

ROM-Struktur in Intel 8087 FPU. Die Metallschicht ist links und Polysilicium und Silicium rechts dargestellt.Obwohl es viele Möglichkeiten gibt, ROMs zu erstellen, besteht die Standardmethode darin, ein Gitter von "Zellen" zu erstellen, in denen jede Zelle ein Bit speichert. Jede Zelle kann einen Transistor haben (was 0 Bits bedeutet) oder keinen Transistor haben, was 1 Bit bedeutet. In der Abbildung oben sehen Sie ein Gitter von Zellen mit Transistoren (bei denen Polysilizium auf Silizium aufgebracht wird) und fehlenden Transistoren (bei denen Lücken im Silizium vorhanden sind). Um Informationen aus dem ROM zu lesen, wird eine Spaltenauswahlzeile (basierend auf der Adresse) aktiviert, um die in dieser Spalte gespeicherten Bits auszuwählen und ein Bit aus jeder Zeile am Ausgang zu erhalten. Sie können die vertikalen Spaltenauswahllinien (Spaltenauswahllinien) von Polysilicium und die horizontalen Metallzeilen auf dem Foto oben sehen. Die vertikalen Linien aus dotiertem Silizium sind geerdet.

Das folgende Diagramm (entsprechend dem 4x4-ROM-Segment) erklärt, wie das ROM funktioniert. Jede Zelle hat entweder einen Transistor (schwarz) oder keinen Transistor (ausgegraut). Wenn an die Polysilicium-Säulenauswahlleitung Spannung angelegt wird, schalten sich die Transistoren in dieser Säule ein und erden die entsprechenden Metallreihen. (In diesem Fall ist der NMOS-Transistor wie ein Gate, das offen ist, wenn der Eingang 0 ist, und geschlossen ist, wenn der Eingang 1 ist.) Die Metall- "Zeilen" der Schaltung geben die in der ausgewählten "Spalte" gespeicherten Daten aus.

Schema 4x4 ROM-SegmentSpaltenauswahlsignale werden von einer Decoderschaltung erzeugt. Da diese Schaltung aus NOR-Ventilen besteht, werde ich zunächst den Aufbau der Ventile erläutern. Das folgende Diagramm zeigt ein NOR-Gatter mit vier Eingängen, das aus vier Transistoren und einem Pull-up-Widerstand besteht (obwohl tatsächlich ein spezieller Transistor die Funktion des Widerstands erfüllt). Auf der linken Seite der Schaltung sind alle Eingänge 0, sodass alle Transistoren ausgeschaltet sind und der Pull-up-Widerstand das Ausgangssignal auf einem "hohen" Pegel hält. Auf der rechten Seite wurde 1 an einen der Eingänge angelegt und der Transistor eingeschaltet. Der Transistor ist geerdet, so dass das Ausgangssignal jetzt "niedrig" ist. Wenn also irgendwelche Eingänge hoch sind (1), ist der Ausgang niedrig (0). Diese Schaltung implementiert also das NOR-Ventil.

4-Wege-NOR-Gatter aus NMOS-TransistorenDie Spaltenauswahldecoderschaltung empfängt die eingehenden Adressbits und aktiviert die entsprechende Auswahlleitung. Der Decoder enthält ein NOR-Gatter mit 8 Eingängen für jede Spalte, dh ein NOR-Gatter für jede Adresse. Das Foto zeigt zwei NOR-Elemente, die Spaltenauswahlsignale erzeugen (der Einfachheit halber zeige ich nur vier der 8 Eingänge). Jede Spalte verwendet eine andere Kombination aus Adresszeilen und aufgefüllten Adresszeilen als Eingabe, wobei eine andere Adresse ausgewählt wird. Die Adresszeilen befinden sich in einer Metallschicht, die auf dem Foto unten entfernt wird. Adresszeilen sind grün hervorgehoben. Um die der Spalte zugeordnete Adresse zu bestimmen, sehen Sie sich die jedem Transistor zugeordneten quadratischen Stifte an und notieren Sie, welche Adressleitungen angeschlossen sind. Wenn alle an die Transistoren einer Spalte angeschlossenen Adressleitungen auf einem niedrigen (0) Pegel liegen, wählt das NOR-Gatter diese Spalte aus.

Teil des Adressdecoders. Der Adressdecoder wählt ungerade Spalten im ROM aus und zählt von rechts nach links. Die Zahlen oben geben die Adresse an, die jedem Ausgang zugeordnet ist.Das Foto unten zeigt einen kleinen Teil des ROM-Decoders mit allen 8 Eingängen für NOR-Gatter. Sie können Binäradressen lesen, indem Sie die Verbindungen in der Adressleiste sorgfältig untersuchen. Beachten Sie das binäre Muster: a1 verbindet Änderungswerte in jeder Spalte, a2 verbindet abwechselnd alle zwei Spalten, a3 verbindet alle vier Spalten usw. A0 ist fest, weil diese Decoderschaltung ungerade Spalten auswählt; Eine ähnliche ROM-Schaltung wählt gerade Adressen aus (eine solche Trennung war erforderlich, damit der Decoder auf den Chip passt, da jede Spalte des Decoders doppelt so breit ist wie die ROM-Zelle).

Teil des Adressdecoders für den ROM-Mikrocode 8087. Der Decoder wandelt die 8-Bit-Adresse in Spaltenauswahlsignale umDie letzte Komponente des ROM ist ein Satz von Multiplexern, die 64 Ausgangsleitungen auf 8 Leitungen reduzieren. Jeder 8-zu-1-Multiplexer wählt einen seiner 8 Eingänge basierend auf der Adresse aus. Das folgende Diagramm zeigt einen der 8087-Prozessorleitungsmultiplexer, der aus acht großen Durchgangstransistoren besteht, von denen jeder mit einer der "Leitungs" -Leitungen verbunden ist. Alle Transistoren sind mit dem Ausgang verbunden. Wenn der ausgewählte Transistor eingeschaltet wird, überträgt er seinen Eingang an den Ausgang. Die Multiplexer-Transistoren sind viel, viel größer als die Transistoren im ROM, um die Signalverzerrung des ROM zu verringern. Ein Decoder (ähnlich dem zuvor betrachteten, jedoch kleiner) erzeugt acht Multiplexer-Steuerleitungen aus drei Adressleitungen.

Einer der 8-Zeilen-Multiplexer im ROM. Hier sehen Sie Schichten aus (Poly) silizium mit orange lackierten MetallverbindungenZusammenfassend speichert ROM Bits in einem Gitter. Es verwendet acht Adressbits, um eine Spalte im Raster auszuwählen. Dann wählen drei Bits der Adresse die gewünschten acht Ausgänge aus den "Zeilen" aus.

Layered ROM

Bisher habe ich ein typisches ROM-Gerät erklärt, das ein Bit pro Zelle speichert. Wie konnte der 8087 zwei Bits pro Zelle speichern? Wenn Sie genau hinschauen, enthält der 8087 ROM-Mikrocode vier verschiedene Transistorgrößen - wenn Sie das Fehlen eines Transistors als eine der Größen betrachten (6). Mit vier Optionen für jeden Transistor kann eine Zelle zwei Bits codieren, wodurch sich die Dichte ungefähr verdoppelt (7). Der aktuelle Abschnitt erklärt, wie die vier Größen von Transistoren vier verschiedene Ströme erzeugen und wie die analogen und digitalen Schaltungen des Chips diese Ströme in zwei Bits umwandeln.

Eine mikroskopische Aufnahme des Mikrocode-ROM 8087 zeigt vier verschiedene Größen von Transistoren. Dadurch kann der ROM zwei Bits pro Zelle speichern.Die Größe des Transistors steuert den Strom durch den Transistor (8). Ein wichtiger geometrischer Faktor sind die unterschiedlichen Breiten von Silizium (rosa), wo es sich mit Polysilizium schneidet (vertikale Linien), wodurch Transistoren mit unterschiedlichen Gate-Breiten entstehen. Da die Gate-Breite den Strom durch den Transistor steuert, erzeugen die vier Größen des Transistors vier verschiedene Ströme: Der größte Transistor lässt den größten Teil des Stroms durch, und es fließt überhaupt kein Strom, wenn kein Transistor vorhanden ist.

Der ROM-Strom wird in wenigen Schritten in Bits umgewandelt. Zunächst wandelt ein Pull-up-Widerstand Strom in Spannung um. Dann vergleichen drei Komparatoren die Spannung mit der Referenzspannung, um digitale Signale zu erzeugen und zu bestimmen, welche Spannung höher / niedriger ist. Schließlich wandeln die Logikgatter die Ausgangssignale des Komparators in zwei Ausgangsbits um. Dieses Muster wird achtmal wiederholt, wobei am Ausgang insgesamt 16 Bits erzeugt werden.

Schema zum Lesen von zwei Bits aus einer ROM-ZelleDas obige Diagramm führt diese Konvertierungsschritte aus. Infolgedessen wird einer der ROM-Transistoren durch die "Spalten" -Auswahlleitung und den Multiplexer (zuvor erörtert) ausgewählt, der einen der vier Ströme erzeugt. Dann wandelt ein Pull-up-Widerstand (12) den Transistorstrom in Spannung um, wodurch die Spannung von der Größe des ausgewählten Transistors abhängt. Komparatoren vergleichen diese Spannung mit drei Referenzspannungen und geben 1 aus, wenn die ROM-Spannung höher als die Referenzspannung ist. Komparatoren und Referenzspannungen erfordern eine sorgfältige Auslegung, da sich die ROM-Spannungen nur um 200 mV unterscheiden können.

Die Referenzspannungen liegen in der Mitte zwischen den erwarteten Spannungswerten des ROM, was einige Spannungsschwankungen zulässt. Die "niedrige" ROM-Spannung ist niedriger als alle Referenzspannungen, so dass alle Komparatoren 0 ausgeben. Die zweite ROM-Spannung ist höher als Ref 0, also gibt der niedrigere Komparator 1 aus. Bei der dritten ROM-Spannung geben die beiden unteren Komparatoren 1 und maximal aus die ROM-Spannung am Ausgang aller drei Komparatoren 1. Somit erzeugen die drei Komparatoren abhängig vom Transistor-ROM vier verschiedene Ausgangsmuster. Die Logikelemente wandeln dann den Ausgang des Komparators in zwei Ausgangsbits (10) um.

Das Design des Komparators ist insofern interessant, als es eine Brücke zwischen der analogen und der digitalen Welt darstellt und 1 oder 0 erzeugt, wenn die ROM-Spannung höher oder niedriger als die Referenzspannung ist. Jeder Komparator enthält einen Differenzverstärker, der die Differenz zwischen der ROM-Spannung und der Referenzspannung verstärkt. Der Ausgang des Differenzverstärkers steuert ein Gate an, das den Ausgang stabilisiert und in ein Logikpegelsignal umwandelt. Der Differenzverstärker (unten) ist eine analoge Standardschaltung. Die Stromquelle (Symbol unten) liefert Gleichstrom. Wenn einer der Transistoren eine höhere Eingangsspannung als der andere hat, fließt der größte Teil des Stroms durch diesen Transistor. Der Spannungsabfall an den Widerständen führt dazu, dass der entsprechende Ausgang niedriger und der andere Ausgang höher wird.

Ein Diagramm, das den Betrieb eines Differentialpaars zeigt. Der größte Teil des Stroms fließt durch einen Transistor mit einer höheren Eingangsspannung, was zu einem niedrigeren Ausgangssignal führt. Das Doppelkreissymbol unten ist eine Gleichstromquelle I.Das Foto unten zeigt einen der Komparatoren auf einem Chip. Metallschicht oben, Transistoren unten. Ich werde nur die Hauptpunkte dieses komplexen Schemas betrachten; Siehe Anmerkung 12 für Einzelheiten. Das Signal vom ROM und vom Multiplexer wird links geliefert. Eine Pull-up-Schaltung 12 wandelt Strom in Spannung um. Zwei große Differenzverstärkertransistoren vergleichen die ROM-Spannung mit der Referenzspannung (Eingang von oben). Die Ausgänge des Differenzverstärkers gehen an die Verschlussschaltung (auf dem Foto gestreut); Der Verschlussausgang befindet sich in der unteren rechten Ecke. Die Stromquelle des Differenzverstärkers und der Pull-up-Widerstände besteht aus Depletion-Mode-Transistoren. In jeder Ausgangsschaltung werden drei Ausgangskomparatoren verwendet, was insgesamt 24 Komparatoren ergibt.

Einer der Komparatoren in 8087. Der Chip enthält 24 Komparatoren zum Konvertieren von Spannungspegeln von einem Mehrebenen-ROM in BinärdatenJede Referenzspannung wird von einem Transistor sorgfältig ausgewählter Größe und einer Pull-up-Schaltung erzeugt. Die Spannungsreferenzschaltung ist so ausgelegt, dass sie der ROM-Signalschaltung so ähnlich wie möglich ist, sodass Änderungen bei der Chipherstellung beide Elemente gleichermaßen betreffen. Die Referenzspannung und das ROM-Signal verwenden dieselbe Lastschaltung. Zusätzlich enthält jede Referenzspannungsschaltung einen sehr großen Transistor, der mit dem Multiplexer-Transistor identisch ist, obwohl in der Referenzsignalschaltung kein Multiplexing vorhanden ist - nur um eine "Anpassung" der Schaltungen sicherzustellen. Die drei Referenzspannungsschaltungen sind bis auf die Größe des Referenztransistors (9) identisch.

Eine Schaltung, die drei Referenzspannungen erzeugt. Die Größen der Referenztransistoren liegen zwischen den Größen der ROM-Transistoren. Die Oxidschicht wurde von diesem Teil der Matrix nicht vollständig entfernt, wodurch Farbwirbel auf dem Foto auftratenUm das gesamte Puzzle zusammenzusetzen, zeigt das Foto unten die Position der Komponenten des ROM-Mikrocodes auf dem Chip (12). Der Hauptteil der ROM-Schaltung besteht aus Transistoren, die Daten speichern. Die Spaltendecoderschaltung befindet sich oberhalb und unterhalb der ROM-Daten. Die Hälfte der Decoder für die Spaltenauswahl befindet sich oben und die Hälfte unten, um ein besseres Layout zu erzielen. Der Ausgangsstromkreis befindet sich rechts. Acht Multiplexer schneiden 64 Zeilen von Zeilen auf acht. Dann treten acht Zeilen in die Komparatoren ein und erzeugen 16 Bits am Ausgang des ROM rechts. Die Referenzschaltung über den Komparatoren erzeugt drei Referenzspannungen. Unten rechts steuert ein kleiner Zeilendecoder die Multiplexer.

Firmware-ROM von Intel 8087 FPU mit den Hauptkomponenten gekennzeichnetObwohl es anfangs so aussehen mag, als wäre ein Mehrebenen-ROM halb so groß wie ein herkömmliches ROM, ist der Effekt aufgrund der zusätzlichen Schaltung der Komparatoren und aufgrund der Tatsache, dass die Transistoren selbst etwas größer sind, aufgrund der Notwendigkeit, mehrere Größen zu verwenden, nicht so spürbar. Trotzdem sparte ein mehrstufiges ROM etwa 40% des Speicherplatzes, den ein normales ROM einnehmen würde.

Nachdem ich die Struktur des ROM verstanden habe, kann ich einfach (aber mühsam) den Inhalt des ROM lesen und nur die Größe jedes Transistors unter einem Mikroskop betrachten. Ohne Kenntnis des Mikrocode-Befehlssatzes ist der Inhalt des ROM jedoch unbrauchbar.

Schlussfolgerungen

8087 « » . Intel 1981 iAPX 432.11 , 1980- . , - , , , , , , (14).

, , -. - (13). - 4 ( 16 ) , (QLC, quad-level cell). , 1980- , .

, @kenshirriff 8087. RSS-. 8087.

- 8087 1648 ( ), 16 , 26368 . , Intel .

- 8087: Intel , 40 000 , , 45 000. . , , PLA , , «» , . , .

- 8086 8087 ; . , 8087 8086 , 8087. , 8086 , . , 8087 8086 ( 8088), , 8086. , 8086, . 8087 , 8086. , 8086 8087, , . , 8087 , , . 8087 , , . 8087 8087, .

- , , , , , . , ROM, , . , 8 1/8 , 1/8 . , , (, 1 × 16) , . , «» . , Intel ; 1405 512 . , «» - 20 .

- IBM : ( , ), (link). , Xerox Alto, . , . , .

- , Hacker News , 8087 . , , .

- 1980- . Mostek : . , . Intel, ( ), . ( ) . ( ), , . Z-80 «», , , , . , , Z-80 , , , .

- . ( — .) ( , ) , . MOSFET . Wikipedia

- , -. , . , Reference 0 , . , , . : , , , . - , , , .

- : = 00, = 01, = 11, = 10. ; , , . (. «Two Bits Per Cell ROM», Stark).

- Intel iAPX 43203 (1981) , 8087. «The interface processor for the Intel VLSI 432 32 bit computer,» J. Bayliss et al., IEEE J. Solid-State Circuits, vol. SC-16, . 522-530, 1981 . 43203 - iAPX 432. Intel iAPX 432 1975 , «», Intel 1980- . iAPX 432 , Intel 8086 , 1978 . Intel 8086 , x86, iAPX 432 1986 .

- ( «Multiple-Valued ROM Output Circuits») . . (T3, T4, T5) . 4 5 , 3, ( ). ( ) T6, . ().

- - SLC ( single level cell — ), MLC (multi level cell — ), TLC (triple level cell — ) QLC (quad level cell — ). , - , , - .

- «Electronics» «Four-State Cell Doubles ROM Bit Capacity» (. 39, 9 1980 .), Intel, . Intel « » COMPCON (. 209-212, 1981 .). Intel «Multiple-valued ROM output circuits» (Proc. 14th Int. Symp. Multivalue Logic, 1984). , , — « A Survey of Multivalued Memories » («IEEE Transactions on Computers», 1986 ., . 99–106) « A review of multiple-valued memory technology » (IEEE Symposium on Multivalued Logic, 1998).

, . Gefällt dir unser Artikel? Möchten Sie weitere interessante Materialien sehen? Unterstützen Sie uns, indem Sie eine Bestellung

aufgeben oder Ihren Freunden empfehlen, einen

Rabatt von 30% für Habr-Benutzer auf ein einzigartiges Analogon von Einstiegsservern, das wir für Sie erfunden haben: Die ganze Wahrheit über VPS (KVM) E5-2650 v4 (6 Kerne) 10 GB DDR4 240 GB SSD 1 Gbit / s von $ 20 oder wie teilt man den Server? (Optionen sind mit RAID1 und RAID10, bis zu 24 Kernen und bis zu 40 GB DDR4 verfügbar).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps 1 ,

.

Dell R730xd 2 mal günstiger? Nur wir haben

2 x Intel Dodeca-Core Xeon E5-2650v4 128 GB DDR4 6 x 480 GB SSD 1 Gbit / s 100 TV von 249 US-Dollar in den Niederlanden und den USA! Lesen Sie mehr über

den Aufbau eines Infrastrukturgebäudes. Klasse mit Dell R730xd E5-2650 v4 Servern für 9.000 Euro für einen Cent?