Die vor zwei Jahren eingeführten Stratix 10 SX / GX-FPGAs von Intel

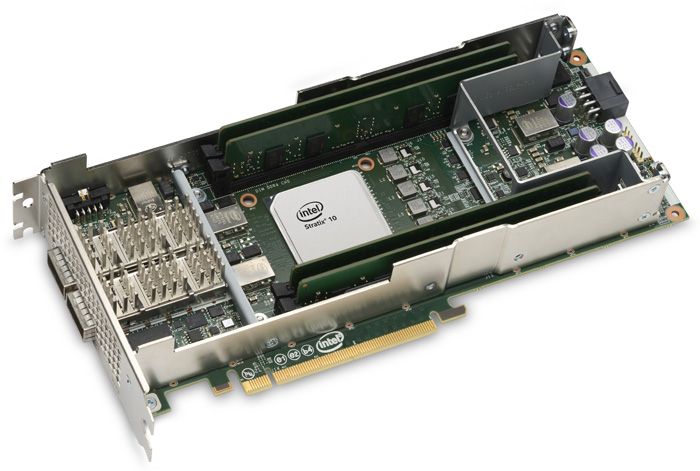

Die vor zwei Jahren eingeführten Stratix 10 SX / GX-FPGAs von Intel sind ein neues Wort auf dem Gebiet der Gate-Arrays. Sie wurden nach der damals minimalen 14-nm-Prozesstechnologie durchgeführt und waren doppelt so produktiv und 70% energieeffizient wie ihre Vorgänger. Um jedoch alle Funktionen von FPGA Intel nutzen zu können, benötigen Sie denselben fortschrittlichen „Wrapper“. Das von Intel veröffentlichte Hardware-Software-Konstrukt für die Verwendung von Stratix in Host-Systemen heißt Programmable Acceleration Card (PAC). Die

nächste Version wurde im September dieses Jahres angekündigt.

Der neue RAS basiert auf dem Intel Stratix 10 SX FPGA - dem leistungsstärksten Modell der Stratix 10-Familie. Ich werde kurz auf seine Hauptmerkmale eingehen:

- HyperFlex-Architektur

- Produktionstechnologie - 14-nm-Tri-Gate (FinFET);

- monolithische Fabrik mit 5,5 Millionen Logikelementen;

- bis zu 96 Duplex-Transceiverkanäle;

- Bandbreite von Transceivern bis zu 28,3 Gbit / s;

- Hardwarefehlerkorrektur in jedem Kanal des Transceivers;

- Hardware-Speichercontroller, die DDR4-2666-Speicher unterstützen;

- digitale Signalverarbeitungseinheiten (DSP) mit einer Gesamtkapazität von bis zu 10 TFLOPS, Energieeffizienz von bis zu 80 GFLOPS / W;

- eingebauter 4-Kern 64-Bit ARM Cortex-A53 Prozessor mit einer Frequenz von bis zu 1,5 GHz;

- Hardwarebeschleunigung der Verschlüsselung / Entschlüsselung AES-256, SHA-256/384 und ECDSA-256/384;

- Hardware-Unterstützung für die Multi-Faktor-Authentifizierung.

Die programmierbare Beschleunigungskarte selbst ist wie folgt funktionsfähig.

Das gleiche im Detail in Form einer Tabelle.

| Formfaktor | PCIe Gen3 x16

Volle Höhe, 3/4 Länge, doppelter Schlitz |

| Die Erinnerung | 32 GB DDR4 (4 x 8 GB) ECC |

| Netzwerkschnittstellen | 2X QSFP + bis zu 100 Gbit / s |

| Serviceschnittstelle | USB 2.0 zum Debuggen und Programmieren |

| Steuerungssteuerung | Intel MAX 10 FPGA Baseboard Management Controller (BMC)

• Lesen von Temperatur- und Spannungsdaten

• PLDM (Platform Level Data Model)

• IPMI 2.0 |

| Energieverwaltung | Intel Enpirion Power Solutions (Echtzeit-Telemetrie und Statusüberwachung) |

| Software | • Beschleunigungsstapel für Intel Xeon-CPU mit FPGA

• FPGA-Schnittstellenmanager

• Intel Quartus Prime Pro Edition

• Intel FPGA SDK für OpenCL |

Die Karte wird Anfang nächsten Jahres als Teil der Serverprodukte der OEM-Partner von Intel (insbesondere Hewlett Packard Enterprise) erhältlich sein.