Das Entwerfen elektronischer Geräte unter Verwendung schneller DDR-SDRAM-Speichermodule erfordert besondere Aufmerksamkeit für die Signalintegrität. Der Artikel spricht über ein modernes Modellierungswerkzeug zur Lösung solcher Probleme.Heute ist fast die gesamte moderne Elektronik mit Speichermodulen ausgestattet. Server, Computer, Smartphones, Spielekonsolen, GPS-Navigatoren und die meisten anderen Geräte basieren auf Prozessoren und FPGAs. Solche Geräte erfordern einen Hochgeschwindigkeitsspeicher mit großer Kanalbandbreite oder einen DDR-Speicher (Dual Frequency Memory). Mit jeder neuen Generation von DDR-SDRAM (synchroner dynamischer Speicher mit wahlfreiem Zugriff und doppelter Datenübertragungsgeschwindigkeit) werden Datenaustauschgeschwindigkeit, Kapazität und Speicherverbrauch reduziert.

Beim Entwurf der Leiterplatten von Geräten mit DDR-Speicher können eine Reihe von Schwierigkeiten auftreten, von denen eine das Problem der Signalintegrität ist. In diesem Artikel werden die Probleme bei der Gewährleistung der Integrität von Signalen in Geräten mit DDR-Speicher erläutert.

Rauschen und Jitter des digitalen Datensignals

Beim Empfangen / Senden des Taktsignals des Speicherbusses von der Steuerung zur Mikroschaltung können verschiedene Störungen aufgrund des eigenen Jitters der Sender und Empfänger, Verluste in den Übertragungsleitungen, Rauschen und Störungen auftreten. All dies führt zum Auftreten von Jitter und zu einer Verzerrung der Form des digitalen Schnittstellensignals.

Jede unerwünschte Energie, die einem idealen Signal hinzugefügt wird, kann als Rauschen betrachtet werden. Dies kann durch Störungen durch benachbarte Leitungen, einen schlecht ausgelegten Übertragungskanal, eine inkonsistente Impedanz und andere Faktoren verursacht werden, die zu einer Unschärfe der Impulsfront führen. In Abwesenheit von Rauschen ist das tatsächliche Signal mit dem Ideal identisch.

Jede Abweichung von der idealen Wellenform wirkt sich auf deren Integrität aus. Zeitabweichungen (Jitter) und Amplituden- / Spannungsabweichungen (Rauschen) wirken sich ebenfalls auf die Systemleistung aus. Wenn Sie die Integrität der Signale nicht sicherstellen, verwendet das DDR-System die falschen Informationen, wodurch die Intensität der Bitfehler BER (Bit Error Rate) erheblich erhöht wird. Letztendlich wird das System falsch und ineffizient arbeiten.

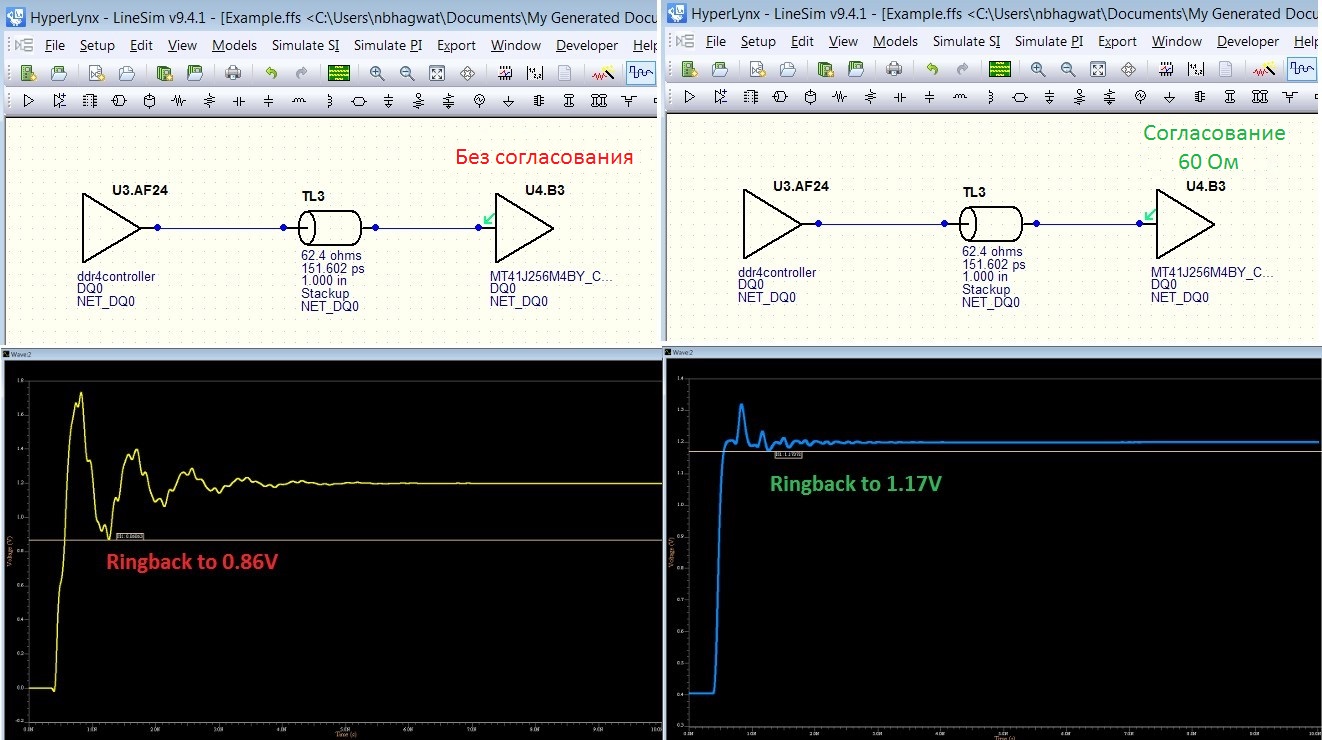

Betrachten Sie ein bestimmtes Beispiel. Wenn der Techniker den Sender an einen inkonsistenten Empfänger anschließt, der sich in einiger Entfernung von ihm befindet, ähnelt die Wellenform der in Abbildung 1a gezeigten: Hier sehen Sie deutlich das „Klingeln“ bei 0,86 V und störend steigende Emissionen bei 1,75 V bei einem Signal von 1,2 V. All dies kann zu einer Fehlfunktion der DDR4-Logik führen. Wenn die Leiterplatte mit einer solchen Topologie ausgelegt ist, treten mit einer Wahrscheinlichkeit von 100% Fehler im Datenstrom auf, die wiederum zu einem fehlerhaften Betrieb des Systems führen können .

Theoretisch ist es möglich, Probleme mit „Klingeln“ und Emissionen zu lösen, indem die Länge der Übertragungsleitung verringert wird. In der Praxis funktioniert dies jedoch leider nur selten. Am effektivsten ist es, den Empfänger / Sender anhand der Impedanz anzupassen, wodurch der Rauschpegel abnimmt und die Signalform viel besser wird (siehe Abb. 1b).

Abb. 1. Eine Topologie mit Problemen mit der Signalqualität: a) vor der Koordination b) nach der Koordination

Abb. 1. Eine Topologie mit Problemen mit der Signalqualität: a) vor der Koordination b) nach der KoordinationIn diesem Zusammenhang stellt sich die Frage, welche Zulassungsbewertung verwendet werden soll und wie sie berechnet werden soll, da bereits eine geringfügige Änderung der Bewertung die Systemleistung erheblich beeinträchtigen kann. Die einzige Möglichkeit, dieses Problem zu lösen, besteht darin, insbesondere die in HyperLynx verwendeten interaktiven Abstimmungsassistenten zu simulieren.

Timing-Probleme in DDRx

Da parallele Busse, die bei Gigahertz-Frequenzen wie DDR3 / 4 arbeiten, zunehmend beim Entwurf von Leiterplatten verwendet werden, sind Signalintegritätsprobleme besonders akut. DDR3 SDRAM unterscheidet sich beispielsweise in Bezug auf Geschwindigkeit und Frequenz erheblich von DDR2: Die maximale Taktfrequenz von DDR2 beträgt 800 MHz und die maximale Frequenz von DDR3 beträgt 1600 MHz. Aufgrund der Reduzierung der Versorgungsspannung der Zellen gelang es den Entwicklern des neuen RAM-Typs, den Energieverbrauch um bis zu 15% zu senken, was angesichts der beeindruckenden Leistung von DDR2 als echter Durchbruch bezeichnet werden kann. DDR3 verwendet eine Netzwerk-Fly-by-Befehls- / Adress- / Steuerbustopologie mit ODT-Übereinstimmung (Intra-Module). Gleichzeitig erzeugt DDR3 neue Probleme der Signalintegrität, insbesondere im Zusammenhang mit ODT-Schaltungen, höheren Datenraten und Zeitverzerrungen.

Trotz der Tatsache, dass es Controller gibt, die eine automatische Lese- / Schreibkalibrierung durchführen und Zeitintervalle optimieren, muss der Entwickler das richtige Timing sicherstellen. Die Zeitgrenzen in den DDR3-Schnittstellen sind so klein, dass der empirische Ansatz zur Optimierung nicht mehr ausreicht. Um den Betrieb der Schnittstelle bei hohen Geschwindigkeiten zu gewährleisten, ist eine detaillierte Analyse der Schaltung erforderlich.

Solche komplexen zeitlichen Beziehungen sind ohne die Hilfe zusätzlicher Werkzeuge schwer zu analysieren. Um mögliche Probleme im Allgemeinen zu identifizieren und zu beseitigen oder komplexe Zeitbeziehungen zu berechnen, müssen Ingenieure eine Kausalzusammenhangsanalyse durchführen, was eine komplexe und zeitaufwändige Aufgabe ist.

Solche Designprobleme führen häufig zu Verzögerungen bei der Projektplanung und verlängern infolgedessen die Zeit, die das fertige Produkt benötigt, um auf den Markt zu kommen. Fortschrittliche, leistungsstarke Simulationswerkzeuge können Ingenieuren helfen, Fehler schnell zu finden und zu korrigieren, indem sie Signale auf ein akzeptables BER-Niveau optimieren.

Signalintegritätsanalyse von DDR-SDRAM-Systemen

Das JEDEC Semiconductor Engineering Standardization Committee hat eine Liste von Anforderungen genehmigt, die bei der Entwicklung von Qualitätsprodukten zu beachten sind. Es ist wichtig, dass DDR-SDRAMs diese Anforderungen erfüllen, um einen ordnungsgemäßen Betrieb sicherzustellen und Probleme mit der Signalintegrität zu vermeiden. Die Durchführung aller erforderlichen Messungen und Berechnungen ist jedoch häufig mit vielen Schwierigkeiten verbunden.

Manchmal können diese Berechnungen ganz vermieden werden, indem die vom Controller-Hersteller bereitgestellten Layout-Anweisungen genau befolgt werden. Was aber, wenn solche Empfehlungen aufgrund verschiedener Einschränkungen in bestimmten Projekten nicht umgesetzt werden können? Was tun, wenn viel Zeit benötigt wird, um sicherzustellen, dass das Projekt alle Empfehlungen und Anforderungen erfüllt? In solchen Situationen müssen Sie Tools verwenden, um das Projekt schnell zu überprüfen, bevor Sie es in Produktion nehmen.

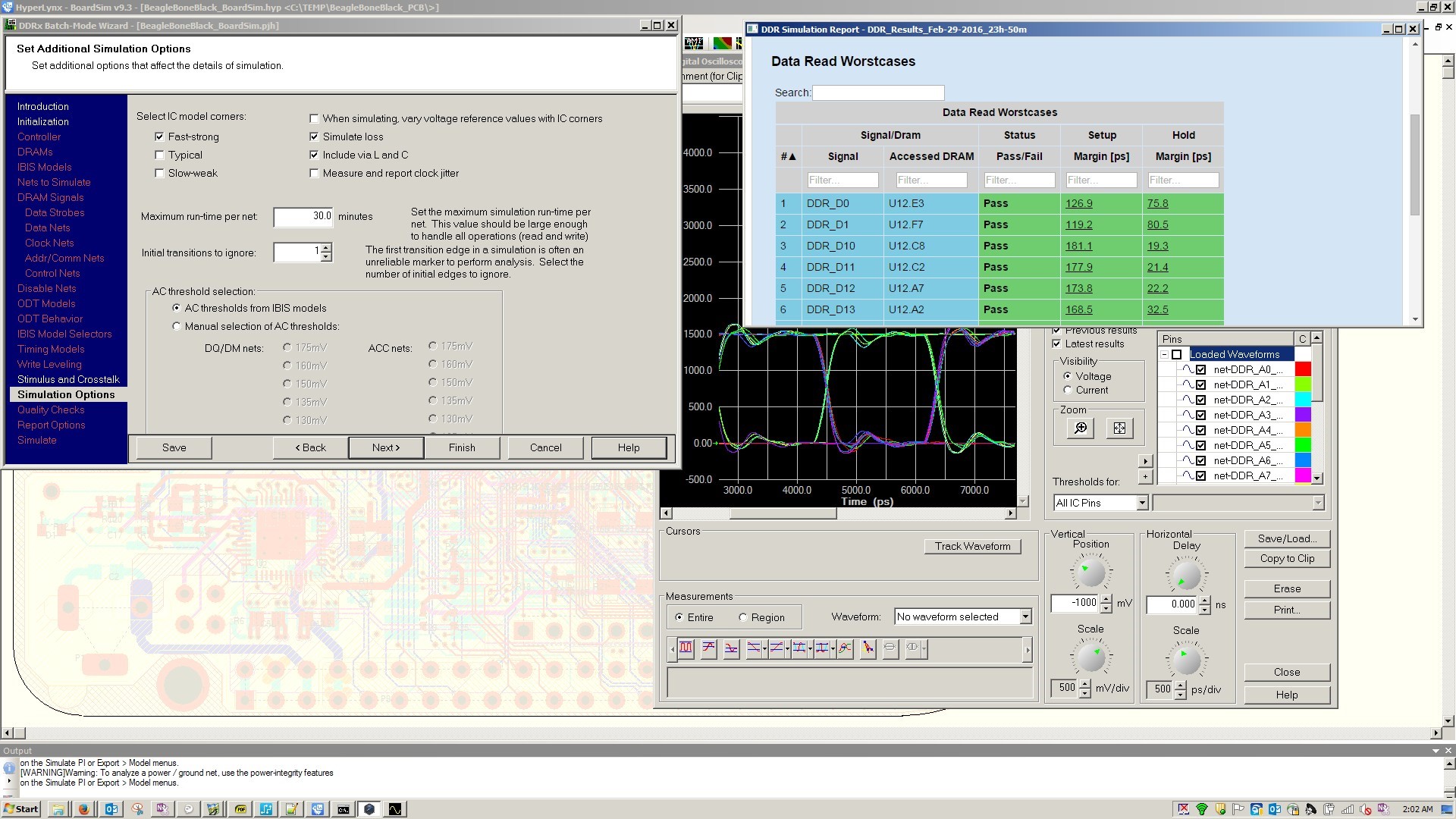

Mit HyperLynx DDR (siehe Abbildung 2) können Sie den gesamten DDR-Kanal in einer Iteration simulieren. Dazu müssen Sie nur die entsprechenden Gerätemodelle binden, die auf den Websites der Hersteller verfügbar sind. Danach dauert die Rüstzeit für die Simulation nur noch zehn Minuten, wodurch eine weitere Modellierung ohne Verzögerung möglich ist.

Abb. 2. Modellierung mit dem HyperLynx DDR Interactive Helper

Abb. 2. Modellierung mit dem HyperLynx DDR Interactive HelperDer Einrichtungsprozess ist intuitiv einfach, da alle zum Einrichten der Simulation erforderlichen Parameter vom Assistenten interaktiv angefordert werden. Der Benutzer gibt einfach relevante Informationen ein, z. B. die Auswahl von IBIS-Modellen für Steuerungen und Speichergeräte, Baudraten für Lese- / Schreibzyklen, ODT usw. Alle erstellten Konfigurationen können für die zukünftige Verwendung gespeichert werden, wodurch die Einrichtungszeit in zukünftigen Projekten verkürzt wird. Vor oder nach der Ablaufverfolgung können Simulationen durchgeführt werden, um die Anforderungen für den PCB-Stapel zu ermitteln.

Analyse der Simulationsergebnisse

Die Simulation umfasst die Analyse der Signalintegrität und die Synchronisation des gesamten DDR-Busses. Nach Abschluss des Simulationsprozesses wird ein Bericht erstellt, der Daten zum Durchgang (nicht zum Bestehen) von Prüfungen gemäß den Konfigurationsinformationen und den Daten enthält, die im interaktiven Assistenten eingegeben wurden. Die Ergebnisse können gefiltert und ordnungsgemäß organisiert werden, um Zeit- und Signalintegritätsprobleme in Datenlese- / Schreibzyklen, in Adress- und Befehlsbussen oder in Differenzschaltungen sorgfältig zu untersuchen. Alle Berichtsergebnisse sind an die entsprechenden Simulationsdaten gebunden, um schnell auf das Tool zum Anzeigen grafischer Signalverläufe von Signalen zugreifen zu können.

Die vom DDRx-Assistenten erstellten Simulationsdaten im Batch-Modus können auf der Festplatte gespeichert werden. Auf diese Weise können Sie mit dem HyperLynx-Oszilloskop mehrere Schaltkreise gleichzeitig simulieren und die Probleme der Signalintegrität im Offline-Modus detailliert untersuchen.

Fazit

DDR SDRAM eröffnet neue Möglichkeiten bei der Entwicklung elektronischer Geräte. Wie bei anderen Hochgeschwindigkeitsschnittstellen weist die Verwendung von DDR-Speicher mehrere Funktionen auf. Das Problem der Signalintegrität muss sorgfältig untersucht werden, um unnötige und kostspielige Iterationen bei der Herstellung von Produkten zu vermeiden. Die Modellierung ist eine hervorragende Möglichkeit, dieses Problem zu lösen. Sie ermöglicht es, Effekte auf Platinenebene zu berücksichtigen, z. B. Änderungen der Impedanz und Zeitverzögerungen, und bietet eine umfassende Kontrolle über die Speicherschnittstelle. Leistungsstarke Analysetools tragen dazu bei, dass Projekte den JEDEC-Empfehlungen entsprechen und dass das Endprodukt mit hoher Leistung und Zuverlässigkeit funktioniert.

HyperLynx DDR kann von vielen CAD-Leiterplattenkonstruktionsunternehmen, einschließlich PADS und Xpedition, gemeinsam genutzt werden.

Dieser Artikel wurde in der Zeitschrift MODERN ELECTRONICS Nr. 7, 2018 (www.soel.ru) veröffentlicht.