Technologisches Design

DFM - das sind die Prinzipien der Entwicklung und des Projektmanagements, die auf die erfolgreiche Produktion des fertigen Produkts abzielen. Das Befolgen dieser Grundsätze soll die Produktions- und Testdauer von Fertigprodukten verkürzen und gleichzeitig die Qualität verbessern. DFM beginnt lange bevor das Design in der Phase der Diskussion der technischen Spezifikationen von der Größe der Serie abhängt und die Kosten für Design, Herstellung und Prüfung beeinflusst. Über DFM schrieb zum Beispiel

hier über Habré. Heute werden wir über die Funktionsprüfung einer Leiterplatte sprechen und deren Vorbereitung für diesen Zweck beschreiben. (Verkehr)

Beim industriellen Design von Leiterplatten verfügt DFM auch über folgende Funktionen: DRC (Design Rule Checking) zur Überprüfung technologischer Einschränkungen, CAM (Computer Aided Manufacturing) zur Vorbereitung der Leiterplattenproduktion und DFA (Design For Assembly) zur Optimierung der Montage. Diese Funktionen können in CAD-Software (PCB Design Automation Systems) integriert oder als separate Software geliefert werden. Hier können wir

Vayo erwähnen, das über Softwaremodule zum Testen von Software verfügt: DFM Expert (wird auch zur Analyse von Teststandorten verwendet) und Test Expert (zur automatischen Bewertung der Testbarkeit von Produkten und zur Vorbereitung von Daten für elektrische Testgeräte).

Wir verwenden die CAD-Software Altium Designer (AD). Sie können Kontrollpunkte (CT) als Bibliothekskomponenten erstellen, die Regeln für die Platzierung der CT im Diagramm festlegen und beim Entwerfen einer Topologie CTs vor der Ablaufverfolgung platzieren. Ein ähnlicher Ansatz kann in anderen modernen CAD-Programmen angewendet werden.

Elektrische Kontaktmethoden für Platinentests

Vier können unterschieden werden:

1) Handbuch

Die klassische Methode, bei der ein Spezialist mit Handsonden nacheinander alle Schaltkreise testet. Die Effizienz hängt von den Qualifikationen und persönlichen Qualitäten des Darstellers ab

2) "Das Nagelbett"

(Aus dem englischen "Nagelbett", auch "Kontaktfeld", "Nadeladapter", "Matrixtester" (MT)). Das Verfahren setzt das Vorhandensein einer Verbindungsvorrichtung mit federbelasteten Kontakten (Pogo-Pins) gegenüber den Kontrollpunkten auf der Platine voraus. Der Tester kann Teil der Produktionslinie sein:

Oder sei ein Desktop-Gerät,

in verschiedenen mechanischen Ausführungen: Indem sichergestellt wird, dass alle Knoten des getesteten PP von Pog-Pins berührt werden, kann ein Testabdeckungsgrad nahe 98% erreicht werden.

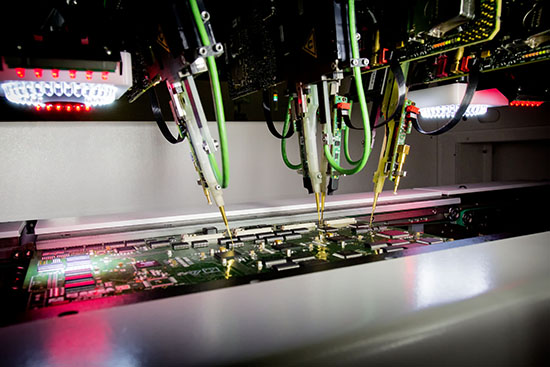

3) "Fliegende Sonden"

(Aus dem Englischen. "Fliegende Sonden"). Die Ausrüstung für das Flugsondenverfahren weist mehrere (manchmal mehrere zehn) bewegliche Köpfe auf, von denen jeder eine Sonde mit axialem Antrieb aufweist. Die Sonden stehen gemäß einem zuvor vom Bediener erstellten Programm in Kontakt mit der Platine, wodurch Strom, Signale geliefert und Messungen durchgeführt werden.

Es wird in der Linie gebaut oder separat verwendet, abhängig von den Merkmalen des Produkts und der ausgewählten Testmethode. Es sieht

so aus , es klingt wie eine riesige Nähmaschine.

4) "Fliegende Matrizen"

(Aus dem englischen "Flying Grid", auch "Flying Bed of Nails"). Ein Hybrid der beiden vorherigen Verfahren, wenn eine Sondenmatrix auf einem sich bewegenden Schlitten platziert ist und jede Sonde auch einen unabhängigen Achsantrieb haben kann. Eine allgemeine Vorstellung davon, wie dies funktioniert, erhalten Sie aus dem

Video.Weitere Informationen zu den verschiedenen elektrischen Kontaktmethoden finden Sie

hier .

In der Tabelle sind einige Vor- und Nachteile der vier Methoden aufgeführt:

Gründe für die Wahl des Matrixtests und seiner Funktionen

Unter realen Bedingungen der russischen Realität muss der Kunde zwischen den ersten beiden Zeilen der Tabelle wählen, da die Ausrüstung für die letzten beiden Methoden nicht billig ist (ab 15 Millionen Rubel pro Gebraucht) und in der heimischen Produktion immer noch selten ist. Aufgrund der geringen Kosten wird normalerweise die manuelle Methode bevorzugt, bei der nur ein Entwickler oder ein Spezialist vergleichbaren Niveaus ein Produkt vollständig testen kann. Infolgedessen können Produkte die Produktion ohne elektronische Tests vollständig verlassen oder sie können nur durch Einschalten von „Rauch“ überprüft werden, häufig bereits auf Kundenseite. In besseren Fällen finden sich manuelle Tests mit Snap-Ins in der Produktion und seltener automatisierte Tests an Matrixständern.

Die Notwendigkeit eines Standes entstand bei uns während des

Blueberry- Projekts. Dieses Produkt verfügt über vier präzise Analogausgänge mit individueller Kalibrierung, sodass das Testen selbst für einen erfahrenen Ingenieur eine zeitaufwändige Aufgabe ist. Wir wollten den Prozess so weit vereinfachen, dass die Möglichkeit menschlicher Fehler ausgeschlossen, das Verfahren auf rein mechanische Vorgänge reduziert und gleichzeitig sichergestellt wurde, dass die Funktionsprüfung jedes Produkts aus einer experimentellen Charge (1020 Stk.) Die Matrixprüfung teurer war als die manuelle Prüfung, aber nur auf diese Weise konnte die korrekte Funktionsweise der einzelnen Produkte gewährleistet werden Geräte.

Ein wichtiger Faktor bei der Auswahl einer Testmethode kann die Möglichkeit einer vorläufigen Optimierung der Platzierung von Kontaktflächen (im Koordinatengitter) in der getesteten Software und deren Minimierung sein. Eine solche Analyse sollte vor Beginn der PCB-Verdrahtungsphase durchgeführt werden. Ziel ist es, eine höchstmögliche Testabdeckung zu erzielen.

In unserem Fall hat dies nicht funktioniert - die Überarbeitung des Boards zum Zeitpunkt der Entscheidung war bereits die 4., wir mussten kleine Kontaktflächen fast zur fertigen Topologie hinzufügen.

Mit abnehmender Anzahl von Pads und Pogo-Pins steigt die Komplexität der Entwicklung von Software für Funktionstests. Gleichzeitig reduziert eine Verringerung der Anzahl der Pog-Pins insgesamt die Kosten für die Ausrüstung und die für ihre Herstellung erforderliche Zeit.

In unserem Fall (für 42 Pogo-Pins und 32 Tests) erforderte die Entwicklung 560 Standardstunden, von denen 200,5 Stunden mit 2 Revisionen der Hardware, 31 - Versorgung und 328,5 - Programmierung belegt waren.

Wenn nicht genügend Platz für die Pads auf der Unterseite der Leiterplatte vorhanden ist, z. B. bei dichter bilateraler Installation von Komponenten, können Kontaktpads zum Testen auch auf der Oberseite der Platine platziert werden. Es sollte jedoch berücksichtigt werden, dass die Kosten für die Entwicklung eines zweiseitigen Testers 1,5 bis 2 Mal höher sind als für einen Einweg-Tester.

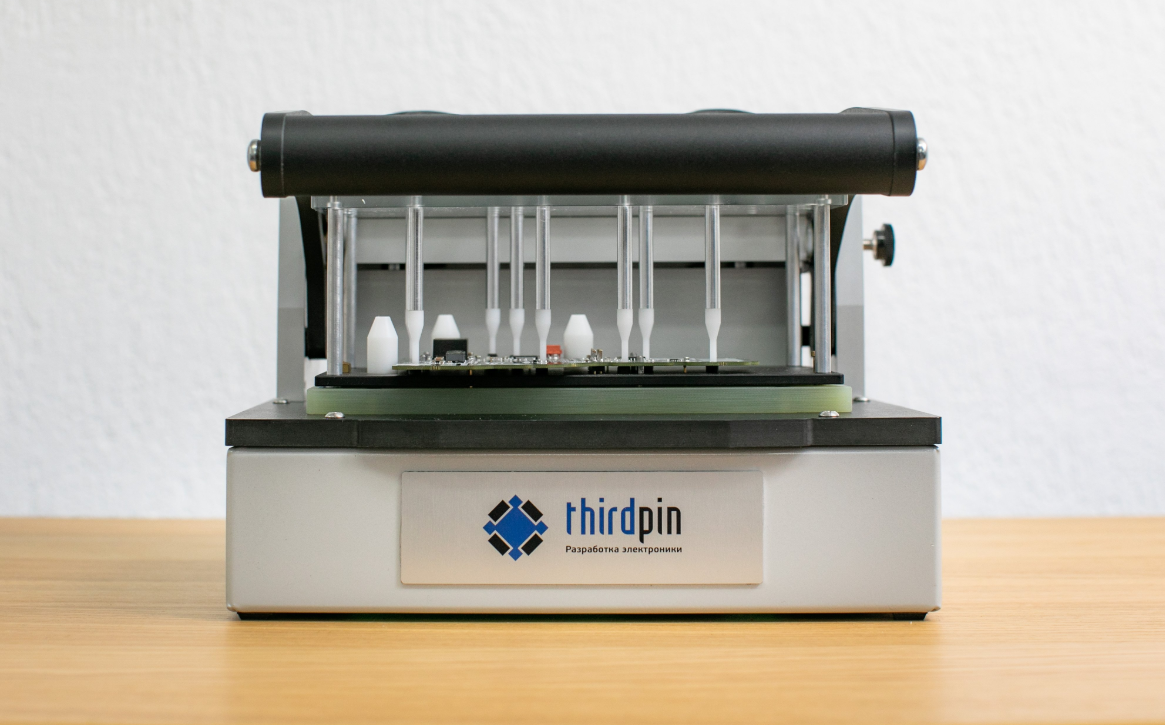

Matrix Tester Ingun MA 260 / F.

Bilder des gekauften Ingun MA 260 / F-Snap-Ins und der Blueberry-Platine sind in den Abbildungen dargestellt. Die Beschreibung des Testers finden Sie

hier .

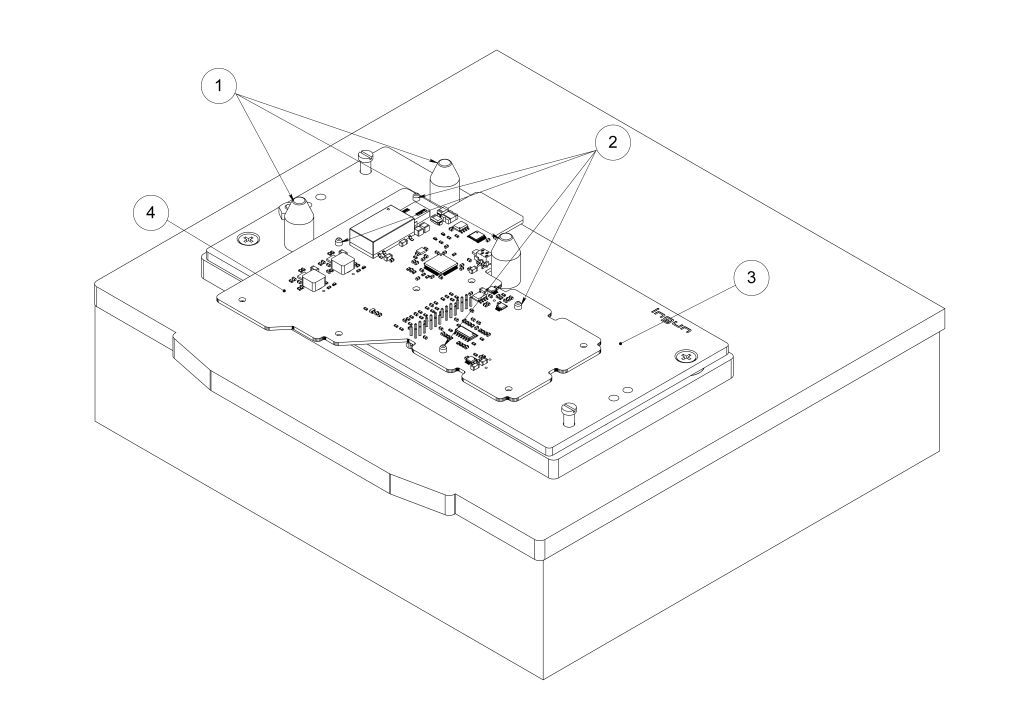

Schnittansicht eines fertigen Gerätes mit einer Platine:

In der Zeichnung sehen wir: 1 - die Druckplatte, 2 - den Druckstab (durch den der obere Teil des Geräts auf die Platine drückt), 3 - die getestete Blueberry-Leiterplatte, 4 - die bewegliche Platte, 5 - die Sondenplatine, 6 - die Testplatine, 7 - Sondenplatte und 8 Pogo-Pins. Um die „Blueberry“ -Platte zu testen, haben wir die von Ingun gelieferten Werkzeugteile in Form von Rohlingen fertiggestellt - eine Druckplatte, eine bewegliche Platte und eine Sondenplatte - und in Altium Designer eine Sondenplatte und eine Testplatte entwickelt.

Unten sehen Sie ein Bild des getesteten Blueberry-Boards (Punkt 4) in Bezug auf die vorläufigen Positionierungsstangen (Punkt 1). Pos. 3 in dieser Figur ist eine bewegliche Platte und Pos. 2 - Zentrierstangen (PCB-Fänger). Der Installateur installiert die Platine ohne zu zielen bis zum Anschlag der Vorpositionierungsstangen (Pos. 1), gibt dann die Platine frei und landet auf genaueren Zentrierstangen. Es ist schwierig, die Platine ohne vorherige Positionierung schnell auf den Zentrierstangen zu installieren.

Für eine zuverlässige Platzierung der Platine auf dem MT muss die Platine mindestens drei Löcher zum Positionieren von Kontakten aufweisen (sie werden auch als Präzisionsmontagestifte bezeichnet), von denen zwei diagonal platziert werden sollten. Der Durchmesser solcher Löcher beträgt üblicherweise nicht weniger als 3,25 mm. Der Abstand von der Kante des Positionierkontakts zur Kante des PP beträgt mindestens 3,18 mm und zum nächsten Kontaktfeld mindestens 5 mm.

Pogo-Stifte müssen gemäß den Arten der Kontrollpunkte auf der Leiterplatte ausgewählt und separat bestellt werden (sie sind nicht im Testkit enthalten). Sie können die Landetiefe von Pogo-Pins für Komponenten mit einer nicht standardmäßigen Höhe variieren. Es wird jedoch empfohlen, dies zu vermeiden (Hinzufügen zusätzlicher Kontrollpunkte auf der Leiterplatte). Die Genauigkeit des Erhaltens von Pogo-Pins an Kontrollpunkten (CT) wird basierend auf der Genauigkeit des Testers und den Toleranzen der Größen und Formen der modifizierten Testplatten bestimmt. Pogo-Pins-Entwickler geben einige Empfehlungen zu CT-Größen. Auch über die Wahl der CT-Größen ist hier gut geschrieben.

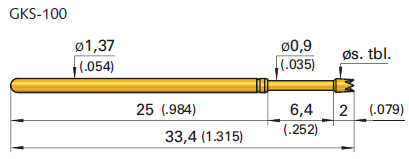

Gebrauchte Pogopins (Pogopins, federbelastete Kontakte)

Es gibt viele Arten von Pogo-Pins für Tester, die sich in Größe, Form und Relief der Kontaktfläche (flach, kronenförmig, nadelförmig, konisch und andere), des Pogo-Pin-Materials und der Beschichtung unterscheiden und deren Verschleißfestigkeit gewährleisten. Die richtige Auswahl von Nadeln mit Köpfen, die einem bestimmten Kontaktpunkt entsprechen, gewährleistet eine hohe Zuverlässigkeit des Kontakts während des Testens und die Haltbarkeit der Pogo-Stifte selbst. Zum leichteren Austausch werden Kontaktsonden normalerweise in Halterungen montiert.

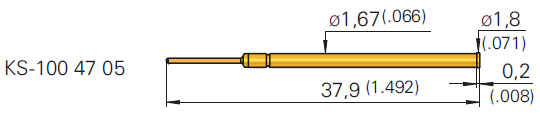

In MT für die Chernik-Software werden die Pogo-Stifte Ingun GKS-100 314 130 A 1500 und die Pogo-Stifthalter KS-100 47 05 verwendet.

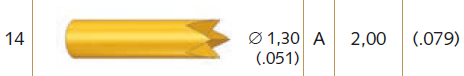

Pogo-Pin GKS-100: Tipp 14 Pogo-Pin GKS-100:

Tipp 14 Pogo-Pin GKS-100: KS-100 Halter für Pogo-Pin GKS-100:

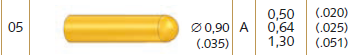

KS-100 Halter für Pogo-Pin GKS-100: Spitze 05 des Halters KS-100

Spitze 05 des Halters KS-100

Weitere Pogo-Pins finden Sie unter den Links:

Ingun und

FEINMETALL .

Für verschiedene Kontrollpunkte auf dem PP werden verschiedene Arten von Pogo-Pins verwendet. Kontrollpunkte können sein: Kontaktflächen (KP) auf der Oberfläche des PP mit der Öffnung der Schutzmaske (Typ KP für die smd-Komponente) durch metallisierte Löcher und Stiftleitungen der in die Löcher gelöteten Komponenten. Es ist erwähnenswert, dass als CT eine Durchkontaktierung verwendet werden kann, inkl. und maskiert.

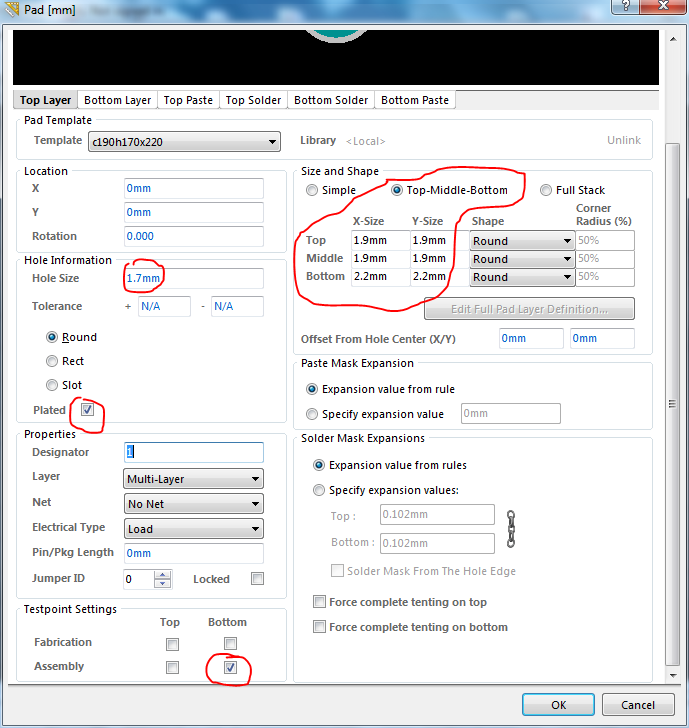

Ein Beispiel für die Erstellung eines Kontrollpunkts in Form eines Durchgangslochs in der Platine

Das Erstellen eines CT in Form eines Durchgangslochs in AD umfasst:

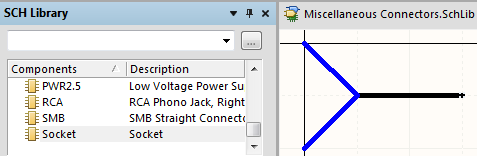

1. Erstellen eines Schaltungselements (UGO) in der Bibliothek .schlib. CTs in einem Diagramm werden häufig als Socket dargestellt, und die Standardbibliothek MiscellaneousConnectors.schlib verfügt über ein Schaltungselement namens Socket. Es reicht aus, es in Ihre Bibliothek zu kopieren, ihm einen neuen Namen zu geben, den Parameter Default Designator beispielsweise in KT zu ändern. Damit die CTs nicht in der Liste der Elemente enthalten sind, müssen Sie den Typ Standard (Keine Stückliste) angeben.

2. Es ist

2. Es ist praktisch, mit dem Befehl Pad einen Footprint (in der .pcblib-Bibliothek) zu erstellen. Für Pogo-Pin KS-100 aus Glasfaserlaminat empfiehlt FR-4 Ingun die Verwendung eines Lochs mit einem Durchmesser von 1,7 mm. Betrachten Sie das Beispiel von KP für mehrschichtiges PP. Die Größe des KP von der Testseite (für den Kontakt mit dem Pog-Pin) beträgt 1,7 + 0,5 = 2,2 (wobei 0,5 die doppelte Mindestleiterbreite gemäß Genauigkeitsklasse 3 ist). Wir werden von unten einen großen KP erstellen, wobei zu berücksichtigen ist, dass sich die Stiftkomponenten häufiger auf der Oberseite der Platine befinden und sich die Stifte, die während des Tests verwendet werden, entsprechend unten befinden. In den übrigen Schichten beträgt der Durchmesser des Getriebes 1,9 mm. Das Loch muss metallisiert sein. Unten links gegenüber der Baugruppe unten setzen wir ein Häkchen.

3.

3. Anschließend müssen Sie den Footprint mit dem Schaltungselement verbinden.

Hinzufügen von Haltepunkten im Diagramm

In AD wird die Standardposition des Stromwandlers in allen Stromkreisen angenommen. Um die Anzahl der Pogo-Pins zu minimieren, werden Stromwandler nur im Stromversorgungskreis und in Stromkreisen installiert, die an analoge und digitale externe Schnittstellen angeschlossen sind (mit Ausnahme derjenigen, die mit JTAG getestet werden können). Wie bereits erwähnt, können die Pogo-Stifte das Getriebe auf der Oberfläche des PP durch metallisierte Löcher und Stiftleitungen der in die Löcher gelöteten Komponenten berühren. In der Phase des Entwurfs der Schaltung ist es möglich, Stiftleitungen von Bauteilen (in Löcher eingelötet) vorzusehen, wenn die Steigung der Leitungen der Gehäuse elektronischer Komponenten (EC) dem Schritt des Platzierens von Pogo-Stiften entspricht und alle ECs mit Stiftanschlüssen auf einer Seite (Testseite) platziert werden. Dies ist jedoch nicht immer bequem, einschließlich aufgrund der Tatsache, dass der Falltyp manchmal während der Entwicklung der Topologie ausgewählt (oder geändert) wird. In der Phase der Entwicklung des Schemas wird empfohlen, die maximal erforderliche Anzahl von CTs festzulegen und dann während der Entwicklung der Topologie überschüssige CTs zu entfernen.

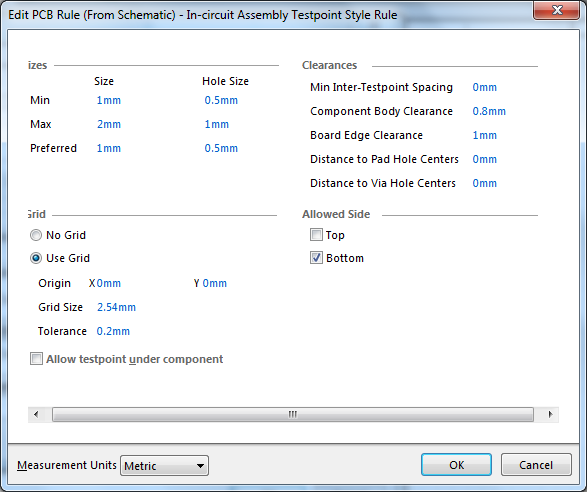

Um der Schaltung einen Stromwandler hinzuzufügen, werden Standardmethoden zum Platzieren eines UGO verwendet. Für das End-to-End-Design können wir Designregeln in der Schaltung festlegen (zur anschließenden Überprüfung mittels DRC). Die Regeln für die Position von Stromwandlern können bequem für die Klasse der Stromkreise (einschließlich der getesteten Stromkreise) festgelegt werden. In einer Schaltung kann eine Schaltungsklasse mit der Direktive Place / Directive / Net Classes erstellt werden. Die Direktive kann auf jedem Stromkreis (der in der Klasse enthalten sein muss), auf dem Bus (dafür müssen jedoch zuerst alle getesteten Stromkreise in den Bus kombiniert werden) und auf der Decke platziert werden. Eine Decke ist ein polygonaler Bereich (Polygon), der mit dem Befehl Platzieren / Direktive / Decke erstellt wurde (wir wählen alle Ketten für die Klasse mit einem Polygon aus). Es ist nicht erforderlich, eine Direktive auf dem Bus zu installieren. Legen Sie einfach die Option "Netzklassen für Busse generieren" auf der Registerkarte "Klassengenerierung" in den Projektoptionen fest. Es ist bequemer, Klassen in der Softwaretopologie zu erstellen, aber in AD gibt es Probleme mit automatischen Änderungen (beim Aktualisieren des Schemas aus der Topologie), wenn mit in der Topologie erstellten Klassen gearbeitet wird. Daher erstellen wir Klassen im Schema. Um eine Regel zum Platzieren von CT in den Klasseneigenschaften (in der Direktive Net Classes) zu erstellen, klicken Sie auf die Schaltfläche Als Regel hinzufügen und dann auf die Schaltfläche Regelwerte bearbeiten. Wählen Sie in der Kategorie Testpoint die Option Assembly Testpoint Style aus und klicken Sie auf OK. Legen Sie dann die Regeln für die CT-Platzierung fest. Im Diagramm ist der Regelsatz für CT etwas kleiner als in der Topologie. Hier können Sie die Größe der Punkte, den Rasterabstand der Testpunkte (mit Toleranz), die Lücken und die Seite der Platzierung angeben. Da wir bereits in der Entwurfsphase über eine Testvorbereitung nachdenken, ist es besser, die CT im Raster zu platzieren. Für KS-100-Halter zeigt die Dokumentation einen Abstand von 2,54 mm. Der Abstand des Komponentenkörpers (der Abstand zwischen dem Kontrollpunkt und dem Komponentenkörper) ist auf 0,8 mm und der Abstand der Plattenkanten auf 1 mm eingestellt. Die verbleibenden Lücken müssen nicht angegeben werden, wenn wir den CT im Raster platzieren.

Damit die in der Schaltung erstellten Schaltungsklassen in die Topologie der Software übertragen werden können, muss die Option "Netzklassen generieren" auf der Registerkarte "Klassengenerierung" in den Projektoptionen aktiviert sein (normalerweise standardmäßig aktiviert).

Kontrollpunkte auf der Platine platzieren

Wir platzieren die Stromwandler vor dem Verfolgen, aber nachdem wir alle anderen Komponenten auf der Platine platziert haben. Vor dem Platzieren müssen Sie den Rasterabstand des CT einstellen (in unserem Fall 2,54 mm).

Bevor wir den CT platzieren, gehen wir zu den Entwurfsregeln und sehen dort, dass der Regelsatz für den Testpunktstil für Baugruppen zwei Regeln enthält: den Testpunktstil für schematische Baugruppen, den wir im Diagramm für die Klasse festgelegt haben, und die Standardregel für Baugruppentestpunkte, die für alle Ketten gilt. Wir entfernen die Standardregel. Die Einstellungen der Assembly Testpoint Style-Regel unterscheiden sich in der Topologie (von den Einstellungen im Diagramm). Hier wird die Option Rule Scope Helper angezeigt. In unserem Fall müssen Sie das Häkchen Thru-Hole Pads hinzufügen.

Es ist besser, die Online-Platzierungsprüfung für CT in Tools / Design Rule Check zu aktivieren, um die Lücken zwischen CT und EC-Fall sowie zwischen CT und Kante der Leiterplatte sofort zu kontrollieren. Sie müssen den Online-Modus speziell für die Assembly Testpoint Style-Regel aktivieren.

Um die CT in der Topologie zu steuern, können Sie bequem den Testpoint Manager (im Menü Extras) verwenden. Eine Beschreibung der Schnittstelle finden Sie

hier .

Matrix Testing Analytics

Zum Testen verwenden wir: einen Prüfstand (als Teil eines Falls), einen ST-Link / v2-Programmierer, einen externen Steuersystem-Simulator (Ausgangsschalter), ein externes Steuerspannungsmesser, ein Labornetzteil, einen Windows 10-PC und einen Klebeetikettendrucker.

Der Testalgorithmus umfasst:

- Systemdiagnose,

- die Simulator-Softwareversion erhalten,

- Stromversorgung und Überprüfung des Spannungs- und Stromverbrauchs,

- Firmware-Seriennummer,

- Sperren der Seriennummer,

- Bootloader-Firmware,

- Erhalten der Bootloader-Softwareversion,

- Firmware des Hauptprogramms,

- die Softwareversion des Hauptprogramms erhalten,

- Firmware-Basiskalibrierungstabellen,

- Ernährungscheck,

- Kontrolle der Steuerleitungen,

- Überprüfen des Ein- und Ausschaltens der Last,

- Kalibrierung der Vorspannung des Phasenschiebers,

- erneutes Blinken der Kalibrierungstabellen,

- Überprüfung der Kalibrierung des Moduls,

- Etikettendruck.

Fazit

Als Ergebnis des Testens von 1020 Blueberry-Boards haben wir 77 Boards abgelehnt. 44 von ihnen konnten ihre Funktionen aufgrund unzureichender Ernährung nicht erfüllen. Wie sich herausstellte, betrafen die Probleme die Stromversorgungen, die in zwei getrennten Losen geliefert wurden. Auf allen abgelehnten Boards wurden Quellen installiert, die ausschließlich einer der Parteien gehörten. Unsere Analyse ergab, dass alle diese Quellen während mindestens eines Tests inakzeptable Abweichungen von den vom Hersteller angegebenen Parametern zeigten.

Außerdem wurden 33 weitere Defekte identifiziert, einschließlich Kurzschlüssen, schlechtem Löten usw. Die Gesamtausstoßrate betrug 7,55%, was ein guter Indikator für die experimentelle Charge ist. Die Testergebnisse jedes Produkts werden in der Datenbank gespeichert, sodass Sie die Fehlerursachen ziemlich genau identifizieren können.

Die Vorbereitung des Chernik-Softwareprojekts für Matrixtests erfolgte in der letzten Phase der Topologieentwicklung, was zu Schwierigkeiten beim Hinzufügen von Kontaktflächen führte. Die Größe des Getriebes wurde unzureichend gewählt (1x1 mm), was zu Problemen beim Kontaktieren führte, wenn die Pog-Pins am Getriebe vorbei fielen. Der Anteil solcher Fehler ist vernachlässigbar.

In unserem nächsten Projekt mit Matrixtests haben wir CT im Voraus gelegt.

Jetzt können Sie eine Remote-Verbindung zur Standdatenbank herstellen. Die Stand-Firmware ist geschützt und unterstützt Profile mit unterschiedlichem Zugriff auf die Einstellungen, sodass der Stand in einer Remote-Auftragsfertigung platziert werden kann, die wir in Kaliningrad erfolgreich abgeschlossen haben. Aber mehr dazu in einem separaten Artikel. Thirdpin.io/testing

Thirdpin.io/testing