Einführung

Ich begrüße alle. Heute möchte ich meine Erfahrungen teilen und meiner Meinung nach auf den ersten Blick einen einfachen Standard für USB 2.0-Host-Controller klar erläutern.

Zunächst können Sie sich vorstellen, dass ein USB 2.0-Anschluss nur aus 4 Pins besteht, von denen zwei einfach Daten übertragen (z. B. ein COM-Anschluss), aber tatsächlich ist nicht alles so, und sogar das Gegenteil. Der USB-Controller erlaubt es uns grundsätzlich nicht, Daten wie über einen normalen COM-Port zu übertragen. EHCI ist ein ziemlich komplizierter Standard, der eine zuverlässige und schnelle Datenübertragung von der Software zum Gerät selbst und in die entgegengesetzte Richtung ermöglicht.

Sie können diesen Artikel nützlich finden, wenn Sie beispielsweise nicht über ausreichende Schreibfähigkeiten für Treiber und das Lesen von Dokumentation für eine Hardware verfügen. Ein einfaches Beispiel: Sie möchten Ihr Betriebssystem für einen Mini-PC schreiben, damit einige Windows- oder andere Linux-Distributionen kein Eisen herunterladen, und Sie nutzen die gesamte Leistung ausschließlich für Ihre eigenen Zwecke.

Was ist EHCI?

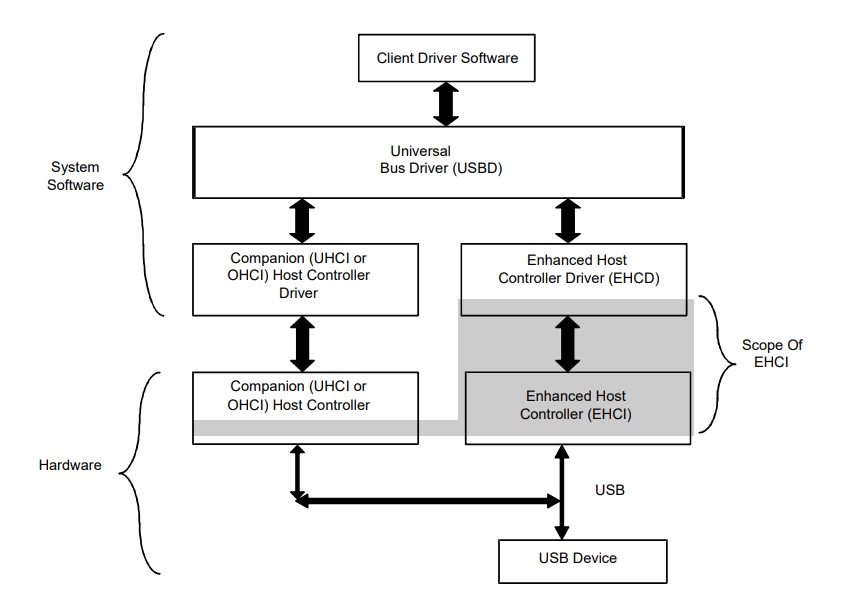

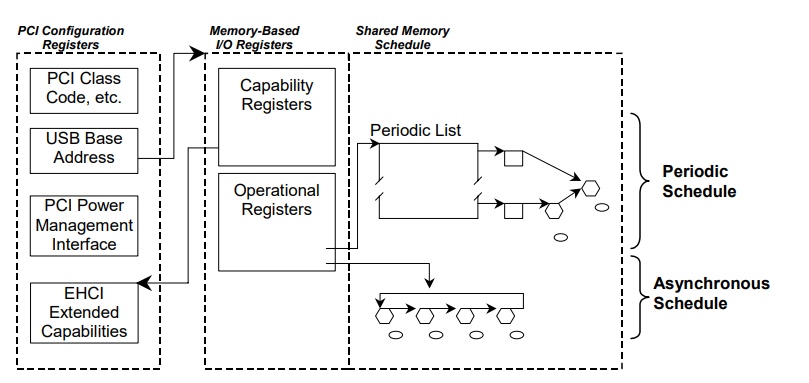

Nun, fangen wir an. EHCI - Enhanced Host Controller Interface (Enhanced Host Controller Interface) dient zur Übertragung von Daten und Steuerungsanforderungen an USB-Geräte und in die andere Richtung. In 99% der Fälle handelt es sich um eine Verbindung zwischen einer Software und einem physischen Gerät. EHCI arbeitet als PCI-Gerät und verwendet dementsprechend MMIO (Memory-Mapped-IO) zur Steuerung des Controllers (ja, ich weiß, dass einige PCI-Geräte Ports verwenden, aber hier habe ich alles verallgemeinert). Die Dokumentation von Intel beschreibt nur das Funktionsprinzip, und es gibt keine Hinweise auf alle Algorithmen, die zumindest in Pseudocode geschrieben sind. EHCI verfügt über zwei Arten von MMIO-Registern: Capability und Operational. Die ersteren dienen dazu, die Eigenschaften der Steuerung zu erhalten, während die letzteren dazu dienen, diese zu steuern. Eigentlich werde ich das Wesentliche der Verbindung zwischen Software und dem EHCI-Controller anhängen:

Jeder EHCI-Controller verfügt über mehrere Anschlüsse, von denen jeder an ein beliebiges USB-Gerät angeschlossen werden kann. Bitte beachten Sie auch, dass EHCI eine verbesserte Version von UHCI ist, die einige Jahre zuvor ebenfalls von Intel entwickelt wurde. Aus Gründen der Abwärtskompatibilität ist jeder UHCI / OHCI-Controller mit einer niedrigeren Version als EHCI ein Begleiter von EHCI. Sie haben beispielsweise eine USB-Tastatur (und die meisten Tastaturen des Jahres waren bisher genau so), die mit USB 1.1 funktioniert (beachten Sie, dass die maximale Geschwindigkeit von USB 1.1 12 Megabit pro Sekunde beträgt und FullSpeed USB 2.0 über Bandbreite verfügt bis zu 480 Mbit / s) und Sie haben einen Computer mit einem USB 2.0-Anschluss. Wenn Sie die Tastatur an den Computer anschließen, funktioniert der EHCI-Host-Controller in keiner Weise mit USB 1.1. Dieses Modell ist in der folgenden Abbildung dargestellt:

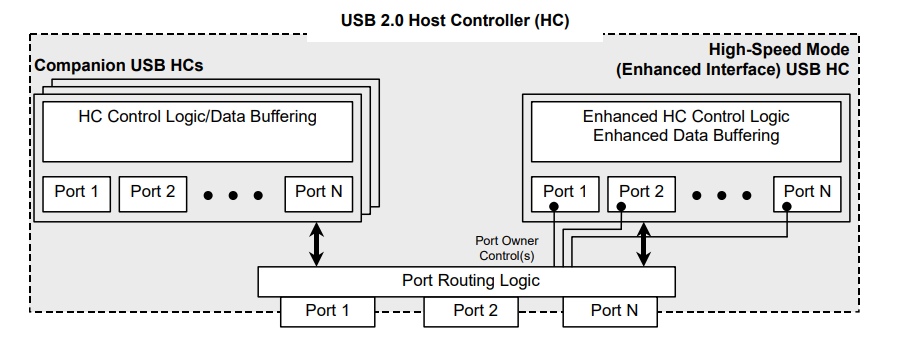

Außerdem möchte ich Sie für die Zukunft sofort warnen, dass Ihr Treiber aufgrund einer solch absurden Situation möglicherweise nicht richtig funktioniert: Sie haben UHCI initialisiert und dann EHCI, während Sie zwei identische Geräte hinzugefügt haben, das Port Owner Control-Bit auf das Portregister gesetzt und dann UHCI funktioniert nicht mehr, da EHCI den Port automatisch auf sich selbst zieht und der Port auf UHCI nicht mehr reagiert. Diese Situation muss überwacht werden.

Schauen wir uns auch ein Diagramm an, das die EHCI-Architektur selbst zeigt:

Rechts steht über die Warteschlange - etwas später darüber.

EHCI-Controller-Register

Zunächst möchte ich noch einmal klarstellen, dass Sie über diese Register Ihr Gerät steuern, daher sind sie sehr wichtig - und ohne sie ist eine EHCI-Programmierung nicht möglich.

Zuerst müssen Sie die MMIO-Adresse erhalten, die diesem Controller zugewiesen wurde. Bei Offset + 0x10 ist dies die Adresse unserer lang erwarteten Register. Es gibt eine Sache: Erstens gehen Capability-Register und erst danach - Operational, also bei Offset 0 (von der vorherigen Adresse, die wir bei Offset 0x10 relativ zum Beginn des MMIO unseres EHCI erhalten haben), gibt es ein Byte - die Länge der Capability-Register.

Fähigkeitsregister

Bei Offset 2 befindet sich das

HCIVERSION- Register - die Revisionsnummer dieses HC, die 2 Bytes benötigt und die BCD-Version der Revision enthält (welche BCD auf Wikipedia zu finden ist).

Bei Offset +4 befindet sich das

HCSPARAMS- Register, seine Größe beträgt 2 Wörter, es enthält die Strukturparameter des Geräts und seine Bits zeigen Folgendes:

- Bit 16 - Portanzeigen - Verfügbare LEDs für angeschlossene USB-Geräte.

- Bits 15:12 - Die Nummer des Companion-Controllers, der diesem Controller zugewiesen ist

- Bits 11: 8 - Die Anzahl der Ports auf dem Companion-Controller

- Bit 7 - Port-Routing-Regeln - zeigt, wie diese Ports Begleit-Ports zugeordnet werden

- Bit 4 - Port Power Control - zeigt an, ob die Stromversorgung für jeden Port eingeschaltet werden muss. 0 - Die Stromversorgung erfolgt automatisch

- Bits 3: 0 - Die Anzahl der Ports für diesen Controller.

- Bei Offset +8 liegt das HCCPARAMS-Register - es zeigt Kompatibilitätsparameter, seine Bits bedeuten Folgendes:

- Bit 2 - Verfügbarkeit der asynchronen Warteschlange,

- Bit 1 - Periodische (sequentielle) Verfügbarkeit der Warteschlange

- Bit 0 - 64 Bit Kompatibilität

Betriebsregister

Bei Offset 0 ist das

USBCMD- Register das Befehlsregister der Steuerung, seine Bits bedeuten Folgendes:

- Bits 23:16 - Interrupt Threshold Control - zeigt an, wie viele Micro-Frames für einen regulären Frame verwendet werden. Je größer, desto schneller, aber wenn mehr als 8, werden die Micro-Frames mit der gleichen Geschwindigkeit wie für 8 verarbeitet.

- Bit 6 - Interrupt nach jeder Transaktion in der asynchronen Warteschlange,

- Bit 5 - ist die verwendete asynchrone Warteschlange

- Bit 4 - Verwendung der sequentiellen Warteschlange,

- Bits 3: 2 - die Größe von FrameList'a (dazu später mehr). 0 bedeutet 1024 Elemente, 1 - 512, 2 - 256, 3 - reserviert

- Bit 1 - Zum Zurücksetzen des Host-Controllers setzen.

- Bit 0 - Ausführen / Stoppen

.

Als nächstes gibt es bei Offset +4 das

USBSTS- Register - den Status des Host-Controllers,

- Bit 15 gibt an, ob eine asynchrone Warteschlange verwendet wird.

- Bit 14 zeigt an, ob eine sequentielle Warteschlange verwendet wird.

- Bit 13 - zeigt an, dass eine leere asynchrone Warteschlange erkannt wurde.

- Bit 12 wird auf 1 gesetzt. Wenn während der Verarbeitung der Transaktion ein Fehler aufgetreten ist, stoppt der Host-Controller alle Warteschlangen.

- Bit 4 wird auf 1 gesetzt. Wenn ein schwerwiegender Fehler auftritt, stoppt der Host-Controller alle Warteschlangen.

- Bit 3 FrameList (Register) Rollover - wird auf 1 gesetzt, wenn der Host-Controller die gesamte FrameList verarbeitet hat.

- Bit 1 - USB-Fehlerunterbrechung - Generiere ich eine Fehlerunterbrechung?

- Bit 0 - USB-Interrupt - wird nach erfolgreicher Transaktionsverarbeitung gesetzt, wenn IOC in TD installiert wurde

Nicht müde? Sie können sich eine starke Möwe einschenken und die Leber bringen, wir stehen ganz am Anfang!

Bei Offset +8 gibt es ein

USBINTR- Register - das Interrupt-Aktivierungsregister

Um nicht lange zu schreiben und noch mehr, um nicht lange zu lesen, finden Sie die Werte der Bits dieses Registers in der Spezifikation. Ein Link dazu bleibt unten. Hier schreibe ich einfach 0, weil Ich habe absolut keine Lust, Handler, Map-Interrupts usw. zu schreiben, daher halte ich das für fast völlig sinnlos.

Bei Offset +12 (0x0C) befindet sich das

FRINDEX- Register, in dem die aktuelle Frame-Nummer einfach liegt, und ich möchte darauf hinweisen, dass die letzten 4 Bits die Micro-Frame-Nummer und in den oberen 28 Bits die Frame-Nummer anzeigen (der Wert ist auch nicht unbedingt kleiner als die FrameList-Größe Wenn Sie jedoch einen Index benötigen, ist es besser, ihn mit einer Maske von 0x3FF (oder 0x1FF usw.) zu verwenden.

Das

CTRLDSSEGMENT- Register hat den Offset + 0x10 und zeigt dem Host-Controller die höchstwertigen 32 Bits der Adresse des Rahmenblatts an.

Das

PERIODICLISTBASE- Register hat einen Versatz von + 0x14. Sie können die unteren 32 Bits des Rahmenblatts darin einfügen. Beachten Sie, dass die Adresse an der Größe der Speicherseite (4096) ausgerichtet sein sollte.

Das

ASYNCLISTADDR- Register hat einen Offset von + 0x18. Sie können die Adresse der asynchronen Warteschlange darin einfügen. Beachten Sie, dass sie an der Grenze von 32 Byte ausgerichtet sein muss, während sie sich in den ersten vier Gigabyte des physischen Speichers befinden muss.

Das

CONFIGFLAG- Register zeigt an, ob das Gerät konfiguriert ist. Sie müssen Bit 0 setzen, nachdem Sie das Geräte-Setup abgeschlossen haben. Es hat einen Offset von + 0x40.

Gehen wir weiter zu den Portregistern. Jeder Port hat ein eigenes Befehlsstatusregister, jedes

Portregister ist versetzt

+ 0x44 + (Portnummer - 1) * 4 , seine Bits bedeuten Folgendes:

- Bit 12 - Portstromversorgung, 1 - Stromversorgung, 0 - Nr.

- Bit 8 - Port Rest - wird gesetzt, um das Gerät zurückzusetzen.

- Bit 3 - Port Enable / Disable Change - wird gesetzt, wenn der Status der "Einbeziehung" des Ports geändert wird.

- Bit 2 - Port ein / aus.

- Bit 1 - Ändern Sie den Verbindungsstatus. Wird beispielsweise auf 1 gesetzt, wenn Sie ein USB-Gerät angeschlossen oder getrennt haben.

- Bit 0 - Verbindungsstatus, 1 - verbunden, 0 - Nr.

Kommen wir nun zum Saft selbst.

Datenübertragungs- und Abfragestrukturen

Das Organisieren einer Struktur zum Verarbeiten von Anforderungen umfasst Warteschlangen und Übertragungsdeskriptoren (TDs).

Im Moment werden wir nur 3 Strukturen betrachten.

Sequenzielle Liste

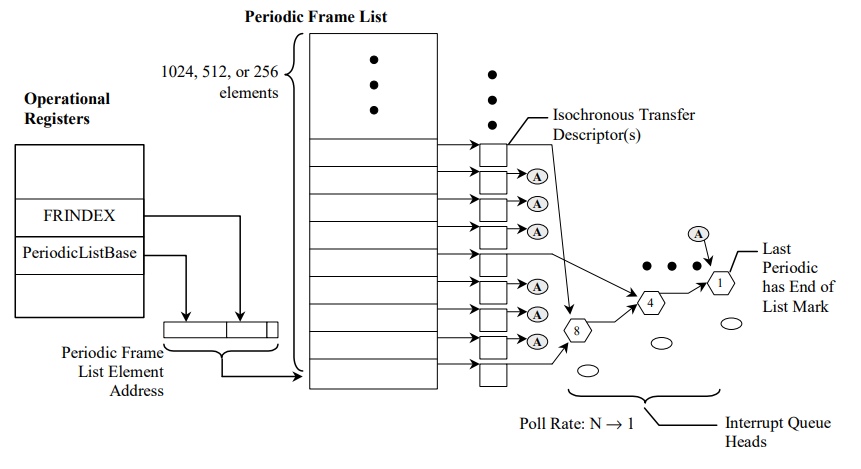

Die sequentielle Liste (periodisch, Pereodisch) ist wie folgt organisiert:

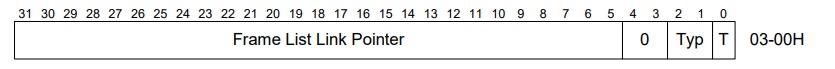

Wie Sie im Diagramm sehen können, beginnt die Verarbeitung mit dem Erhalten des gewünschten Rahmens aus dem Blattrahmen. Jedes seiner Elemente belegt 4 Bytes und hat die folgende Struktur:

Wie Sie in der Abbildung sehen können, ist die Übertragung von Warteschlangenadresse / Deskriptor an der Grenze von 32 Bytes ausgerichtet. Bit 0 bedeutet, dass der Host-Controller dieses Element nicht verarbeitet. Bits 3: 1 geben den Typ an, den der Host-Controller verarbeitet: 0 - isosynchrones TD (iTD), 1 - Runde, 2 und 3 in diesem Artikel werde ich nicht berücksichtigen.

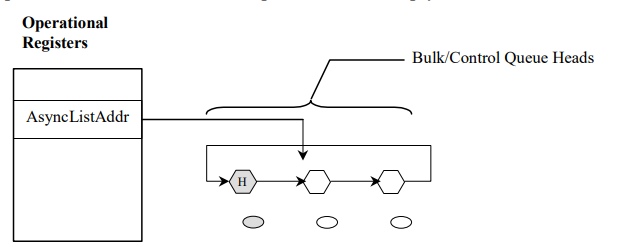

Asynchrone Warteschlange

Der Host-Controller verarbeitet diese Warteschlange nur, wenn der sequentielle Frame leer ist oder der Host-Controller die gesamte serielle Liste verarbeitet hat.

Eine asynchrone Warteschlange ist ein Zeiger auf eine Warteschlange, die andere Warteschlangen enthält, die verarbeitet werden müssen. Schema:

qTD (Queue Element Transfer Descriptor)

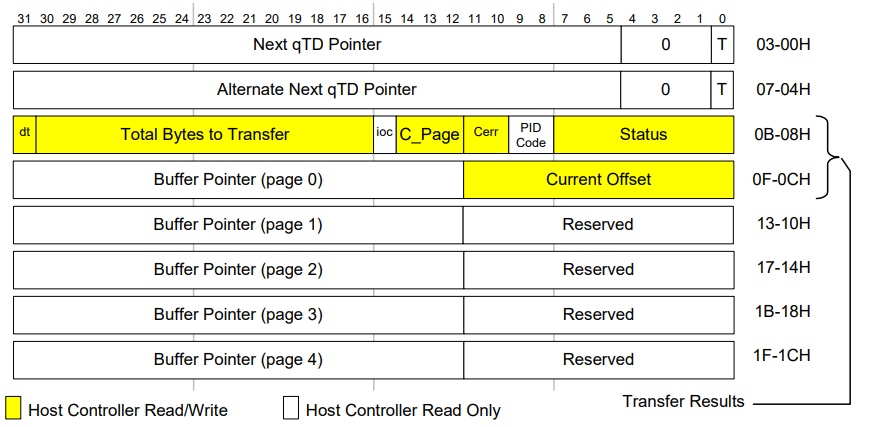

Dieser TD hat die folgende Struktur:

Nächster qTD-Zeiger

Nächster qTD-Zeiger - Ein Zeiger auf die Fortsetzung der Warteschlange zur Verarbeitung (für die horizontale Ausführung), Bit 0. Nächster qTD-Zeiger zeigt an, dass keine weitere Warteschlange vorhanden ist.

qTD-Token - TD-Token, zeigt Datenübertragungsparameter an:

- Bit 31 - Data Toggle (dazu später mehr)

- Bits 30:16 - Die zu übertragende Datenmenge verringert sich nach Abschluss der Transaktion um die übertragene Datenmenge.

- Bit 15 - IOC - Interrupt On Complete - Unterbrechung verursachen, nachdem die Deskriptorverarbeitung abgeschlossen ist.

- Die Bits 14:12 zeigen die Nummer des aktuellen Puffers, zu dem / von dem Daten ausgetauscht werden, dazu später mehr.

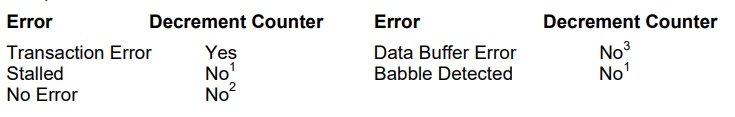

- Bits 11:10 - die Anzahl der zulässigen Fehler. Diese Tabelle zeigt, wann die Fehlerzahl abnimmt:

Fußnote 1 - Wenn Sie entweder Babble oder Stall erkennen, wird die Ausführung des Warteschlangenkopfs automatisch gestoppt. Fußnote 3 - Datenpufferfehler sind Probleme mit dem Host. Sie berücksichtigen keine Gerätewiederholungen. - 9: 8 - PID-Code - Token-Typ: 0 - Token zum Eingang (vom Host zum Gerät), 1 - Token zum Ausgang (vom Gerät zum Host), 2 - Token „SETUP“

- Die Bits 7: 0 zeigen den TD-Status an:

Bit 7 zeigt an, dass sich der TD in einem aktiven Zustand befindet (d. H. Der Host-Controller verarbeitet diesen TD).

Bit 6 - Angehalten - zeigt an, dass ein Fehler aufgetreten ist und die TD-Ausführung gestoppt wurde.

Bit 4 - Babble Detected - Die Datenmenge, die wir an das Gerät oder pro Umdrehung gesendet haben, ist geringer als die von uns übertragene, d. H. Das Gerät hat uns beispielsweise 100 Datenbytes gesendet, und wir lesen nur 50 Byte und dann weitere 50 Byte Das angehaltene Bit wird auch gesetzt, wenn dieses Bit auf 1 gesetzt ist.

Bit 3 - Transaktionsfehler - Während der Transaktion ist ein Fehler aufgetreten.

qTD Buffer Page Pointer List - einer von 5 Puffern. Es enthält einen Link zu dem Ort, an dem die Transaktion im Speicher durchgeführt werden soll (Daten an das Gerät senden / Daten vom Gerät empfangen). Alle Adressen in den Puffern mit Ausnahme der ersten sollten an der Größe der Seite ausgerichtet sein (4096 Byte).

Leiter der Leitung

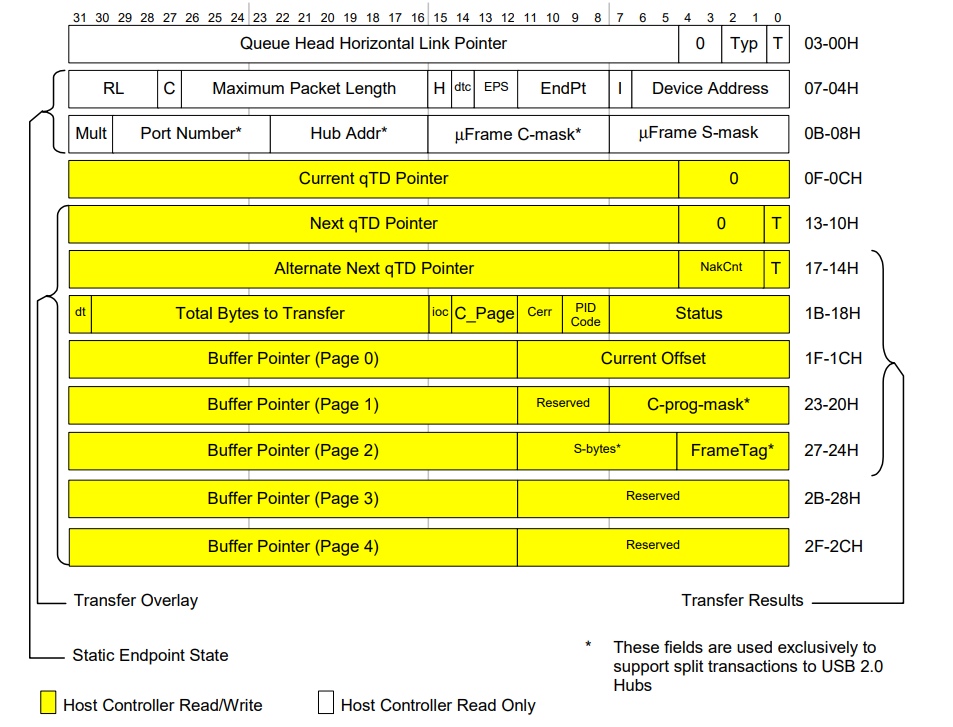

Der Warteschlangenkopf hat die folgende Struktur:

Horizontaler Verbindungszeiger

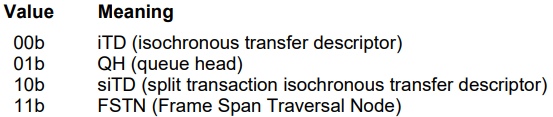

Horizontaler Verbindungszeiger für Warteschlangenkopf - Zeiger auf die nächste Warteschlange, Bits 2: 1 haben je nach Warteschlangentyp die folgenden Werte:

Endpunktfunktionen / -merkmale

Endpunktfunktionen / -merkmale - Warteschlangenmerkmale:

- Die Bits 26:16 enthalten die maximale Paketgröße für die Übertragung

- Bit 14: Data Toggle Control - Zeigt an, wo der Host-Controller den anfänglichen Data Toggle-Wert 0 annehmen soll. Ignoriert das DT-Bit in qTD und speichert das DT-Bit für den Warteschlangenkopf.

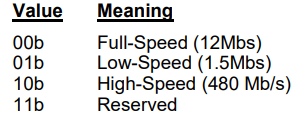

- Bit 13:12 - Übertragungsrateneigenschaften:

- Bits 11: 8 - Die Nummer des Endpunkts, an den die Anforderung gesendet wird

- Bits 6: 0 - Geräteadresse

Endpunktfunktionen: Queue Head DWord 2 - Fortsetzung des vorherigen Doppelworts:

- Bits 29:23 - Hub-Nummer

- Bits 22:16 - Hub-Adresse

Aktueller qTD-Link-Zeiger - Zeiger auf den aktuellen qTD.

Wir gehen zu den interessantesten über.

EHCI-Treiber

Beginnen wir mit den Fragen, die der EHCI erfüllen kann. Es gibt zwei Arten von Anforderungen: Steuerung - a la Befehl und Bulk - an Endpunkte, für den Datenaustausch. Beispielsweise verwendet die überwiegende Mehrheit der USB-Flash-Laufwerke (USB MassStorage) den Datenübertragungstyp Bulk / Bulk / Bulk. Maus und Tastatur verwenden auch Massenanforderungen für die Datenübertragung.

Initialisieren Sie EHCI und konfigurieren Sie asynchrone und sequentielle Warteschlangen:

Eigentlich der Code zum Zurücksetzen des Ports auf seinen ursprünglichen Zustand:

volatile u32 *reg = &hc->opRegs->ports[port];

Steueranforderung an das Gerät:

static void EhciDevControl(UsbDevice *dev, UsbTransfer *t) { EhciController *hc = (EhciController *)dev->hc; UsbDevReq *req = t->req;

Code für die Warteschlangenverarbeitung:

if (qh->token & TD_TOK_HALTED) { t->success = false; t->complete = true; } else if (qh->nextLink & PTR_TERMINATE) if (~qh->token & TD_TOK_ACTIVE) { if (qh->token & TD_TOK_DATABUFFER) kprintf(" Data Buffer Error\n"); if (qh->token & TD_TOK_BABBLE) kprintf(" Babble Detected\n"); if (qh->token & TD_TOK_XACT) kprintf(" Transaction Error\n"); if (qh->token & TD_TOK_MMF) kprintf(" Missed Micro-Frame\n"); t->success = true; t->complete = true; } if (t->complete) ....

Und jetzt die Endpunktanforderung (Massenanforderung)

static void EhciDevIntr(UsbDevice *dev, UsbTransfer *t) { EhciController *hc = (EhciController *)dev->hc;

Ich finde das Thema sehr interessant, im Internet auf Russisch gibt es fast keine Dokumente, Beschreibungen und Artikel zu diesem Thema, und wenn ja, ist es sehr verschwommen. Wenn das Thema der Arbeit mit Hardware- und Betriebssystementwicklung interessant ist, gibt es viel zu erzählen.

Docks:

Spezifikation