Anfang Oktober stellte Xilinx

den neuen Versal-Chip vor, der auf programmierbaren Gate-Arrays (

FPGAs )

basiert . Die Funktionslogik eines solchen Geräts kann jederzeit während des Gebrauchs geändert werden. Es wird erwartet, dass der Chip die Arbeit von KI-Systemen beschleunigt und in 5G-Netzwerken Anwendung findet. Die Veröffentlichung des Prozessors ist für Ende 2019 geplant.

Als nächstes sprechen wir über das Gerät und wie es Netzwerken der nächsten Generation helfen wird.

/ Flickr / mike mozart / cc

/ Flickr / mike mozart / cc5G-Netzwerkproblem

Die 5G-Technologie verwendet hohe Frequenzen - 28 GHz und höher -, sodass das Signal über große Entfernungen schlecht übertragen wird. Das Plus seiner Ausbreitung wird durch die Wände der Häuser stark behindert. In einer Stadt kann dies zu einer Verschlechterung der Verbindungsqualität führen.

Experten

sagen, dass dies ein Hindernis für die Arbeit einer großen Anzahl von IoT-Geräten sein wird, deren aktive Zunahme ab 2020

prognostiziert wird (genau dann, wenn vollwertige 5G-Netze bereitgestellt werden).

Angeschlossene Geräte wie Autos oder tragbare medizinische Geräte müssen in Echtzeit kommunizieren. Die Instabilität der Verbindung kann verhindern, dass sie die Situation um sie herum angemessen einschätzen oder wichtige Daten (z. B. über den Gesundheitszustand des Menschen) an die Server der bedienenden Organisation übertragen. Unternehmen planen, dieses Problem durch die Anordnung spezieller verteilter Antennensysteme zu lösen. Dabei treten jedoch Schwierigkeiten auf.

Zum Beispiel sind jetzt in New York mehr als tausend Basisstationen installiert. Um die gesamte Stadt mit einem 5G-Netz abzudecken

, muss eine weitere halbe Million installiert werden . Die Kosten des Projekts werden viel höher sein als bei den vorherigen "G-Standards".

Wie Versal hilft, diese Probleme zu lösen

Das Xilinx-Gerät hilft bei der Lösung der Probleme mit der Stabilität der Internetverbindung mithilfe von KI-Systemen, mit denen es „abgestimmt“ ist. Der Versal-Chip verarbeitet Algorithmen für maschinelles Lernen in 5G-Netzwerken, die die

Strahlungsmuster mobiler Antennen optimieren. Dadurch werden blinde Sektoren vermieden und der geeignete Datenübertragungsmodus ausgewählt.

KI-Systeme werden auch

Übergabealgorithmen verbessern, die für die Übertragung von Sitzungen von einer Station zu einer anderen verantwortlich sind. Außerdem reparieren und passen sich die Netzwerke selbst an und leiten Daten automatisch um, wenn ein Knoten ausfällt. So können sich 5G-Benutzer ohne Verbindungsfehler frei in einem Gebäude oder einer Stadt bewegen.

Xilinx hat bereits Kunden für AI-Chips für 5G. Versale Prozessoren werden bei den Olympischen Spielen 2020 für die Vernetzung verwendet.

Merkmale der Chiparchitektur

Xilinx führte das Versal-Konzept im Oktober ein. Die neue Mikroschaltung ist

heterogen , dh sie verwendet mehrere Recheneinheiten gleichzeitig. Diese Einheiten können Prozessoren, Coprozessoren, integrierte Schaltkreise ASIC und FPGA sein.

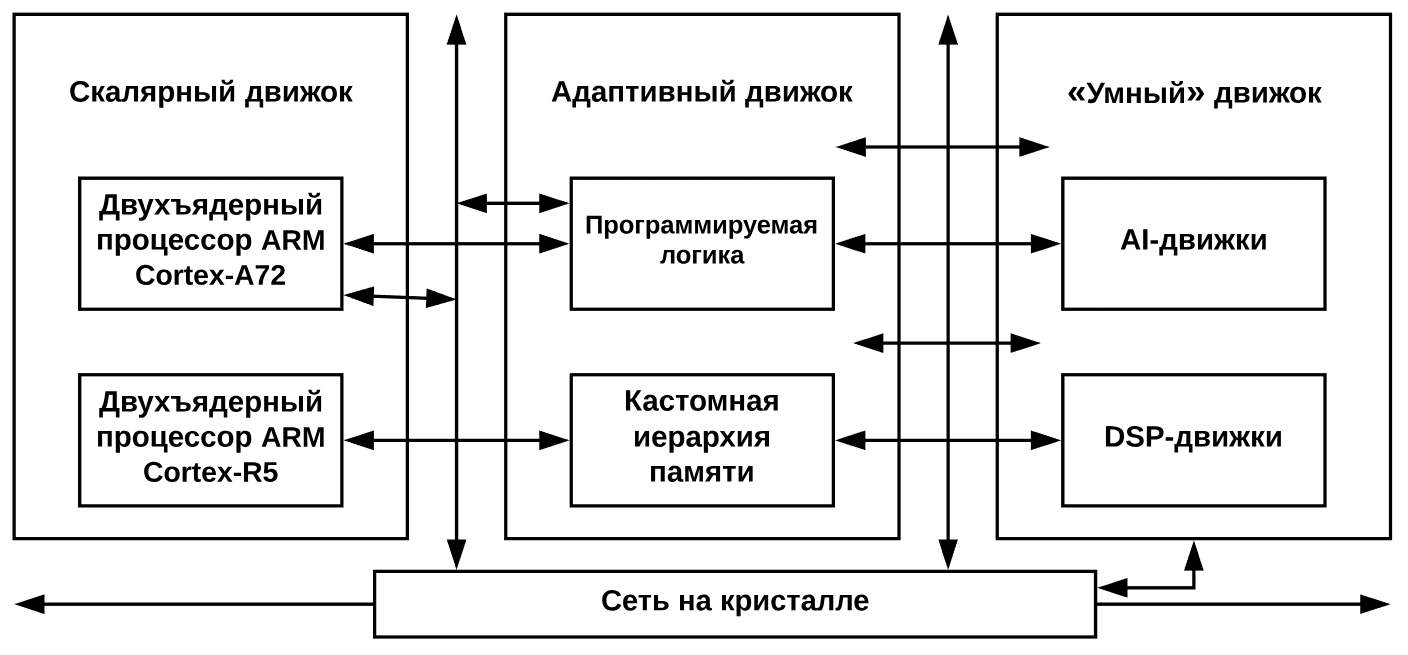

Der neue Xilinx-Chip basiert auf einer verbesserten Version von FPGA - der ACAP-Architektur (Adaptive Computer Accelerator Platform). Es besteht aus vier Grundkomponenten: einer

Skalarmaschine , einer adaptiven Engine,

Vektorbeschleunigern („intelligente“ Engine) und einem Netzwerk auf einem Chip (NoC - Network-on-Chip) zum Verbinden von Systemelementen.

Die Skalarmaschine wird durch Dual-Core-Prozessoren ARM Cortex-A72 und Cortex-R5 dargestellt. Die programmierbare Logik basiert auf konfigurierbaren

Logikelementen mit

Nachschlagetabellen ,

Triggern , Speicher und speziellen Blöcken zum Verknüpfen von Komponenten. Auf diese Weise können Sie eine

Speicherhierarchie erstellen, die für eine bestimmte Rechenaufgabe geschärft wurde.

Die „intelligente“ Engine basiert auf der

VLIW-Architektur , die für die parallele Ausführung mehrerer Operationen in einem Befehl benötigt wird. Das Prinzip der

SIMD- Berechnungen wird ebenfalls angewendet. Eine solche Struktur hilft, MO-Probleme zu lösen und Signale 5- bis 10-mal schneller zu verarbeiten als klassische Systeme. Für NoC beträgt die deklarierte Bandbreite 1 Tbit / s.

Das ACAP-Architekturdiagramm sieht folgendermaßen aus.

Die Versal-Chipfamilie wird bei TSMC unter Verwendung einer

7-nm- Prozesstechnologie hergestellt. Weitere architektonische Merkmale finden Sie in den offiziellen PDF-Dokumenten -

Übersicht über die ASAP-Architektur und

Überprüfung der Versal-Chips .

Das System ist in C, C ++ und Python programmiert. Laut den Entwicklern haben sie sich für diese PLs entschieden, da sie laut

TIOBE , C, C ++ und Python nach Java am beliebtesten sind.

Darüber hinaus ergänzen sich diese Sprachen. C und C ++ werden kompiliert, was bedeutet, dass der Code auf Bare-Metal (insbesondere auf FPGA) ausgeführt werden kann. Python ist besser als jeder andere für die Analyse von Daten und die Arbeit mit KI-Systemen. Weitere Gründe für die Wahl von Xilinx finden Sie in einer separaten Studie zum Thema (

PDF ).

Ähnliche Lösungen

FPGA-basierte Chips werden auch von anderen Unternehmen wie Intel entwickelt. Unter den neuesten Produkten des Unternehmens kann das

Arria-Hybridgerät unterschieden werden. Die Entwicklung ist eine Plattform aus zwei Chips: Xeon E5-2600 v4 und

Altera Arria 10 .

Laut Intel eignet sich das Gerät für Server, Rechenzentren und Cloud-Dienste, bei denen die Auslastung häufig krampfhaft zunimmt. Ein Prozessor auf dem FPGA hilft bei der parallelen Verarbeitung von Daten, wodurch die Gesamtsystemleistung erhöht wird. Fujitsu

plant beispielsweise, seine Primergy-Serverlinie bis Ende des Jahres mit diesem Chip auszustatten.

Andere Marktteilnehmer - AMD, ARM, Qualcomm, Samsung und andere - gründeten 2012 die gemeinnützige Organisation

HSA Foundation . Dort werden heterogene Berechnungen populär gemacht: Sie entwickeln Industriestandards, helfen Entwicklern beim Markteintritt und fördern Bildungsprogramme.

Xilinx geht

davon aus, dass mit der Entwicklung von KI-Systemen und der Verbreitung von 5G-Netzen die Nachfrage nach FPGA-Plattformen steigen wird. Victor Peng, CEO von Xilinx,

merkt an, dass das einzige Hindernis für die Massenproduktion von Chips die Konkurrenz durch CPU und GPU ist, die verhindert, dass FPGA-Lösungen den Markt „erobern“. Aber wahrscheinlich sollte ein Nachfragesprung (falls dies geschieht) nicht

vor 2020 erwartet werden.

PS Zusätzliche Materialien aus dem Unternehmensblog von VAS Experts:

PPS Ein paar neue Artikel aus unserem Blog über Habré: