In diesem Artikel möchte ich die Interrupt-Übermittlungsmechanismen von externen Geräten im x86-System betrachten und versuchen, die folgenden Fragen zu beantworten:

- Was ist PIC und wofür ist es?

- Was ist APIC und wofür ist es? Wofür sind LAPIC und I / O APIC?

- Was sind die Unterschiede zwischen APIC, xAPIC und x2APIC?

- Was ist MSI? Was sind die Unterschiede zwischen MSI und MSI-X?

- Wie hängen die $ PIR-, MPtable- und ACPI-Tabellen damit zusammen?

Wenn Sie eine Antwort auf eine dieser Fragen erhalten möchten oder sich nur mit der Entwicklung der Interrupt-Controller im x86-System vertraut machen möchten, sind Sie bei cat willkommen.

Einführung

Wir alle wissen, was Unterbrechung ist. Für diejenigen, die es nicht sind, zitieren Sie aus Wikipedia:

Unterbrechung (englische Unterbrechung) - Ein Signal von Software oder Hardware, das den Prozessor über das Auftreten eines Ereignisses informiert, das sofortige Aufmerksamkeit erfordert. Eine Unterbrechung benachrichtigt den Prozessor über das Auftreten eines Ereignisses mit hoher Priorität, das eine Unterbrechung des vom Prozessor ausgeführten aktuellen Codes erfordert. Der Prozessor reagiert, indem er seine aktuelle Aktivität unterbricht, seinen Status beibehält und eine Funktion ausführt, die als Interrupt-Handler (oder Interrupt-Handler) bezeichnet wird und auf das Ereignis reagiert und es bedient. Danach gibt er die Kontrolle an den unterbrochenen Code zurück.

Abhängig von der Quelle des Interrupt-Signals werden sie unterteilt in:

- asynchron oder extern (Hardware) - Ereignisse, die von externen Hardwaregeräten (z. B. Peripheriegeräten) stammen und zu einem beliebigen Zeitpunkt auftreten können: ein Signal von einem Timer, einer Netzwerkkarte oder einem Festplattenlaufwerk, Tastenanschläge, Mausbewegungen. Die Tatsache, dass ein solcher Interrupt im System auftritt, wird als Interrupt Request (IRQ) interpretiert. Geräte melden, dass sie die Aufmerksamkeit des Betriebssystems benötigen.

- synchrone oder interne Ereignisse im Prozessor selbst infolge der Verletzung bestimmter Bedingungen bei der Ausführung von Maschinencode: Division durch Null oder Stapelüberlauf, Zugriff auf ungültige Speicheradressen oder ungültigen Operationscode;

In diesem Artikel möchte ich externe IRQ-Interrupts diskutieren.

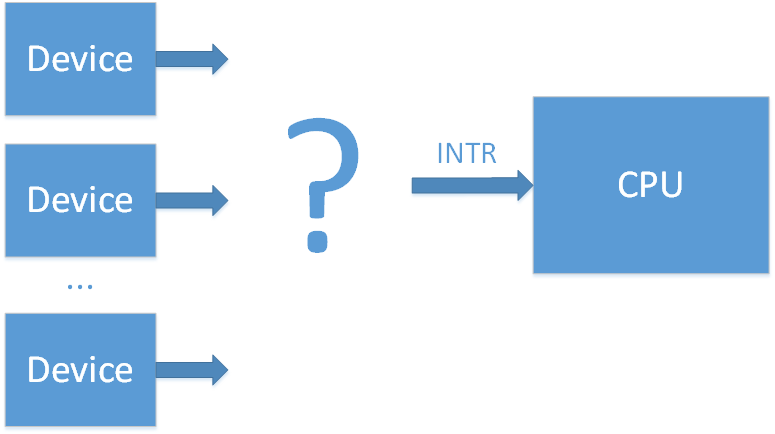

Warum werden sie gebraucht? Angenommen, wir möchten eine Aktion mit einem Eingabepaket für eine Netzwerkkarte ausführen, wenn diese eintrifft. Um die Netzwerkkarte nicht ständig zu fragen: "Haben Sie ein neues Paket?" Verschwenden Sie keine Prozessorressourcen, Sie können den IRQ-Interrupt verwenden. Die Geräte-Interrupt-Leitung ist mit der INTR-Leitung des Prozessors verbunden, und wenn ein Paket empfangen wird, "zieht" die Netzwerkkarte diese Leitung. Der Prozessor versteht, dass Informationen dafür vorhanden sind, und liest das Paket.

Aber was ist, wenn es viele Geräte gibt? Sie können nicht genug von allen externen Geräten der Prozessorbeine erhalten.

Um dieses Problem zu lösen, haben sie einen Chip entwickelt - einen Interrupt-Controller.

Pic

(

wiki /

osdev )

Der erste war ein

Intel 8259 PIC- Chip. 8 Eingangsleitungen (IRQ0-7) und ein Ausgang, der den Controller mit der INTR-Leitung des Prozessors verbindet. Wenn ein Interrupt von einem Gerät auftritt, zieht 8259 die INTR-Leitung, der Prozessor versteht, dass ein Gerät einen Interrupt signalisiert, und fragt den PIC ab, um zu verstehen, welcher IRQx-Zweig den Interrupt verursacht hat. Es gibt eine zusätzliche Verzögerung für diese Umfrage, aber die Anzahl der Interrupt-Leitungen erhöht sich auf 8.

8 Leitungen erwiesen sich jedoch schnell als klein, und um ihre Anzahl zu erhöhen, wurden 2 8259 in Kaskade geschaltete Controller (Master und Slave) (Dual PIC) verwendet.

Die IRQs 0 bis 7 werden vom ersten Intel 8259 PIC (Master) und die IRQs 8 bis 15 vom zweiten 8259 PIC (Slave) verarbeitet. Nur ein Master signalisiert das Auftreten eines Interrupts. Wenn auf den Leitungen 8-15 ein Interrupt auftritt, signalisiert der zweite PIC (Slave) dem Master über IRQ 2 einen Interrupt, und der Master signalisiert wiederum der CPU. Dieser kaskadierende Interrupt benötigt eine der 16 Leitungen, bietet jedoch am Ende 15 verfügbare Interrupts für Geräte.

Die Schaltung hat sich etabliert, und das ist es, was sie bedeuten, wenn sie jetzt über PIC (Programm Interrupt Controller) sprechen. Anschließend erhielten die 8259-Controller einige Verbesserungen und wurden als 8259A bekannt, und diese Schaltung wurde in den Chipsatz aufgenommen. Zu einer Zeit, als der Hauptbus zum Anschließen externer Geräte der ISA-Bus war, reichte ein solches System insgesamt aus. Es musste nur sichergestellt werden, dass verschiedene Geräte nicht mit derselben IRQ-Leitung verbunden waren, um Konflikte zu vermeiden, da ISA-Interrupts nicht gemeinsam genutzt werden.

Normalerweise war das Layout von Interrupts für Geräte mehr oder weniger Standard

Beispiel (

von hier genommen ):

IRQ 0 - Systemtimer

IRQ 1 - Tastaturcontroller

IRQ 2 - Kaskade (Interrupt vom Slave-Controller)

IRQ 3 - serielle Schnittstelle COM2

IRQ 4 - serielle Schnittstelle COM1

IRQ 5 - Parallelport 2 und 3 oder Soundkarte

IRQ 6 - Diskettenregler

IRQ 7 - Parallelport 1

IRQ 8 - RTC-Timer

IRQ 9 - ACPI

IRQ 10 - offen / SCSI / NIC

IRQ 11 - offen / SCSI / NIC

IRQ 12 - Mauscontroller

IRQ 13 - Mathe-Co-Prozessor

IRQ 14 - ATA-Kanal 1

IRQ 15 - ATA-Kanal 2

Die Konfiguration und Arbeit mit 8259 Mikroschaltungen erfolgt über E / A-Ports:

→ Die Dokumentation zum 8259A finden Sie

hier.Der ISA-Bus wurde durch den PCI-Bus ersetzt. Und die Anzahl der Geräte begann deutlich die Zahl 15 zu überschreiten. Im Gegensatz zum statischen ISA-Bus können die Geräte in diesem Fall dynamisch zum System hinzugefügt werden. Glücklicherweise können in diesem Bus Interrupts gemeinsam genutzt werden (dh mehrere Geräte können an dieselbe IRQ-Leitung angeschlossen werden). Um das Problem des Fehlens von IRQ-Leitungen zu lösen, beschlossen sie, Interrupts von allen PCI-Geräten in PIRQ-Leitungen zu gruppieren (Programmable Interrupt Request).

Angenommen, wir haben 4 Interrupt-Leitungen frei auf dem PIC-Controller und 20 PCI-Geräte. Wir kombinieren die Interrupts von 5 Geräten pro PIRQx-Leitung und verbinden die PIRQx-Leitungen mit dem Controller. Wenn auf der PIRQx-Leitung ein Interrupt auftritt, muss der Prozessor alle an diese Leitung angeschlossenen Geräte abfragen, um zu verstehen, von wem der Interrupt stammt. Dies löst jedoch im Allgemeinen das Problem. Ein Gerät, das PCI-Interrupt-Leitungen in einer PIRQ-Leitung bindet, wird häufig als PIR-Router bezeichnet.

Bei dieser Methode müssen Sie sicherstellen, dass die PIRQx-Leitungen nicht mit den IRQx-Leitungen verbunden sind, auf denen bereits ISA-Interrupts gestartet wurden (da dies zu Konflikten führt), und dass die PIRQx-Leitungen ausgeglichen sind (je mehr Geräte wir mit derselben PIRQ-Leitung verbunden haben, desto mehr Geräte benötigen Sie fragt den Prozessor ab, um zu verstehen, welches dieser Geräte den Interrupt verursacht hat).

Hinweis

Hinweis : Das PCI-Gerät -> PIR-Mapping wird im Bild abstrakt dargestellt, da es tatsächlich etwas komplizierter ist. In der Realität verfügt jedes PCI-Gerät über 4 Interrupt-Leitungen (INTA, INTB, INTC, INTD). Jedes PCI-Gerät kann bis zu 8 Funktionen haben, und jetzt hat jede Funktion einen INTx-Interrupt. Welche INTx jede Funktion des Geräts abruft, hängt von der Konfiguration des Chipsatzes ab.

Funktionen sind im Wesentlichen separate logische Blöcke. Beispielsweise kann in einem PCI-Gerät eine Smbus-Controller-Funktion, eine SATA-Controller-Funktion oder eine LPC-Bridge-Funktion vorhanden sein. Auf der Betriebssystemseite ist jede Funktion ein separates Gerät mit einem eigenen Konfigurationsbereich für die PCI-Konfiguration.

Das Betriebssystem übertrug Informationen über Routing-Interrupts im BIOS des PIC-Controllers unter Verwendung der Tabelle $ PIR und durch Ausfüllen der Register 3Ch (INT_LN Interrupt Line (R / W)) und 3Dh (INT_PN Interrupt Pin (RO)) des PCI-Konfigurationsraums für jede Funktion. Die Spezifikation für die $ PIR-Tabelle befand sich zuvor

auf der Microsoft-Website , ist jetzt jedoch nicht mehr vorhanden. Der Inhalt der Zeilen der $ PIR-Tabelle kann der

PCI-BIOS-Spezifikation [4.2.2. Holen Sie sich PCI Interrupt Routing Options] oder lesen Sie

hierApic

(

Wiki ,

Osdev )

Die vorherige Methode funktionierte, bis Multiprozessorsysteme erschienen. Tatsache ist, dass PIC in seinem Gerät Interrupts nur an einen Hauptprozessor übertragen kann. Ich möchte jedoch, dass die Belastung der Prozessoren durch die Interrupt-Behandlung ausgeglichen wird. Die Lösung für dieses Problem war die neue Schnittstelle APIC (Advanced PIC).

Für jeden Prozessor wird ein spezieller LAPIC-Controller (Local APIC) und ein

E / A-APIC- Controller hinzugefügt, um Interrupts von Geräten weiterzuleiten. Alle diese Steuerungen sind in einem gemeinsamen Bus namens APIC zusammengefasst (neue Systeme werden jetzt über einen Standardsystembus verbunden).

Wenn ein Interrupt von einem Gerät am E / A-APIC-Pin ankommt, leitet die Steuerung den Interrupt an den LAPIC eines der Prozessoren weiter. Durch das Vorhandensein von E / A-APIC können Sie die Verteilung von Interrupts von externen Geräten zwischen Prozessoren ausgleichen.

Der erste APIC-Chip war

82489DX , ein separater Chip, der LAPIC und I / O-APIC kombiniert. Um ein System von 2 Prozessoren zu erstellen, wurden 3 solcher Mikroschaltungen benötigt. 2 würde als LAPIC und eine als I / O APIC fungieren. Später wurde die LAPIC-Funktionalität direkt in die Prozessoren integriert, und die E / A-APIC-Funktionalität wurde in den 82093AA-Chip integriert.

Der E / A-APIC

82093AA enthielt 24 Eingangspins, und die APIC-Architektur konnte bis zu 16 CPUs unterstützen. Um die Kompatibilität mit älteren Systemen aufrechtzuerhalten, wurden alten ISA-Interrupts 0 bis 15 Interrupts zugewiesen. In der IRQ-Zeile 16-23 wurden Unterbrechungen durch PCI-Geräte angezeigt. Jetzt war es möglich, nicht an Interrupt-Konflikte von ISA- und PCI-Geräten zu denken. Dank der erhöhten Anzahl freier Interrupt-Leitungen ist es auch möglich geworden, die Anzahl der PIRQx-Leitungen zu erhöhen.

Die E / A-APIC- und LAPIC-Programmierung erfolgt über MMIO. LAPIC-Register befinden sich normalerweise bei 0xFEE00000, E / A-APIC-Register bei 0xFE00000. Grundsätzlich können jedoch alle diese Adressen neu konfiguriert werden.

Wie bei PIC wurden zunächst einzelne Chips später Teil des Chipsatzes.

Anschließend wurde die APIC-Architektur modernisiert und die neue Version hieß xAPIC (x - erweitert). Abwärtskompatibilität mit der vorherigen Version beibehalten. Die Anzahl der möglichen CPUs im System wurde auf 256 erhöht.

Die nächste Runde der Architekturentwicklung hieß

x2APIC . Die Anzahl der möglichen CPUs im System wurde auf 2 ^ 32 erhöht. Die Controller können im xAPIC-Kompatibilitätsmodus oder im neuen x2APIC-Modus arbeiten, in dem die LAPIC-Programmierung nicht über MMIO, sondern über MSR-Register (was viel schneller ist) erfolgt. Nach

diesem Link zu urteilen

, ist IOMMU-Unterstützung erforderlich, damit dieser Modus funktioniert.

Es ist zu beachten, dass das System möglicherweise über mehrere E / A-APIC-Controller verfügt. Zum Beispiel eine für 24 Unterbrechungen in der Südbrücke, die andere für 32 im Norden. Im Zusammenhang mit E / A werden APIC-Interrupts häufig als GSI (Global System Interrupt) bezeichnet. In einem solchen System wird also GSI 0-55 sein.

Gibt es eine eingebaute LAPIC in der CPU und welche Architektur von den Bit-Flags in der CPUID verstanden werden kann.

Damit das System LAPIC und E / A-APIC erkennen kann, muss das BIOS dem System Informationen über diese entweder über die MPtable (die alte Methode) oder über die ACPI-Tabelle (in diesem Fall MADT) bereitstellen. Zusätzlich zu allgemeinen Informationen sollten sowohl die MPtable als auch die ACPI (diesmal in der DSDT-Tabelle) Informationen zum Interrupt-Routing enthalten, dh Informationen darüber, welches Gerät auf welcher Interrupt-Leitung sitzt (analog zur $ PIR-Tabelle).

Die MPTable-Tabelle finden Sie in der offiziellen

Spezifikation . Früher befand sich die Spezifikation auf der Intel-Website, jetzt ist sie nur noch im Archiv zu finden. Die ACPI-Spezifikation befindet sich jetzt auf der UEFI-Website (aktuelle Version

6.2 ). Es ist zu beachten, dass Sie mit ACPI das Interrupt-Routing für Systeme ohne APIC festlegen können (anstatt die Tabelle $ PIR zu verwenden).

Msi

(

Wiki )

Die vorherige Version mit APIC ist gut, aber nicht ohne Mängel. Alle diese Geräteunterbrechungsleitungen komplizieren die Schaltung und erhöhen die Fehlerwahrscheinlichkeit. Der PCI-Bus wurde durch PCI Express ersetzt, bei dem die Interrupt-Leitungen einfach entfernt werden sollten. Um die Kompatibilität zu gewährleisten, werden Interrupt-Signale (INTx #) von bestimmten Nachrichtentypen emuliert. In diesem Schema fiel die logische Hinzufügung von Interrupt-Leitungen, die früher durch physische Verbindung von Drähten erfolgte, auf die Schultern von PCI-Brücken. Die Unterstützung älterer INTx-Interrupts ist jedoch nur Unterstützung für die Abwärtskompatibilität mit dem PCI-Bus. Tatsächlich hat PCI Express eine neue Methode zur Zustellung von Interrupt-Nachrichten vorgeschlagen - MSI (Message Signaled Interrupts). Bei dieser Methode schreibt das Gerät einfach in den MMIO-Bereich, der dem Prozessor-LAPIC zugewiesen ist, um eine Unterbrechung zu signalisieren.

Früher wurden einem PCI-Gerät (dh allen seinen Funktionen) nur 4 Interrupts zugewiesen, jetzt können jetzt bis zu 32 Interrupts adressiert werden.

Bei MSI gibt es keine gemeinsame Nutzung für die Leitungen, jeder Interrupt entspricht seinem Gerät.

MSI-Interrupts lösen auch ein anderes Problem. Angenommen, ein Gerät führt eine Speicherschreibtransaktion durch und möchte seinen Abschluss über einen Interrupt melden. Eine Schreibtransaktion auf dem Bus kann jedoch während des Übertragungsprozesses (von dem das Gerät überhaupt nichts weiß) verzögert sein, und das Interrupt-Signal wird vor dem Prozessor eintreffen. Somit liest die CPU immer noch ungültige Daten. Wenn MSI verwendet wird, werden Informationen über MSI sowie Daten übertragen und können einfach nicht früher eingehen.

Es sollte beachtet werden, dass MSI-Interrupts ohne LAPIC nicht funktionieren können, aber die Verwendung von MSI kann uns durch I / O-APIC ersetzen (Design-Vereinfachung).

Anschließend erhielt diese Methode die MSI-X-Erweiterung. Jetzt kann jedes Gerät bis zu 2048 Interrupts haben. Und es wurde möglich, jedem Interrupt einzeln anzugeben, auf welchem Prozessor er ausgeführt werden soll. Dies kann für stark belastete Geräte wie Netzwerkkarten sehr nützlich sein.

Für die MSI-Unterstützung sind keine zusätzlichen BIOS-Tabellen erforderlich. Das Gerät muss jedoch die MSI-Unterstützung in einer der Funktionen in seiner PCI-Konfiguration melden, und der Gerätetreiber muss die Arbeit mit MSI unterstützen.

Fazit

In diesem Artikel haben wir die Entwicklung von Interrupt-Controllern untersucht und allgemeine theoretische Informationen zur Übermittlung von Interrupts von externen Geräten in einem x86-System erhalten.

Im

nächsten Teil werden wir uns ansehen, wie jeder der beschriebenen Controller in der Praxis unter Linux verwendet wird.

Referenzen: