Im

vorherigen Teil haben wir die Entwicklung der Interrupt-Übermittlung von Geräten in x86-Systemen (PIC → APIC → MSI), eine allgemeine Theorie und alle erforderlichen Begriffe untersucht.

In diesem praktischen Teil werden wir uns ansehen, wie Sie auf ältere Linux-Interrupt-Übermittlungsmethoden zurückgreifen können, indem Sie die Kernel-Boot-Optionen berücksichtigen:

Wir werden uns auch die Reihenfolge ansehen, in der das Betriebssystem die Interrupt-Routing-Tabellen (ACPI / MPtable / $ PIR) betrachtet und welche Auswirkungen dies auf das Hinzufügen von Startoptionen hat:

- pci = noacpi

- acpi = noirq

- acpi = aus

Vielleicht haben Sie Kombinationen all dieser Optionen ausprobiert, als ein Gerät aufgrund eines Interrupt-Problems nicht funktionierte. Lassen Sie uns sehen, was genau sie tun und wie sie die Ausgabe von / proc / interrupts ändern.

Download ohne zusätzliche Optionen

Wir werden Unterbrechungen in diesem Artikel auf einem benutzerdefinierten Board mit Intel Haswell i7 mit dem lynxPoint-LP-Chipsatz beobachten, auf dem

Coreboot ausgeführt wird.

Wir werden Informationen über Interrupts über den Befehl ausgeben

cat /proc/interrupts

Ausgabe beim Booten ohne zusätzliche Optionen:

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 0 1 0 1 IO-APIC-edge i8042 8: 0 0 0 1 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-fasteoi acpi 12: 0 0 0 1 IO-APIC-edge 23: 16 247 7 10 IO-APIC-fasteoi ehci_hcd:usb1 56: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 57: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 58: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 59: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 60: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 61: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 62: 3118 1984 972 3454 PCI-MSI-edge ahci 63: 1 0 0 0 PCI-MSI-edge eth59 64: 2095 57 4 832 PCI-MSI-edge eth59-rx-0 65: 6 18 1 1309 PCI-MSI-edge eth59-rx-1 66: 13 512 2 1 PCI-MSI-edge eth59-rx-2 67: 10 61 232 2 PCI-MSI-edge eth59-rx-3 68: 169 0 0 0 PCI-MSI-edge eth59-tx-0 69: 14 14 4 205 PCI-MSI-edge eth59-tx-1 70: 11 491 3 0 PCI-MSI-edge eth59-tx-2 71: 20 19 134 50 PCI-MSI-edge eth59-tx-3 72: 0 0 0 0 PCI-MSI-edge eth58 73: 2 1 0 152 PCI-MSI-edge eth58-rx-0 74: 3 150 2 0 PCI-MSI-edge eth58-rx-1 75: 2 34 117 2 PCI-MSI-edge eth58-rx-2 76: 153 0 2 0 PCI-MSI-edge eth58-rx-3 77: 4 0 2 149 PCI-MSI-edge eth58-tx-0 78: 4 149 2 0 PCI-MSI-edge eth58-tx-1 79: 4 0 117 34 PCI-MSI-edge eth58-tx-2 80: 153 0 2 0 PCI-MSI-edge eth58-tx-3 81: 66 106 2 101 PCI-MSI-edge snd_hda_intel 82: 928 5657 262 224 PCI-MSI-edge i915 83: 545 56 32 15 PCI-MSI-edge snd_hda_intel NMI: 0 0 0 0 Non-maskable interrupts LOC: 4193 3644 3326 3499 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 290 233 590 111 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1339 2163 2404 1946 Rescheduling interrupts CAL: 607 537 475 559 Function call interrupts TLB: 163 202 164 251 TLB shootdowns TRM: 48 48 48 48 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 3 3 3 3 Machine check polls ERR: 0 MIS: 0

Die Datei / proc / interrupts enthält eine Tabelle zur Anzahl der Interrupts auf jedem Prozessor in der folgenden Form:

- Erste Spalte: Interruptnummer

- CPUx-Lautsprecher: Interrupt-Zähler auf jedem Prozessor

- Nächste Spalte: Art des Interrupts:

- IO-APIC-Flanke - Flankenunterbrechung zum E / A-APIC-Controller

- IO-APIC-fasteoi - Pegelinterrupt pro E / A-APIC-Controller

- PCI-MSI-Edge - MSI-Interrupt

- XT-PIC-XT-PIC - Interrupt am PIC-Controller (siehe später)

- Letzte Spalte: Gerät, das diesem Interrupt zugeordnet ist

So wie es in einem modernen System sein sollte, werden sie für Geräte und Treiber verwendet, die MSI / MSI-X-Interrupts unterstützen. Die verbleibenden Interrupts werden über den E / A-APIC geleitet.

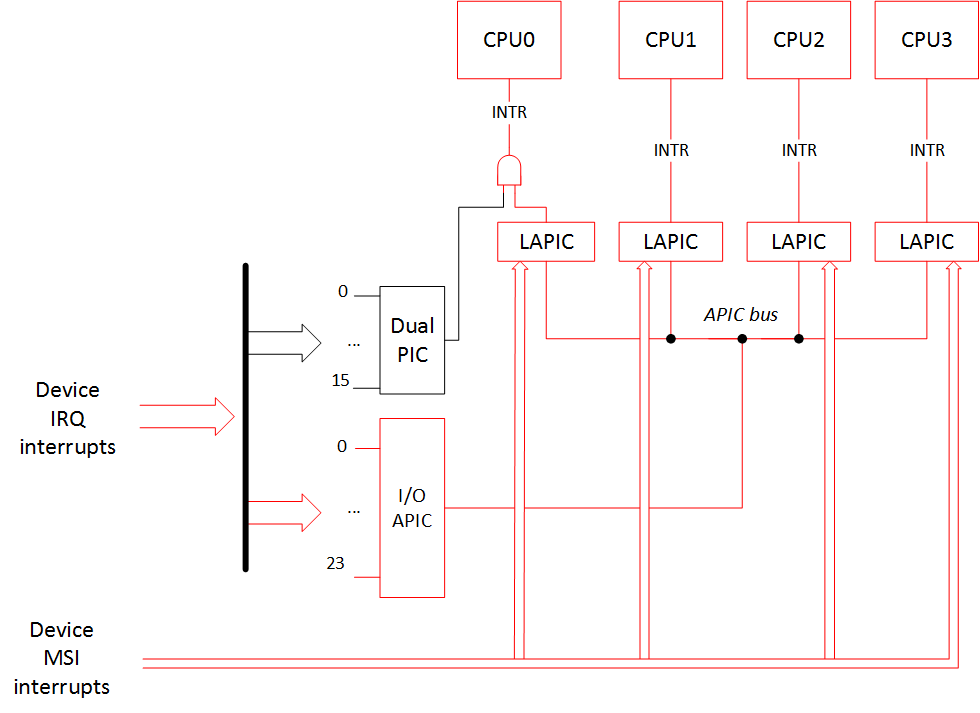

So kann ein vereinfachtes Interrupt-Routing-Schema gezeichnet werden (aktive Pfade rot markiert, nicht verwendete Pfade schwarz markiert).

Die Unterstützung für ein MSI / MSI-X-Gerät muss in seinem PCI-Konfigurationsbereich als entsprechende Funktion angegeben werden.

Zur Bestätigung geben wir ein kleines Fragment der lspci-Ausgabe für Geräte an, für die angegeben wird, dass sie MSI / MSI-X verwenden. In unserem Fall handelt es sich um einen SATA-Controller (Interrupt ahci), 2 Ethernet-Controller (Interrupts eth58 * und eth59 *), einen Grafik-Controller (i915) und 2 HD-Audio-Controller (snd_hda_intel).

lspci -v

00:02.0 VGA compatible controller: Intel Corporation Haswell-ULT Integrated Graphics Controller (rev 09) (prog-if 00 [VGA controller]) ... Capabilities: [90] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [d0] Power Management version 2 Capabilities: [a4] PCI Advanced Features Kernel driver in use: i915 00:03.0 Audio device: Intel Corporation Haswell-ULT HD Audio Controller (rev 09 ... Capabilities: [60] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [70] Express Root Complex Integrated Endpoint, MSI 00 Kernel driver in use: snd_hda_intel 00:1b.0 Audio device: Intel Corporation 8 Series HD Audio Controller (rev 04) ... Capabilities: [60] MSI: Enable+ Count=1/1 Maskable- 64bit+ Capabilities: [70] Express Root Complex Integrated Endpoint, MSI 00 Capabilities: [100] Virtual Channel Kernel driver in use: snd_hda_intel 00:1f.2 SATA controller: Intel Corporation 8 Series SATA Controller 1 [AHCI mode] (rev 04) (prog-if 01 [AHCI 1.0]) ... Capabilities: [80] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [70] Power Management version 3 Capabilities: [a8] SATA HBA v1.0 Kernel driver in use: ahci 05:00.0 Ethernet controller: Intel Corporation I350 Gigabit Network Connection (rev 01) ... Capabilities: [50] MSI: Enable- Count=1/1 Maskable+ 64bit+ Capabilities: [70] MSI-X: Enable+ Count=10 Masked- Capabilities: [a0] Express Endpoint, MSI 00 Kernel driver in use: igb 05:00.1 Ethernet controller: Intel Corporation I350 Gigabit Network Connection (rev 01) ... Capabilities: [50] MSI: Enable- Count=1/1 Maskable+ 64bit+ Capabilities: [70] MSI-X: Enable+ Count=10 Masked- Capabilities: [a0] Express Endpoint, MSI 00 Kernel driver in use: igb

Wie wir sehen können, haben diese Geräte die Zeile "MSI: Enable +" oder "MSI-X: Enable +".

Beginnen wir damit, das System zu verschlechtern. Booten Sie zunächst mit der Option pci = nomsi.

pci = nomsi

Mit dieser Option werden MSI-Interrupts je nach verwendetem Interrupt-Controller zu IO-APIC / XT-PIC.

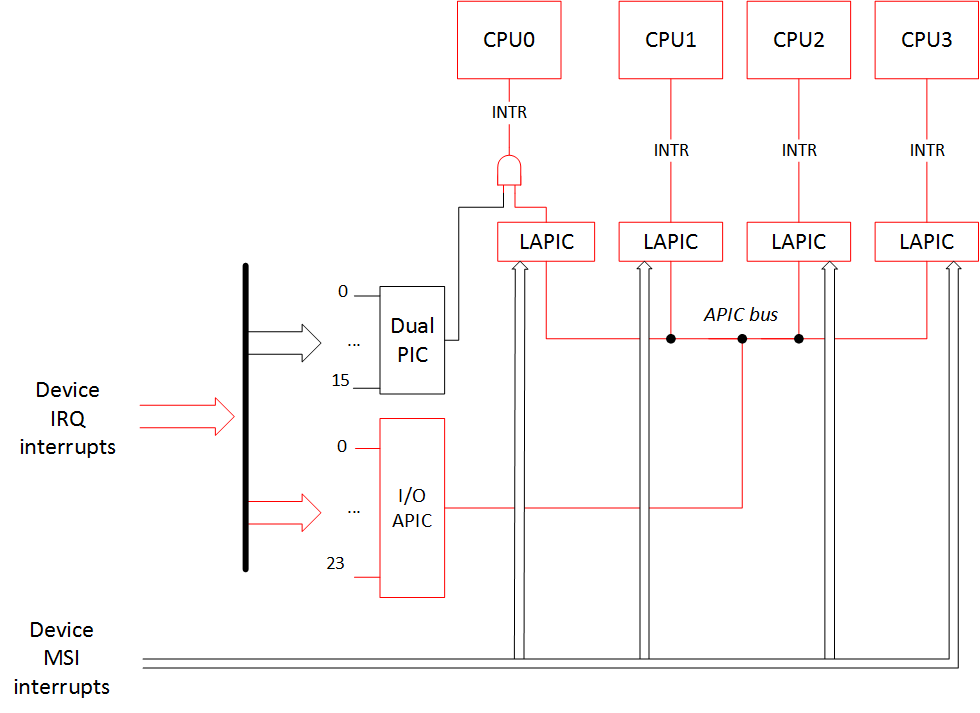

In diesem Fall haben wir immer noch den Prioritäts-APIC-Interrupt-Controller. Das Bild sieht also folgendermaßen aus:

Die Ausgabe von / proc / interrupts:

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 0 1 0 1 IO-APIC-edge i8042 8: 0 0 1 0 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-fasteoi acpi 12: 0 0 0 1 IO-APIC-edge 16: 1314 5625 342 555 IO-APIC-fasteoi i915, snd_hda_intel, eth59 17: 5 0 1 34 IO-APIC-fasteoi eth58 21: 2882 2558 963 2088 IO-APIC-fasteoi ahci 22: 26 81 2 170 IO-APIC-fasteoi snd_hda_intel 23: 23 369 8 8 IO-APIC-fasteoi ehci_hcd:usb1 NMI: 0 0 0 0 Non-maskable interrupts LOC: 3011 3331 2435 2617 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 197 228 544 85 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1708 2349 1821 1569 Rescheduling interrupts CAL: 520 554 509 555 Function call interrupts TLB: 187 181 205 179 TLB shootdowns TRM: 102 102 102 102 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Es wird erwartet, dass alle MSI / MSI-X-Interrupts verschwinden. Stattdessen verwenden Geräte jetzt IO-APIC-fasteoi-Interrupts.

Beachten Sie, dass eth58 und eth59 vor der Aufnahme dieser Option jeweils 9 Interrupts hatten! Und jetzt nur noch einer nach dem anderen. Wie wir uns erinnern, ist ohne MSI eine PCI-Funktion nur ein Interrupt verfügbar!

Einige Informationen von dmesg zur Initialisierung von Ethernet-Controllern:

- Download ohne pci = nomsi Option:

igb: Intel(R) Gigabit Ethernet Network Driver - version 5.0.5-k igb: Copyright (c) 2007-2013 Intel Corporation. acpi:acpi_pci_irq_enable: igb 0000:05:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16 igb 0000:05:00.0: irq 63 for MSI/MSI-X igb 0000:05:00.0: irq 64 for MSI/MSI-X igb 0000:05:00.0: irq 65 for MSI/MSI-X igb 0000:05:00.0: irq 66 for MSI/MSI-X igb 0000:05:00.0: irq 67 for MSI/MSI-X igb 0000:05:00.0: irq 68 for MSI/MSI-X igb 0000:05:00.0: irq 69 for MSI/MSI-X igb 0000:05:00.0: irq 70 for MSI/MSI-X igb 0000:05:00.0: irq 71 for MSI/MSI-X igb 0000:05:00.0: irq 63 for MSI/MSI-X igb 0000:05:00.0: irq 64 for MSI/MSI-X igb 0000:05:00.0: irq 65 for MSI/MSI-X igb 0000:05:00.0: irq 66 for MSI/MSI-X igb 0000:05:00.0: irq 67 for MSI/MSI-X igb 0000:05:00.0: irq 68 for MSI/MSI-X igb 0000:05:00.0: irq 69 for MSI/MSI-X igb 0000:05:00.0: irq 70 for MSI/MSI-X igb 0000:05:00.0: irq 71 for MSI/MSI-X igb 0000:05:00.0: added PHC on eth0 igb 0000:05:00.0: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.0: eth0: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2a igb 0000:05:00.0: eth0: PBA No: 106300-000 igb 0000:05:00.0: Using MSI-X interrupts. 4 rx queue(s), 4 tx queue(s) acpi:acpi_pci_irq_enable: igb 0000:05:00.1: PCI INT B -> GSI 17 (level, low) -> IRQ 17 igb 0000:05:00.1: irq 72 for MSI/MSI-X igb 0000:05:00.1: irq 73 for MSI/MSI-X igb 0000:05:00.1: irq 74 for MSI/MSI-X igb 0000:05:00.1: irq 75 for MSI/MSI-X igb 0000:05:00.1: irq 76 for MSI/MSI-X igb 0000:05:00.1: irq 77 for MSI/MSI-X igb 0000:05:00.1: irq 78 for MSI/MSI-X igb 0000:05:00.1: irq 79 for MSI/MSI-X igb 0000:05:00.1: irq 80 for MSI/MSI-X igb 0000:05:00.1: irq 72 for MSI/MSI-X igb 0000:05:00.1: irq 73 for MSI/MSI-X igb 0000:05:00.1: irq 74 for MSI/MSI-X igb 0000:05:00.1: irq 75 for MSI/MSI-X igb 0000:05:00.1: irq 76 for MSI/MSI-X igb 0000:05:00.1: irq 77 for MSI/MSI-X igb 0000:05:00.1: irq 78 for MSI/MSI-X igb 0000:05:00.1: irq 79 for MSI/MSI-X igb 0000:05:00.1: irq 80 for MSI/MSI-X igb 0000:05:00.1: added PHC on eth1 igb 0000:05:00.1: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.1: eth1: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2b igb 0000:05:00.1: eth1: PBA No: 106300-000 igb 0000:05:00.1: Using MSI-X interrupts. 4 rx queue(s), 4 tx queue(s)

- Booten Sie mit der Option pci = nomsi

igb: Intel(R) Gigabit Ethernet Network Driver - version 5.0.5-k igb: Copyright (c) 2007-2013 Intel Corporation. acpi:acpi_pci_irq_enable: igb 0000:05:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16 igb 0000:05:00.0: added PHC on eth0 igb 0000:05:00.0: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.0: eth0: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2a igb 0000:05:00.0: eth0: PBA No: 106300-000 igb 0000:05:00.0: Using legacy interrupts. 1 rx queue(s), 1 tx queue(s) acpi:acpi_pci_irq_enable: igb 0000:05:00.1: PCI INT B -> GSI 17 (level, low) -> IRQ 17 igb 0000:05:00.1: added PHC on eth1 igb 0000:05:00.1: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.1: eth1: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2b igb 0000:05:00.1: eth1: PBA No: 106300-000 igb 0000:05:00.1: Using legacy interrupts. 1 rx queue(s), 1 tx queue(s)

Aufgrund der Verringerung der Anzahl der Interrupts pro Gerät kann die Aktivierung dieser Option die

Treiberleistung erheblich einschränken (dies berücksichtigt nicht die Tatsache, dass Interrupts über MSI laut Intel zur

Reduzierung der Interrupt-Latenz durch die Verwendung von Message Signaled Interrupts dreimal schneller sind als über IO -APIC und 5 mal schneller als durch PIC).

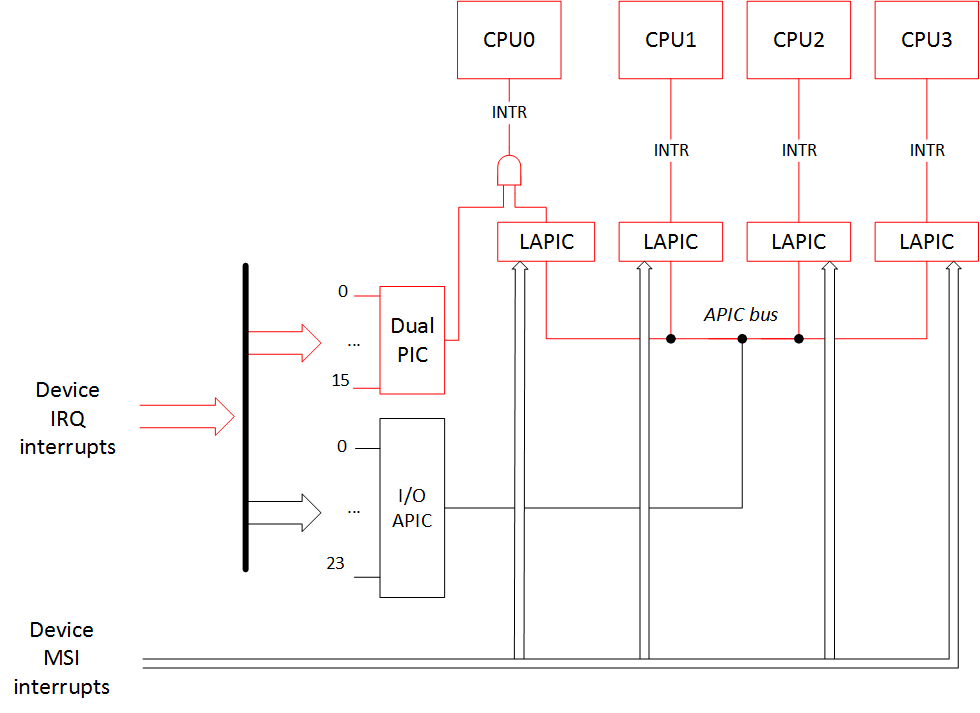

noapic

Diese Option deaktiviert den E / A-APIC. MSI-Interrupts können weiterhin an alle CPUs gesendet werden, Interrupts von Geräten können jedoch nur an CPU0 gesendet werden, da der PIC nur an CPU0 angeschlossen ist. Aber LAPIC funktioniert und andere CPUs können Interrupts verarbeiten.

CPU0 CPU1 CPU2 CPU3 0: 5 0 0 0 XT-PIC-XT-PIC timer 1: 2 0 0 0 XT-PIC-XT-PIC i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 8: 1 0 0 0 XT-PIC-XT-PIC rtc0 9: 0 0 0 0 XT-PIC-XT-PIC acpi 12: 172 0 0 0 XT-PIC-XT-PIC ehci_hcd:usb1 56: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 57: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 58: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 59: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 60: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 61: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 62: 2833 2989 1021 811 PCI-MSI-edge ahci 63: 0 1 0 0 PCI-MSI-edge eth59 64: 301 52 9 3 PCI-MSI-edge eth59-rx-0 65: 12 24 3 178 PCI-MSI-edge eth59-rx-1 66: 14 85 6 2 PCI-MSI-edge eth59-rx-2 67: 17 24 307 1 PCI-MSI-edge eth59-rx-3 68: 70 18 8 10 PCI-MSI-edge eth59-tx-0 69: 7 0 0 23 PCI-MSI-edge eth59-tx-1 70: 15 227 2 2 PCI-MSI-edge eth59-tx-2 71: 18 6 27 2 PCI-MSI-edge eth59-tx-3 72: 0 0 0 0 PCI-MSI-edge eth58 73: 1 0 0 27 PCI-MSI-edge eth58-rx-0 74: 1 22 0 5 PCI-MSI-edge eth58-rx-1 75: 1 0 22 5 PCI-MSI-edge eth58-rx-2 76: 23 0 0 5 PCI-MSI-edge eth58-rx-3 77: 1 0 0 27 PCI-MSI-edge eth58-tx-0 78: 1 22 0 5 PCI-MSI-edge eth58-tx-1 79: 1 0 22 5 PCI-MSI-edge eth58-tx-2 80: 23 0 0 5 PCI-MSI-edge eth58-tx-3 81: 187 17 70 7 PCI-MSI-edge snd_hda_intel 82: 698 1647 247 129 PCI-MSI-edge i915 83: 438 135 16 59 PCI-MSI-edge snd_hda_intel NMI: 0 0 0 0 Non-maskable interrupts LOC: 1975 2499 2245 1474 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 132 67 429 91 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1697 2178 1903 1541 Rescheduling interrupts CAL: 561 496 534 567 Function call interrupts TLB: 229 254 170 137 TLB shootdowns TRM: 78 78 78 78 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Wie Sie sehen können, werden alle IO-APIC- * Interrupts zu XT-PIC-XT-PIC, und diese Interrupts werden nur auf CPU0 geroutet. MSI-Interrupts bleiben unverändert und gehen an alle CPU0-3.

nolapic

Deaktiviert LAPIC. MSI-Interrupts können ohne LAPIC nicht funktionieren, E / A-APIC kann ohne LAPIC nicht funktionieren. Daher werden alle Interrupts von Geräten an den PIC gesendet und funktionieren nur mit CPU0. Und ohne LAPIC funktionieren andere CPUs nicht einmal im System.

Die Ausgabe von / proc / interrupts:

CPU0 0: 6416 XT-PIC-XT-PIC timer 1: 2 XT-PIC-XT-PIC i8042 2: 0 XT-PIC-XT-PIC cascade 3: 5067 XT-PIC-XT-PIC aerdrv, aerdrv, PCIe PME, PCIe PME, i915, snd_hda_intel, eth59 4: 32 XT-PIC-XT-PIC aerdrv, aerdrv, PCIe PME, PCIe PME, eth58 5: 0 XT-PIC-XT-PIC aerdrv, PCIe PME 6: 0 XT-PIC-XT-PIC aerdrv, PCIe PME 8: 1 XT-PIC-XT-PIC rtc0 9: 0 XT-PIC-XT-PIC acpi 11: 274 XT-PIC-XT-PIC snd_hda_intel 12: 202 XT-PIC-XT-PIC ehci_hcd:usb1 15: 7903 XT-PIC-XT-PIC ahci NMI: 0 Non-maskable interrupts LOC: 0 Local timer interrupts SPU: 0 Spurious interrupts PMI: 0 Performance monitoring interrupts IWI: 0 IRQ work interrupts RTR: 0 APIC ICR read retries RES: 0 Rescheduling interrupts CAL: 0 Function call interrupts TLB: 0 TLB shootdowns TRM: 0 Thermal event interrupts THR: 0 Threshold APIC interrupts MCE: 0 Machine check exceptions MCP: 1 Machine check polls ERR: 0 MIS: 0

Kombinationen:

Tatsächlich nur eine für die neue Version: "noapic pci = nomsi". Alle Interrupts von Geräten können nur über den PIC an CPU0 gesendet werden. Aber LAPIC funktioniert und andere CPUs können Interrupts verarbeiten.

Zum einen, weil man mit "nolapic" nichts kombinieren kann, weil Diese Option macht E / A-APIC und MSI nicht verfügbar. Wenn Sie also einmal die Startoptionen "noapic nolapic" (oder die häufigste Option "acpi = off noapic nolapic") vorgeschrieben haben, haben Sie anscheinend zusätzliche Buchstaben eingegeben.

Was passiert also mit den Optionen "noapic pci = nomsi":

Die Ausgabe von / proc / interrupts:

CPU0 CPU1 CPU2 CPU3 0: 5 0 0 0 XT-PIC-XT-PIC timer 1: 2 0 0 0 XT-PIC-XT-PIC i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 3: 5072 0 0 0 XT-PIC-XT-PIC i915, snd_hda_intel, eth59 4: 32 0 0 0 XT-PIC-XT-PIC eth58 8: 1 0 0 0 XT-PIC-XT-PIC rtc0 9: 0 0 0 0 XT-PIC-XT-PIC acpi 11: 281 0 0 0 XT-PIC-XT-PIC snd_hda_intel 12: 200 0 0 0 XT-PIC-XT-PIC ehci_hcd:usb1 15: 7930 0 0 0 XT-PIC-XT-PIC ahci NMI: 0 0 0 0 Non-maskable interrupts LOC: 2595 2387 2129 1697 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 159 90 482 135 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1568 1666 1810 1833 Rescheduling interrupts CAL: 431 556 549 558 Function call interrupts TLB: 124 184 156 274 TLB shootdowns TRM: 116 116 116 116 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Unterbrechen Sie die Routing-Tabellen und -Optionen "acpi = noirq", "pci = noacpi", "acpi = off".

Wie empfängt das Betriebssystem Interrupt-Routing-Informationen von Geräten? Das BIOS bereitet Informationen für das Betriebssystem in Form von:

- ACPI-Tabellen (_PIC / _PRT-Methoden)

- _MP_ Tabellen (MPtable)

- $ PIR-Tabellen

- Registriert den 0x3C / 0x3D PCI-Gerätekonfigurationsbereich

Es ist zu beachten, dass das BIOS keine zusätzlichen Maßnahmen ergreifen muss, um Unterbrechungen des MSI anzuzeigen. Alle oben genannten Informationen werden nur für APIC / PIC-Interrupt-Leitungen benötigt.

Die Tabellen in der obigen Liste sind in der Reihenfolge ihrer Priorität angegeben. Betrachten wir es genauer.

Angenommen, das BIOS hat alle diese Daten bereitgestellt und wir starten ohne zusätzliche Optionen:

- Das Betriebssystem findet ACPI-Tabellen

- Das Betriebssystem führt die ACPI-Methode "_PIC" aus und übergibt ihr das Argument, dass sie im APIC-Modus geladen werden muss. Hier speichert der Methodencode normalerweise den ausgewählten Modus in einer Variablen (z. B. PICM = 1).

- Um Daten über Interrupts zu erhalten, ruft das Betriebssystem die ACPI-Methode "_PRT" auf. Es überprüft die PICM-Variable intern und gibt das Routing für den APIC-Fall zurück

Falls wir mit der

Noapic- Option

booten :

- Das Betriebssystem findet ACPI-Tabellen

- Das Betriebssystem führt die ACPI-Methode "_PIC" aus und übergibt ihm das Argument, dass im PIC-Modus gestartet werden muss. Hier speichert der Methodencode normalerweise den ausgewählten Modus in einer Variablen (z. B. PICM = 0).

- Um Daten über Interrupts zu erhalten, ruft das Betriebssystem die ACPI-Methode "_PRT" auf. Es überprüft die PICM-Variable intern und gibt das Routing für den PIC-Fall zurück

Wenn die ACPI-Tabelle fehlt oder die Interrupt-Routing-Funktionalität über ACPI mithilfe der

Optionen acpi = noirq oder

pci = noacpi deaktiviert ist (oder die ACPI mithilfe von

acpi = off vollständig

deaktiviert ist ), sucht das Betriebssystem nach der Tabelle MPtable (_MP_) für Routing-Interrupts:

- Das Betriebssystem findet keine ACPI-Tabellen

- Betriebssystem findet MPtable (_MP_)

Wenn die ACPI-Tabelle fehlt oder die Interrupt-Routing-Funktionalität über ACPI mit den

Optionen acpi = noirq oder

pci = noacpi deaktiviert ist (oder die ACPI mit

acpi = off vollständig

deaktiviert ist ) und wenn die Tabelle MPtable (_MP_) fehlt (oder die Option

noapic oder

nolapic boot

übergeben wurde ):

- Das Betriebssystem findet / sieht keine ACPI-Tabelle

- Betriebssystem findet / sieht Tabelle MPtable (_MP_) nicht

- Das Betriebssystem findet die Tabelle $ PIR

Wenn keine $ PIR-Tabelle vorhanden ist oder diese nicht vollständig ist, überprüft das Betriebssystem, um Unterbrechungen zu erraten, die Werte der Register 0x3C / 0x3D im Konfigurationsbereich von PCI-Geräten.

Wir fassen alle oben genannten Punkte mit folgendem Bild zusammen:

Es ist zu beachten, dass nicht jedes BIOS alle drei Tabellen (ACPI / MPtable / $ PIR) bereitstellt. Wenn Sie also die Option an den Loader übergeben haben, die Verwendung von ACPI oder ACPI und MPtable für das Weiterleiten von Interrupts abzulehnen, ist dies weit davon entfernt, dass Ihr System gestartet wird.

Hinweis 1 : Wenn wir versuchen, im APIC-Modus mit der Option acpi = noirq und ohne MPtable zu booten, ist das Bild der Unterbrechungen das gleiche wie beim normalen Booten mit der einzigen noapic-Option. Das Betriebssystem selbst wechselt in den PIC-Interrupt-Modus.

Wenn wir versuchen, überhaupt ohne ACPI-Tabellen (acpi = off) und ohne MPtable zu booten, sieht das Bild folgendermaßen aus:

CPU0 0: 6 XT-PIC-XT-PIC timer 1: 2 XT-PIC-XT-PIC i8042 2: 0 XT-PIC-XT-PIC cascade 8: 0 XT-PIC-XT-PIC rtc0 12: 373 XT-PIC-XT-PIC ehci_hcd:usb1 16: 0 PCI-MSI-edge PCIe PME 17: 0 PCI-MSI-edge PCIe PME 18: 0 PCI-MSI-edge PCIe PME 19: 0 PCI-MSI-edge PCIe PME 20: 0 PCI-MSI-edge PCIe PME 21: 0 PCI-MSI-edge PCIe PME 22: 8728 PCI-MSI-edge ahci 23: 1 PCI-MSI-edge eth59 24: 1301 PCI-MSI-edge eth59-rx-0 25: 113 PCI-MSI-edge eth59-tx-0 26: 0 PCI-MSI-edge eth58 27: 45 PCI-MSI-edge eth58-rx-0 28: 45 PCI-MSI-edge eth58-tx-0 29: 1280 PCI-MSI-edge snd_hda_intel NMI: 2 Non-maskable interrupts LOC: 24076 Local timer interrupts SPU: 0 Spurious interrupts PMI: 2 Performance monitoring interrupts IWI: 2856 IRQ work interrupts RTR: 0 APIC ICR read retries RES: 0 Rescheduling interrupts CAL: 0 Function call interrupts TLB: 0 TLB shootdowns TRM: 34 Thermal event interrupts THR: 0 Threshold APIC interrupts MCE: 0 Machine check exceptions MCP: 2 Machine check polls ERR: 0 MIS: 0

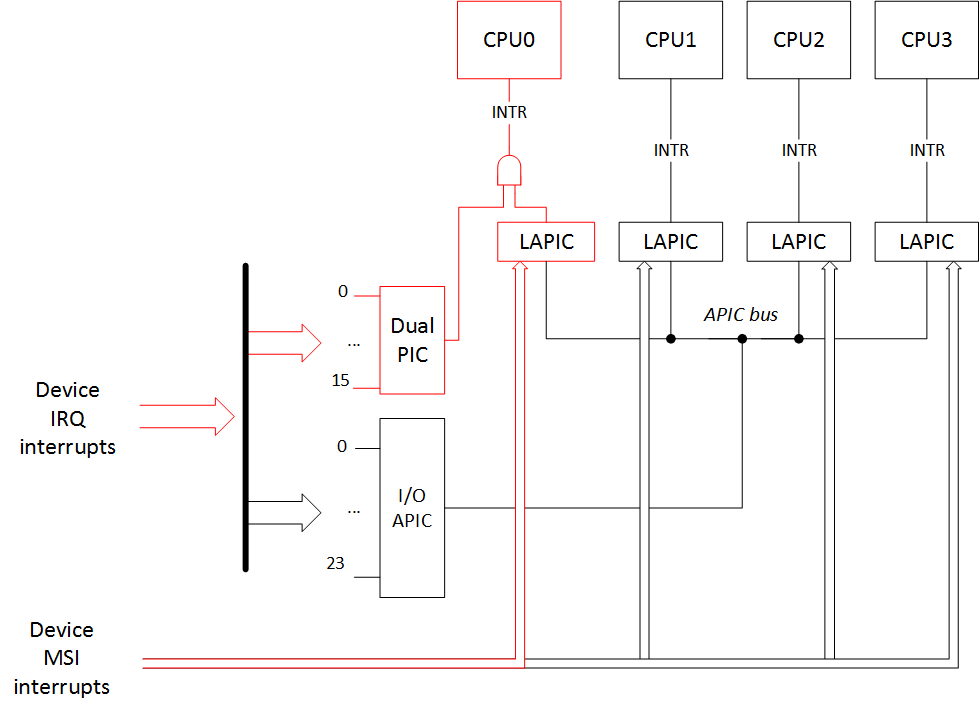

Dies liegt daran, dass das Betriebssystem ohne die ACPI der MADT-Tabelle (

Multiple APIC Description Table ) und die erforderlichen Informationen aus MPtable die APIC-Kennungen (APIC IDs) für andere Prozessoren nicht kennt und nicht mit ihnen arbeiten kann, die LAPIC des Hauptprozessors jedoch funktioniert. da wir dies nicht verboten haben und MSI-Interrupts dazu kommen können. Das heißt, es wird so sein:

Hinweis 2

Hinweis 2 : Im Allgemeinen entspricht das Interrupt-Routing bei Verwendung von ACPI bei APIC dem Interrupt-Routing über MPtable. Das ACPI-Interrupt-Routing bei PIC entspricht dem Interrupt-Routing über $ PIR. Die Schlussfolgerungen von / proc / interrupts sollten sich also nicht unterscheiden. Während des Forschungsprozesses bemerkte ich jedoch eine Seltsamkeit. Beim Routing über MPtable enthält der Ausgang aus irgendeinem Grund einen kaskadierenden Interrupt „XT-PIC-XT-PIC-Kaskade“.

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 2 0 0 0 IO-APIC-edge i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 8: 0 1 0 0 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-edge acpi ...

Es ist etwas seltsam, dass dies passiert, aber die

Kerneldokumentation scheint zu sagen, dass dies normal ist.

Fazit:

Abschließend bezeichnen wir noch einmal die analysierten Optionen.

Auswahloptionen für Interrupt-Controller:

- pci = nomsi - MSI-Interrupts werden abhängig vom verwendeten Interrupt-Controller zu IO-APIC / XT-PIC

- noapic - Deaktiviert den E / A-APIC. MSI-Interrupts können weiterhin an alle CPUs gesendet werden, andere Interrupts von Geräten können nur an PIC gesendet werden und funktionieren nur mit CPU0. Aber LAPIC funktioniert und andere CPUs können Interrupts verarbeiten

- noapic pci = nomsi - Alle Interrupts von Geräten können nur an den PIC gesendet werden und funktionieren nur mit CPU0. Aber LAPIC funktioniert und andere CPUs können Interrupts verarbeiten

- nolapic - Deaktiviert LAPIC. MSI-Interrupts können ohne LAPIC nicht funktionieren, E / A-APIC kann ohne LAPIC nicht funktionieren. Alle Interrupts von Geräten werden an den PIC gesendet und funktionieren nur mit CPU0. Und ohne LAPIC funktioniert der Rest der CPU nicht.

Optionen zur Auswahl der Prioritätstabelle für das Interrupt-Routing:

- Keine Optionen - Routing durch APIC mithilfe von ACPI-Tabellen

- noapic - Routing durch PIC unter Verwendung von ACPI-Tabellen

- acpi = noirq ( pci = noacpi / acpi = off ) - Routing durch APIC unter Verwendung der MPtable

- acpi = noirq ( pci = noacpi / acpi = off ) noapic ( nolapic ) - Routing über PIC unter Verwendung der $ PIR-Tabelle

Im nächsten Teil werden wir sehen, wie Coreboot den Chipsatz für das Routing von Interrupts konfiguriert.