In den Kommentaren zu meinem

Artikel über die Steuerung von RGB-LEDs mit dem UDB-Mikrocontroller-Block PSoC von Cypress wurde vorgeschlagen, am Anfang des Artikels kurz zu erläutern, was UDB ist. Wie ich bereits in diesem Artikel erwähnt habe, kann ich nicht kurz über UDB schreiben, aber Sie können einfach die Unternehmensdokumentation darauf übertragen, um den inländischen Leser mit einem so leistungsstarken Tool zur Implementierung von Firmware-Funktionen vertraut zu machen.

Aber zuerst schauen wir uns an, worum es bei PSoC geht. PSoC ist eine Cypress-Familie von Chipsätzen zur Implementierung von On-Chip-Systemen. Verschiedene Familien haben einen unterschiedlichen Prozessorkern (für PSoC 3 ist es MCS-51, für PSoC 4 ist es Cortex M0, für PSoC 5LP ist es Cortex M3 und für PSoC 6 sind es zwei gleichzeitig: Cortex M0 + und Cortex M4) und einen Satz programmierbarer Logik. Darüber hinaus ist diese Logik nicht rein digital, es gibt dort analoge Dinge. Neben verschiedenen ADCs gibt es auch analoge Schalter. Sie können die Beine sogar programmgesteuert über analoge Schaltkreise verbinden. Der Widerstand des Schaltkreises wird jedoch in Kilogramm gemessen. In PSoC gibt es Operationsverstärker, die programmgesteuert geschaltet werden können. Dies bedeutet, dass Sie verschiedene analoge Blöcke darauf aufbauen können.

PSoCs können übrigens mit jeder Spannung von 2,7 bis 5,5 Volt betrieben werden. Das heißt, Sie müssen weder mit Batteriestrom noch mit USB-Strom an Stabilisatoren denken.

Aber ich habe über analoge Dinge nur für ein rotes Wort geschrieben. Jetzt konzentrieren wir uns auf digitale Dinge. Die meisten modernen Steuerungen verfügen über leistungsstarke Peripheriegeräte, die eine Vielzahl von Funktionen bieten. In der Praxis werden diese Blöcke jedoch in jeder spezifischen Softwareentwicklung nicht vollständig, sondern nur teilweise verwendet. Und in PSoC wird anstelle einer Menge guter Programmlogik implementiert, ähnlich der Logik klassischer FPGAs. Dementsprechend ist es möglich, genau die Blöcke zu implementieren, die darauf benötigt werden, indem sie in die erforderlichen Modi aufgenommen werden. Und Ressourcen sollten nicht für nicht verwendete Modi ausgegeben werden, sondern für die Implementierung eigener Dinge.

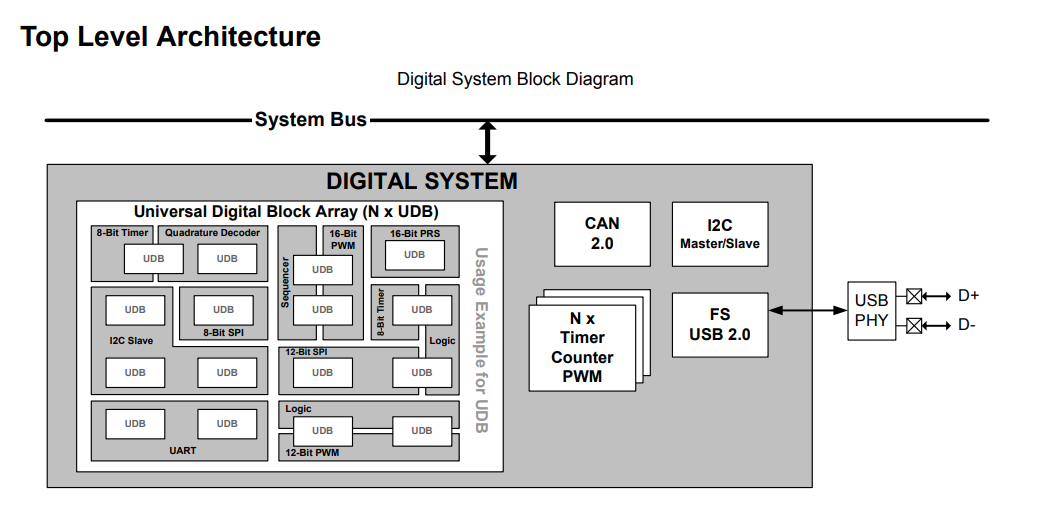

Und hier kommt es oft zu Missverständnissen. Viele Entwickler sind daran gewöhnt, dass es zwei Arten von programmierbaren integrierten Logikschaltungen (FPGAs) gibt: CPLD und FPGA. Daher glauben viele, die von PSoC gehört haben, dass es eine Art CPLD-Box gibt, die in Veriolg programmiert werden kann. In der Tat ja und nein. Eine bestimmte Anzahl von PLDs (ohne "C", nur PLDs) sind wirklich vorhanden, und Sie können sie wirklich auf Verilog programmieren. Aber wirklich, diese PLDs sind Teil von UDB-Blöcken. Und es ist UDB, die das Hauptelement der in PSoC implementierten programmierbaren Logik ist. Dieser Block ist äußerst originell und bietet dem Entwickler einfach die breitesten Möglichkeiten. Betrachten Sie die Abbildung aus der proprietären Dokumentation, in der das Wesentliche der Verwendung von UDB-Blöcken erläutert wird.

Da ich alles am Beispiel der PSoC 5LP-Familie studiert habe, werde ich die Dokumentation darauf übersetzen. Bevor Sie beginnen, möchte ich noch einige Worte zum Preis dieser Controller sagen. Wenn Sie zu Ali Express gehen und nach dem Steckbrett suchen, bekommen Sie ein trauriges Gefühl. Ehrlich gesagt sind sie im Vergleich zu STM32-DISCOVERY immer noch nichts, aber im Vergleich zu den Prototypen STM32F103C8T6 sind sie etwas teuer. Dies ist vor allem darauf zurückzuführen, dass Unternehmensmodelle immer nicht einen, sondern zwei solcher Controller haben. JTAG-Funktionen sind auf dem PSoC 5LP implementiert, auch wenn der Zielcontroller und PSoC 4 (letzterer hat normalerweise keinen USB-Anschluss).

Wenn wir den Preis durch zwei teilen, stellen wir immer noch fest, dass er höher ist als der des STM32F103, der im Prozessorkern ähnlich ist. Wenn wir jedoch von außen dem einfachsten STM32 selbst die einfachste CPLD hinzufügen, wird der Gesamtpreis zugunsten von PSoC ausfallen. Und wir werden die verlorenen Beine zur Verbindung dieser beiden Fälle hinzufügen (PSoC hat alle Verbindungen im Inneren). Und auch der Preis von Quadratzentimetern der Platte. Es stellt sich also heraus, dass PSoC wirklich nicht erforderlich ist, wenn Sie nur mit dem Prozessorkern arbeiten müssen. Wenn Sie einige Funktionen auf Firmware- oder Hardwareebene bringen möchten, benötigen Sie PSoC. Darauf wird das System billiger und einfacher herauskommen.

Tatsächlich habe ich eine manische Idee, Hardware-Unterstützung für den Kernel unseres RTOS MAX bereitzustellen. Zu diesem Zweck habe ich die Methodik für die Entwicklung von Bare-Metal-Anwendungen für Altera V SoC untersucht (leider stellte sich heraus, dass die Architekturfunktion dort so ist, dass das Betriebssystem verlangsamt werden kann, aber nicht beschleunigt werden kann - einzelne Anforderungen an die Hardware sind mit einer verrückten Latenz verbunden). Dafür begann ich PSoC zu beherrschen. Ich habe das Übertakten des Kernels nicht erreicht (es gibt nur allgemeine Gedanken), aber die Idee der UDB-Programmierung hat mir sehr gut gefallen. Natürlich bin ich jetzt daran interessiert, diese Idee auf die maximale Anzahl inländischer Programmierer zu übertragen. Daher fahren wir mit der Übersetzung des entsprechenden Teils der Cypress-eigenen Dokumentation zu UDB fort. Die Nummerierung der Kapitel und Abbildungen erfolgt gemäß Originaldokument.

Der allgemeine Inhalt des Zyklus „UDB. Was ist das? "

Teil 1. Einführung. Pld. (Aktueller Artikel)

Teil 2. Datenpfad.Teil 3. Datenpfad-FIFO.Teil 4. Datenpfad ALU.Teil 5. Datenpfad. Nützliche Kleinigkeiten.Teil 6. Management- und Statusmodul.Teil 7. Steuermodul für Timing und ResetTeil 8. Adressierung von UDBUDB. Was ist das Teil 1

21. Universelle digitale Blöcke

In diesem Kapitel werden wir untersuchen, wie Universal Digital Blocks (UDBs) die Entwicklung programmierbarer digitaler Peripheriefunktionen ermöglichen. Die UDB-Architektur schafft ein Gleichgewicht zwischen Granularität der Konfiguration und effizienter Implementierung. UDBs bestehen aus einer Kombination von nicht kommutierter Logik ähnlich einer programmierbaren Logikmatrix (PLM, englische PLD), strukturierter Logik (Betriebsmaschinen, im Folgenden als Datenpfad bezeichnet) und einem flexiblen Verfolgungsschema.

21.1 Funktionen

- Für eine optimale Flexibilität enthält jede UDB die folgenden Komponenten:

• 8-Bit-Datenpfad basierend auf ALU (Arithmetic and Logic Unit, ALU) mit 8-Befehls-Befehls-Repository, mehreren Registern und FIFO-Puffern;

• zwei PLDs mit jeweils 12 Eingängen, acht konjunktiven Begriffen (Product Terms, PT) und vier Makrozellenausgängen;

• Verwaltungs- und Statusregister;

• Module takten und zurücksetzen. - PSoC 5LP enthält ein Array mit einer Größe von bis zu 24 UDB.

- Flexible Ablaufverfolgung zwischen UDB-Array-Elementen.

- UDB-Elemente können geteilt oder verkettet werden, um größere Funktionen zu erstellen.

- Flexible Implementierung einer Reihe digitaler Funktionen, einschließlich Timer, Zähler, Impulsbreitenmodulatoren (einschließlich PWM mit Totbandgenerator), UART, I2C-Bus, SPI-Bus und CRC-Verifizierung / -Erzeugung.

21.2 Blockschaltbild

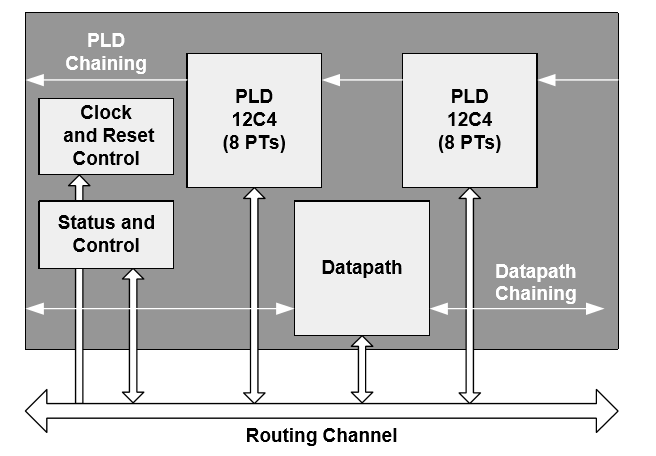

Abbildung 21-1 zeigt die UDB als Konstrukt, das zwei grundlegende logische Blöcke enthält: PLD, Datenpfad sowie die Steuerungs-, Status-, Takt- und Rücksetzfunktionen.

Abbildung 21-1. Blockschaltbild der UDB.

Abbildung 21-1. Blockschaltbild der UDB.21.3 Wie es funktioniert

Die Hauptkomponenten von UDB sind:

- PLD (2). Daten von Trace-Ressourcen werden den Eingängen dieser Blöcke zugeführt. Sie implementieren kombinatorische Logik und Datenfang, mit denen Sie Finite-State-Maschinen implementieren, die Operationen des Datenpfadblocks steuern, Eingabebedingungen konfigurieren und Ausgänge steuern können.

- Datenpfad. Dieser Block enthält eine dynamisch programmierbare ALU, vier Register, zwei FIFO-Puffer, Komparatoren und eine Bedingungserzeugung.

- Management und Status (Status und Kontrolle). Diese Module bieten einen Mechanismus für die Interaktion der Mikroprogramme des Zentralprozessors (CPU) und die Synchronisation mit UDB-Operationen. Steuerregister wirken auf interne Elemente und Statusregister lesen den Status externer Elemente.

- Clock and Reset Control Diese Module bieten eine Auswahl und Aktivierung des Timings sowie eine Auswahl zum Zurücksetzen innerhalb der UDB.

- Verkettungssignale. PLD und Datapath verfügen über Signale, mit denen Sie benachbarte Blöcke in einer Kette verketten können, um Funktionen mit höheren Bits zu erstellen.

- Kanal verfolgen UDBs sind über programmierbare Schaltmatrizen mit dem Trace-Kanal verbunden, um zwischen Blöcken innerhalb derselben UDB zu kommunizieren und mit anderen UDBs im Array zu kommunizieren.

- Systembusschnittstelle (Systembusschnittstelle). Alle Register und RAMs in jeder UDB werden auf den Systemadressraum projiziert, und der Zugriff auf sie kann über den Zentralprozessor oder über direkten Speicherzugriff (English Direct Memory Access, DMA) in Form von 8-Bit und 16-Bit erfolgen Daten.

21.3.1. Pld

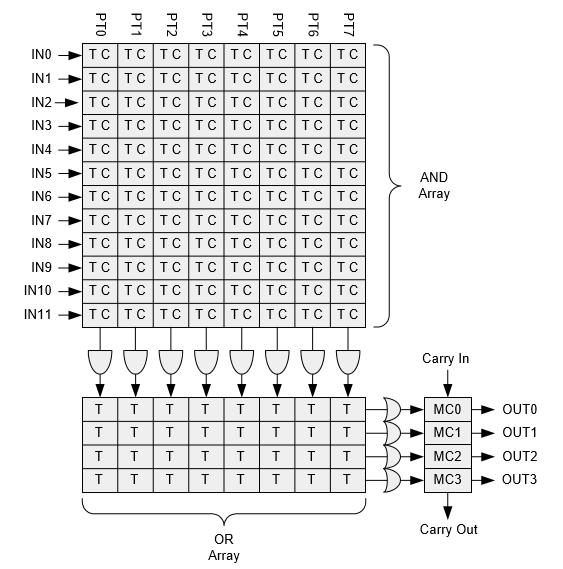

Jede UDB verfügt über zwei 12C4-PLDs. Mit den in Abbildung 21-1 gezeigten PLD-Blöcken können Zustandsmaschinen implementiert, E / A-Daten verarbeitet und Tabellenlogik erstellt werden (Eng. Lookup Table, LUT). Darüber hinaus kann PLD so konfiguriert werden, dass arithmetische Funktionen ausgeführt, die Datenpfadsequenz festgelegt und der Status generiert werden. Allgemeine Logik kann synthetisiert und auf PLD-Blöcke projiziert werden. Dieser Abschnitt bietet einen Überblick über die PLD-Architektur.

PLD verfügt über 12 Eingänge, die Informationen in 8 Konjunktivtermen in einem UND-Array übertragen. In jedem Konjunktivterm können Sie eine direkte (true, T) oder inverse (Komplement, C) Eingabe wählen. Die Ausgabe von Konjunktivtermen geht an die Eingabe des ODER-Arrays. Der Buchstabe 'C' in 12C4 zeigt an, dass die ODER-Terme für alle Eingaben konstant sind und jeder ODER-Eingang programmgesteuerten Zugriff auf jeden konjunktiven Term erhalten kann. Diese Struktur bietet maximale Flexibilität und stellt sicher, dass alle Ein- und Ausgänge verschoben werden können.

Abbildung 21-2. Die Struktur von PLD 12C4.

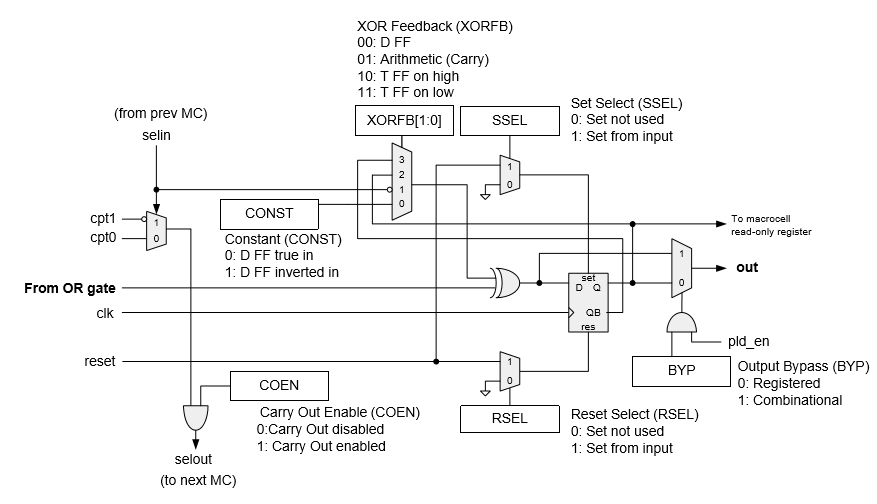

Abbildung 21-2. Die Struktur von PLD 12C4.21.3.1.1 Makro-PLD

Die Architektur der Makrozellen ist in Abbildung 21-3 dargestellt. Die Ausgabe steuert das Trace-Array und kann zwischengespeichert oder Raman sein. Zum Verriegeln wird ein D-Trigger mit direktem oder inversem Eingang oder ein T-Trigger mit hohem oder niedrigem Eingangspegel verwendet. Der Ausgangstrigger kann während der Initialisierung oder asynchron während des normalen Betriebs durch ein externes Signal vom Trace-Kanal gesetzt oder zurückgesetzt werden.

Abbildung 21-3. Macrocell-Architektur.Schreibgeschütztes PLD-Makrozellenregister

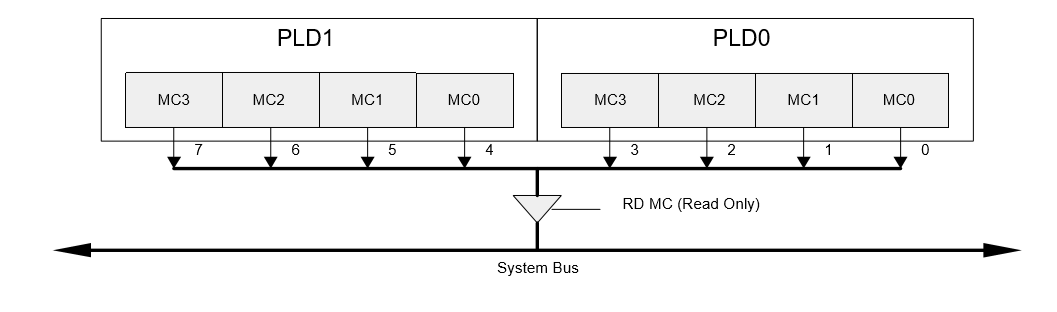

Abbildung 21-3. Macrocell-Architektur.Schreibgeschütztes PLD-MakrozellenregisterZusätzlich zur Steuerung des Trace-Arrays werden die Makrozellenausgänge beider PLDs in Form eines schreibgeschützten 8-Bit-Registers auf den Adressraum projiziert, auf das über die CPU oder DMA zugegriffen werden kann.

Abbildung 21-4. Das schreibgeschützte PLD-Makrozellenregister.

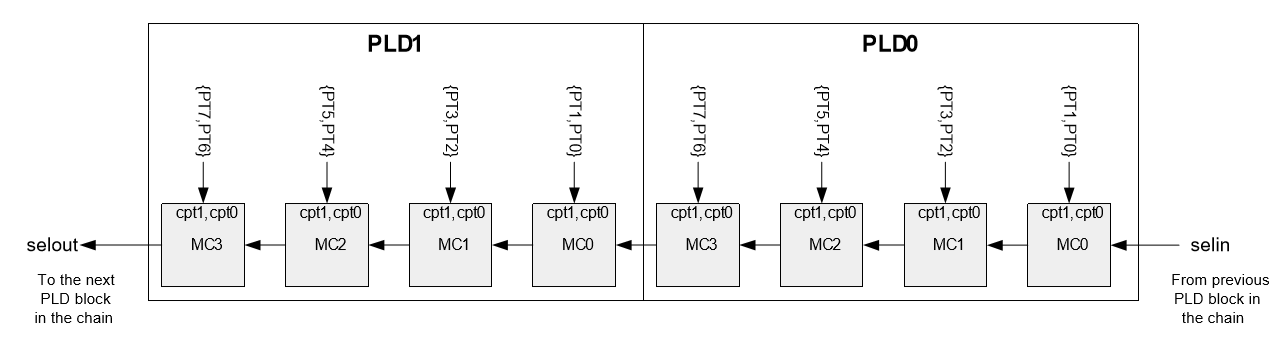

Abbildung 21-4. Das schreibgeschützte PLD-Makrozellenregister.21.3.1.2 Silbentrennungskette PLD

PLDs werden in der UDB-Adressierung miteinander verknüpft. Wie in Abbildung 21-5 gezeigt, wird der Eingang der Selin-Übertragskette von der vorherigen UDB über jede Makrozelle in beiden PLDs an die Schaltung weitergeleitet und dann als Ausgang der Selout-Übertragskette an die nächste UDB weitergeleitet. Um die effiziente Platzierung von arithmetischen Funktionen zu unterstützen, werden spezielle Konjunktivterme (PT) generiert, die in Makrozellen zusammen mit einer Silbentrennungskette verwendet werden.

Abbildung 21-5. PLD-Silbentrennungskette und spezielle konjunktive Termeingaben.

Abbildung 21-5. PLD-Silbentrennungskette und spezielle konjunktive Termeingaben.21.3.1.3 PLD-Konfiguration

Jede PLD erscheint vor der CPU oder dem DMA in Form eines RAM mit 16-Bit-Zugriff. Das UND-Array hat 12 × 8 × 2 Bits oder 24 Bytes zum Programmieren, und das ODER-Array hat 4 × 8 Bits oder 4 Bytes zum Programmieren. Zusätzlich hat jede Makrozelle ein Konfigurationsbyte, insgesamt 32 Konfigurationsbytes pro PLD. Da jede UDB 2 PLDs hat, beträgt die Gesamtkonfiguration jeder UDB 64 Bytes.

Das nächste Mal werden wir Operational Automata (Datenpfade) betrachten.