Wir betrachten UDB weiterhin basierend auf der Cypress-Dokumentation. Und dieses Mal werden wir Datapath, einen Betriebsautomaten, im Detail untersuchen.

Der allgemeine Inhalt des Zyklus „UDB. Was ist das? "

Teil 1. Einführung. Pld.Teil 2. Datenpfad. (Aktueller Artikel)

Teil 3. Datenpfad-FIFO.Teil 4. Datenpfad ALU.Teil 5. Datenpfad. Nützliche Kleinigkeiten.Teil 6. Management- und Statusmodul.Teil 7. Steuermodul für Timing und ResetTeil 8. Adressierung von UDB21.3.2 Betriebsmaschine (Datenpfad)

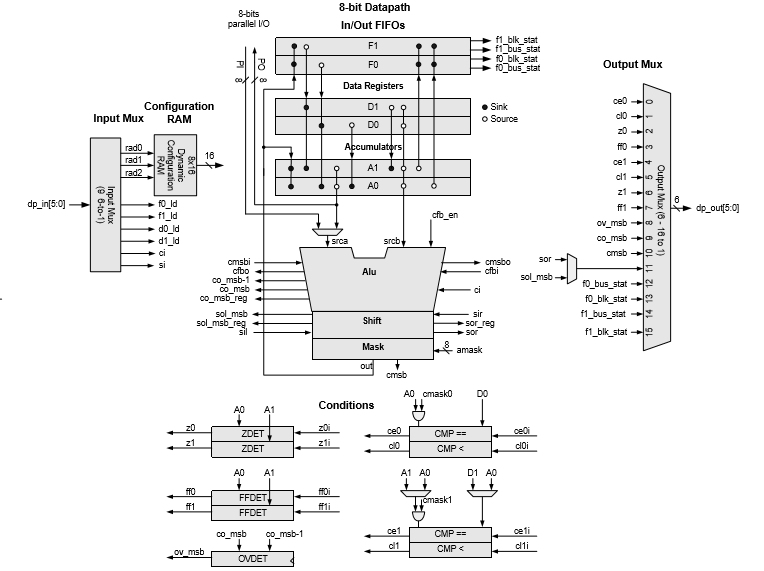

Der in Abbildung 21-6 gezeigte Datenpfad enthält eine 8-Bit-Einzelzyklus-ALU und den zugehörigen Vergleich und die Generierung von Bedingungsflags. Datenpfadblöcke benachbarter UDBs können miteinander verkettet werden, um die Bittiefe zu erhöhen. Der Datenpfad enthält einen kleinen dynamischen Konfigurations-RAM, der die in einem bestimmten Zyklus auszuführende Operation dynamisch auswählen kann.

Datapath ist optimiert, um typische eingebettete Funktionen wie Timer, Zähler, PWMs, PRS, CRC, Schieberegister und Totbandgeneratoren zu implementieren. Das Hinzufügen von Additions- und Subtraktionsfunktionen bietet Unterstützung für digitale Delta-Sigma-Operationen.

Abbildung 21-6. Datenpfad der obersten Ebene.

21.3.2.1 Übersicht

Die folgenden Kapitel bieten einen Überblick über die Hauptfunktionen von Datapath.

Dynamische KonfigurationDynamische Konfiguration - Die Möglichkeit, die Arbeit und die interne Kommunikation von Datapath in jedem Zyklus unter der Kontrolle eines Sequenzers zu ändern. Dies wird mithilfe des Konfigurationsspeichers (Konfigurations-RAM) implementiert, in dem acht eindeutige Konfigurationen gespeichert sind. Die Eingangsadresse dieses Speichers kann von jedem Block weitergeleitet werden, der mit Ablaufverfolgungsressourcen verbunden ist, normalerweise von der PLD-Logik, den E / A-Pins oder von anderen Datenpfaden.

AluALU kann acht Allzweckfunktionen ausführen: Inkrementieren, Dekrementieren, Addieren, Subtrahieren und Ausführen logischer Operationen AND, OR, XOR und PASS. Die Auswahl der Funktionen wird durch den Konfigurationsspeicher für jeden Zyklus bestimmt. Am ALU-Ausgang stehen unabhängige Verschiebungsoperationen (Links-, Rechts-, Halbbyte-Permutation) sowie Maskierungsoperationen zur Verfügung.

Bedingte KonstruktionenJeder Datenpfad verfügt über zwei bitweise maskierte Komparatoren, die so konfiguriert werden können, dass mehrere Datenpfad-Registereingaben als Argumente ausgewählt werden. Andere identifizierbare Bedingungen können alle Nullen, alle Einsen und Überlauf sein. Diese Bedingungen bilden die Hauptausgänge von Datapath und können an digitale Trace-Leitungen oder Eingänge anderer Funktionen weitergeleitet werden.

Eingebettetes CRC / PRSDatapath bietet integrierte Unterstützung für CRC-Einzelzyklusberechnungen und die Erzeugung von Pseudozufallssequenzen (Eng. Pseudo Random Sequence, PRS) mit einer bestimmten Bittiefe und einem generierenden Polynom. Um eine Bittiefe von mehr als 8 Bit zu erreichen, können Signale zwischen Datapath verkettet werden. Diese Funktion wird dynamisch gesteuert, dh sie kann mit anderen Funktionen abwechseln.

Benutzerdefinierte hohe BitnummerDie Nummer des höchstwertigen Bits (English Most Significant Bit, MSB) der arithmetischen Funktion und der Verschiebungsfunktion kann programmgesteuert eingestellt werden. Dies bietet Unterstützung für CRC / PRS-Funktionen variabler Länge und ermöglicht in Verbindung mit der Maskierung der ALU-Ausgabe die Implementierung von Timern beliebiger Länge, Zähler und Verschiebungsblöcke.

FIFO-Eingangs- / AusgangspufferJeder Datenpfad verfügt über zwei 4-Byte-FIFO-Puffer, von denen jeder als Eingangspuffer (CPU oder DMA schreibt Daten in FIFO, Datenpfad liest FIFO) oder als Ausgabepuffer (Datenpfad schreibt in FIFO und CPU oder DMA) konfiguriert werden kann liest daraus). Diese FIFO-Puffer erzeugen einen Status, der zur Interaktion mit Sequenzern, Interrupts oder DMA-Anforderungen weitergeleitet werden kann.

VerkettungDer Datenpfad kann so konfiguriert werden, dass Bedingungen und Signale in einer Kette mit benachbarten Datenpfaden verkettet werden. Shift-, Transfer-, Capture- und andere bedingte Signale können zu Ketten kombiniert werden, um arithmetische Funktionen mit höherer Bittiefe sowie Shift-Funktionen und CRC / PRS-Funktionen zu erstellen.

ZeitmultiplexIn Oversampling-Anwendungen oder wenn keine hohen Taktraten erforderlich sind, kann eine ALU in Datapath effektiv zwischen zwei Registersätzen und Bedingungsgeneratoren aufgeteilt werden. Die Ausgänge der ALU und des Schieberegisters sind zwischengespeichert und können in nachfolgenden Zyklen als Eingang verwendet werden. Beispiele für die Verwendung sind die Unterstützung von 16-Bit-Funktionen in einem (8-Bit-) Datenpfad oder das Abwechseln von CRC-Generierungsoperationen mit Datenverschiebungsoperationen.

DatenpfadeingabenDatapath verfügt über vier Arten von Eingängen: Konfiguration, Steuerung sowie Dateneingänge (seriell und parallel). Die Konfigurationseingänge wählen die RAM-Adresse der dynamischen Konfiguration aus. Die Steuereingänge laden die Datenregister vom FIFO und laden den Batterieausgang in den FIFO herunter. Serielle Dateneingänge umfassen Shift- und Carry-Eingänge. Über den parallelen Dateneingangsport können Sie bis zu 8 Datenbits von Trace-Ressourcen empfangen.

DatenpfadausgabenInsgesamt werden in Datapath 16 Signale generiert. Einige von ihnen sind bedingte Signale (zum Beispiel Vergleiche), andere sind Statussignale (zum Beispiel FIFO-Status) und der Rest sind Datensignale (zum Beispiel Schieberegisterausgang). Diese 16 Signale werden in 6 Datenpfadausgänge gemultiplext und zur Trace-Matrix geleitet. Standardmäßig sind die Ausgänge mit der Taktfrequenz synchronisiert, wodurch ein Pipelining mit einer Verzögerung von 1 Taktzyklus erstellt wird. Außerdem können ihre (Ausgänge) in den asynchronen (kombinatorischen) Modus geschaltet werden (siehe Anmerkungen des Übersetzers).

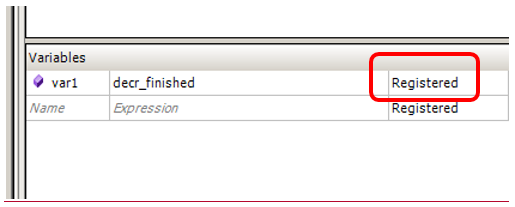

Anmerkung des ÜbersetzersIch habe lange nach dem Timing der Datapath-Ausgaben gesucht. Meine Erfahrung hat gezeigt, dass alles asynchron da ist. Es stellte sich heraus, dass dies nicht so sehr der Status der Ausgaben ist, sondern diese Editoreinstellung für darauf basierende Variablen. Dadurch wird der Editor gezwungen, den folgenden Verilog-Code zu generieren:

Dadurch wird der Editor gezwungen, den folgenden Verilog-Code zu generieren:/* ==================== Assignment of Registered Variables ==================== */ always @ (posedge clock) begin : register_assignments var1 <= (decr_finished); end

Wenn Sie in den kombinatorischen Modus wechseln Der Code wird folgendermaßen aussehen:

Der Code wird folgendermaßen aussehen: assign var1 = (decr_finished);

All dies gilt jedoch für Variablen, die aus Datenpfadausgaben generiert werden. Und die Ausgänge selbst sind immer asynchron. Und ihre Namen (in diesem Beispiel decr_finished ) können ohne Eingabe zusätzlicher Variablen verwendet werden.Datenpfad-ArbeitsregisterJedes Datenpfadmodul verfügt über sechs 8-Bit-Arbeitsregister. Die CPU oder der DMA hat Lese- und Schreibzugriff auf alle Register.

Tabelle 21-1Im nächsten Artikel werden wir uns mit FIFO befassen.