Wir übersetzen weiterhin die proprietäre Dokumentation von Cypress in UDB-Blöcke. Außerdem stimmt alles sehr gut überein. Um den

praktischen Artikel über UDB fortzusetzen

, müssen Sie FIFO verwenden, und im theoretischen Teil haben wir die genaue Beschreibung dieser

Artikel gefunden . Deshalb beginnen wir, sie im Detail zu studieren.

Der allgemeine Inhalt des Zyklus „UDB. Was ist das? "

Teil 1. Einführung. Pld.Teil 2. Datenpfad.Teil 3. Datenpfad-FIFO. (Aktueller Artikel)

Teil 4. Datenpfad ALU.Teil 5. Datenpfad. Nützliche Kleinigkeiten.Teil 6. Management- und Statusmodul.Teil 7. Steuermodul für Timing und ResetTeil 8. Adressierung von UDB21.3.2.2 Datenpfad-FIFO

FIFO-Modi und -Konfigurationen

Für jeden FIFO-Puffer stehen verschiedene Betriebsarten und Konfigurationen zur Verfügung:

Tabelle 21-2. FIFO-Modi und -Konfigurationen.

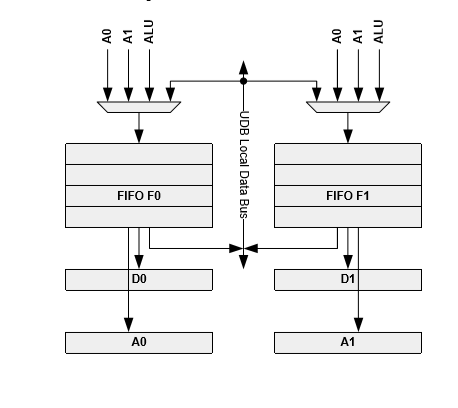

Abbildung 21-7 zeigt die möglichen Konfigurationsoptionen für das FIFO-Paar in Abhängigkeit von den jeweils ausgewählten Ein- / Ausgabemodi. Befindet sich ein FIFO im Eingangsmodus und der andere im Ausgangsmodus, erhalten wir die RX / TX-Konfiguration. Ein typisches Beispiel, bei dem eine solche Konfiguration erforderlich ist, ist der SPI-Bus-Controller. Die

Dual-Capture- Konfiguration (beide FIFOs sind für die Ausgabe konfiguriert) ermöglicht die unabhängige Erfassung des A0- und A1-Paares oder zwei unabhängige Erfassung der A0- oder A1-Register. Schließlich ist es im

Dual-Buffer- Modus (beide am Eingang) möglich, entweder ein Registerpaar oder zwei unabhängige Register zum Laden oder Vergleichen zu verwenden.

Abbildung 21-7. FIFO-Konfigurationen.

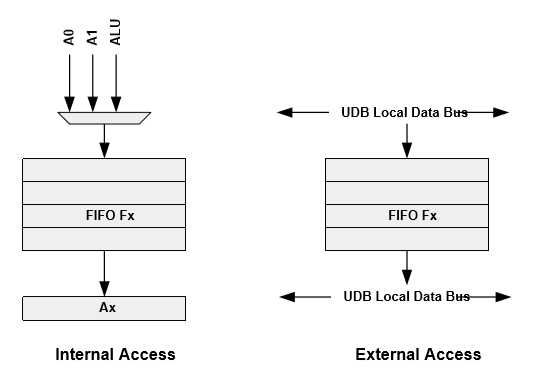

Abbildung 21-8 zeigt detailliert die Quellen und Empfänger für FIFO.

Abbildung 21-8. FIFO-Quellen und -Empfänger.

Wenn FIFO im Eingangspuffermodus arbeitet, ist die Quelle der Systembus und die Empfänger sind die Register Dx und Ax. Wenn Sie im Ausgangspuffermodus arbeiten, sind die Quellen die Ax- und ALU-Register, und der Empfänger ist der Systembus. Die Multiplexerauswahl wird statisch im UDB CFG15-Konfigurationsregister festgelegt, wie in der Tabelle für F0_INSEL [1: 0] oder F1_INSEL [1: 0] gezeigt:

Tabelle 21-3. Ein Satz von FIFO-Multiplexern im UDB-Konfigurationsregister.

FIFO-Status

Jeder FIFO erzeugt zwei Statussignale, "Bus" und "Block", die über den Datenpfad-Ausgangsmultiplexer an die UDB-Trace-Ressourcen übertragen werden. Der Busstatus kann verwendet werden, um ein DMA-Lesen / Schreiben in den FIFO zu unterbrechen oder anzufordern. Der Blockzustand soll in erster Linie den FIFO-Zustand an interne UDB-Entitäten übergeben. Der Zweck der Statusbits hängt von der konfigurierten Richtung (Fx_INSEL [1: 0]) und den FIFO-Pegelbits ab. FIFO-Pegelbits (Fx_LVL) werden im Hilfssteuerregister im Arbeitsregisterraum gesetzt. Statusoptionen werden in der folgenden Tabelle angezeigt:

Tabelle 21-4. FIFO-Statusoptionen.

FIFO-Arbeitsillustration

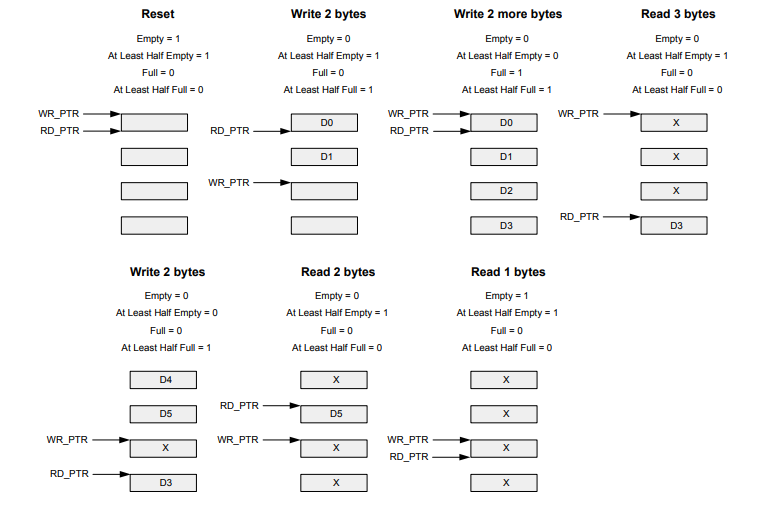

Abbildung 21-9 zeigt eine typische Abfolge von Lesen und Schreiben sowie die Generierung von Status, die diesen Vorgängen zugeordnet sind. In der Abbildung erfolgt das Lesen und Schreiben zu unterschiedlichen Zeiten, sie können jedoch gleichzeitig ausgeführt werden.

Abbildung 21-9 Betrieb der FIFO-Empfänger

FIFO-Schnellmodus (FIFO FAST)

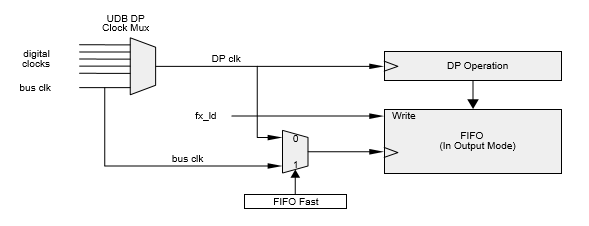

Wenn sich das FIFO im Ausgangspuffermodus befindet, verwendet die FIFO-Startoperation typischerweise die Taktfrequenz des ausgewählten Datenpfads, um das Schreibsignal zu takten. Wie in Abbildung 21-10 dargestellt, können Sie bei Auswahl des FIFO-Schnellmodus (FIFO FAST) die Busfrequenz für diesen bestimmten Vorgang auswählen. In Verbindung mit dem

Level / Edge = Edge- Modus reduziert dieser Vorgang die Übertragungsverzögerung von der Batterie zum FIFO von der Datenpfad-Taktperiode zur Bustaktperiode, da die Busfrequenz viel höher sein kann. Dadurch kann die CPU oder der DMA das empfangene FIFO-Ergebnis mit minimaler Verzögerung lesen.

Wie in Abbildung 21-10 dargestellt, wird der Schnellstartvorgang unabhängig vom aktuellen Datenpfadtakt ausgeführt. Die Verwendung der Bustaktrate kann jedoch den Stromverbrauch erhöhen.

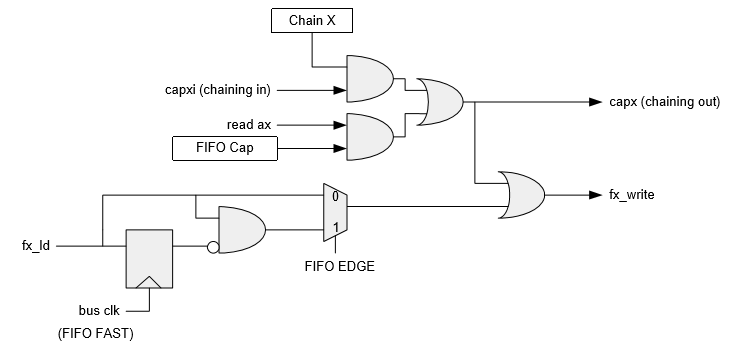

Abbildung 21-10. FIFO-Empfänger mit schneller Konfiguration.

FIFO Edge / Level-Aufnahmemodus (Differential / Level)

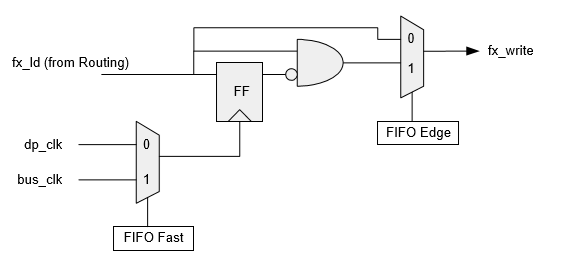

Im FIFO von Datapath gibt es zwei Aufnahmemodi. Im ersten Modus werden Daten synchron von den Batterien zum FIFO übertragen. Das Steuersignal dieses Datensatzes (FX_LD) wird normalerweise von einer Zustandsmaschine oder von einer Bedingung generiert, die mit der Datenpfad-Taktung synchronisiert ist. Das Schreiben in den FIFO wird in jedem Zyklus ausgeführt, in dem das Eingangslaststeuersignal '1' ist. Im zweiten Modus wird FIFO verwendet, um Batteriewerte als Reaktion auf eine positive Flanke des FX_LD-Signals zu erfassen. In diesem Modus ist das Signalformat des Signals beliebig (seine Periode muss jedoch mindestens einem Datenpfad-Taktzyklus entsprechen). Ein Beispiel für diesen Modus ist die Erfassung des Batteriewertes unter Verwendung des Eingangs des externen Fußes als Auslöser. Eine Einschränkung dieses Modus besteht darin, dass der Eingabeparameter mindestens einen Zyklus auf den Wert '0' zurückkehren muss, bevor eine weitere positive Differenz erkannt wird.

Abbildung 21-11 zeigt die Implementierung des Differentialerkennungsmodus am Eingang FX_LD. Der Modus beider FIFOs in der UDB wird durch dasselbe Bit gesteuert, wodurch diese Option umgeschaltet wird. Es ist zu beachten, dass die Differentialerkennung mit einer Frequenz getaktet wird, die der Frequenz des ausgewählten FIFO entspricht.

Abbildung 21-11. Differentialerkennung für interne FIFO-Aufzeichnungsempfänger.

FIFO-Software-Erfassungsmodus

Eine häufige und wichtige Anforderung besteht darin, dass CPU und DMA den Inhalt der Batterie während des normalen Betriebs zuverlässig lesen können. Dies erfolgt mithilfe der Softwareerfassung und wird mithilfe des FIFO-Cap-Konfigurationsbits aktiviert. Dieses Bit gilt für beide FIFOs in der UDB, funktioniert jedoch nur, wenn sich das FIFO im Ausgabepuffermodus befindet. Bei Verwendung der Softwareerfassung muss F0 von A0 und F1 von A1 lesen.

Wie in Abbildung 21-12 gezeigt, leitet das Lesen der Batterie das Schreiben von der Batterie in den FIFO ein. Das Signal ist in einer Kette verknüpft, sodass beim gleichzeitigen Lesen eines bestimmten Bytes die Batteriewerte aller UDBs in der Kette erfasst werden. Dadurch kann der 8-Bit-Prozessor 16 Bit oder mehr gleichzeitig erfolgreich lesen. Daten, die beim Lesen der Batterie zurückgegeben werden, sollten ignoriert werden, und der erfasste Wert kann sofort vom FIFO gelesen werden.

Das verfolgte FX_LD-Signal, das die FIFO-Last erzeugt, wird zusammen mit dem Programmerfassungssignal an den ODER-Term gesendet. Wenn die Hardware- und Softwareerfassung gleichzeitig verwendet wird, kann das Ergebnis unvorhersehbar sein. In der Regel sollten sich diese Funktionen gegenseitig ausschließen. Die Erfassung von Hardware und Software kann jedoch unter den folgenden Bedingungen gleichzeitig verwendet werden:

- Der FIFO-Erfassungstaktmodus ist auf FIFO SCHNELL eingestellt.

- Der FIFO-Aufzeichnungsmodus ist auf FIFO EDGE eingestellt.

Unter den oben beschriebenen Bedingungen funktionieren Hardware- und Software-Erfassungen im Wesentlichen gleich, und während eines Bustaktzyklus kann jedes dieser Signale eine Erfassung auslösen.

Es wird außerdem empfohlen, das Ziel-FIFO im Programmcode (ACTL-Register) zu löschen, bevor die Programmerfassung beginnt. Dank dessen werden die FIFO-Lese- und Schreibzeiger auf einen bekannten Zustand gesetzt.

Abbildung 21-12. Software Capture-Konfiguration.

Anmerkung des Übersetzers:

Ich konnte die Bedeutung dieses Abschnitts lange Zeit nicht verstehen. Dann war ich mir lange sicher, dass der Abschnitt für PSoC3 geschrieben wurde, dessen 8-Bit-Kern nicht mehr als Byte zugreifen kann. Beim Erstellen des achten Teils der Übersetzung stellte sich jedoch heraus, dass selbst in PSoC5LP für alle 32-Bit-ARM-Prozessorkerne der Zugriff auf die funktionierenden UDB-Register entweder im 8-Bit- oder im 16-Bit-Modus erfolgen kann. Nach dem Dokument zu urteilen, nicht mehr. Hier bietet sich die beschriebene Funktionalität an.

FIFO-Kontrollbits

Das Hilfssteuerregister, mit dem der FIFO während des normalen Betriebs gesteuert werden kann, enthält 4 Bits.

Die FIFO0-CLR- und FIFO1-CLR-Bits werden zum Zurücksetzen oder Löschen von FIFOs verwendet. Wenn einem dieser Bits der Wert '1' zugewiesen wird, wird der zugehörige FIFO zurückgesetzt. Das Bit muss auf seinen ursprünglichen Wert ('0') zurückgesetzt werden, damit das FIFO weiterarbeiten kann. Wenn der Bitwert gleich eins bleibt, wird das entsprechende FIFO deaktiviert und arbeitet als Einzelbytepuffer ohne Status. Daten können in FIFO geschrieben werden, Daten sind sofort lesbar und können jederzeit überschrieben werden. Die Datenrichtung mit den FX INSEL-Konfigurationsbits [1: 0] kann weiterhin gesetzt werden.

Die FIFO0-LVL- und FIFO1-LVL-Bits bestimmen den Pegel, auf dem FIFO das Statusbit

"Bus" spannt (wenn der Bus in FIFO liest oder schreibt). Das heißt, der Status des

"Bus" -Status hängt von der angegebenen Richtung ab, wie in der folgenden Tabelle gezeigt.

Tabelle 21-5. FIFO Level Control Bits

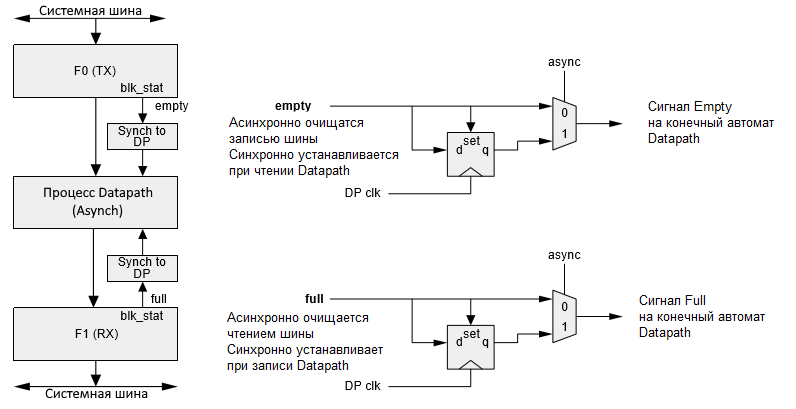

FIFO-Asynchronbetrieb

Abbildung 21-13 zeigt das Prinzip des asynchronen FIFO-Betriebs. Stellen Sie sich als Beispiel vor, dass F0 im Eingangspuffermodus und F1 im Ausgangspuffermodus arbeitet, was eine typische Konfiguration von TX- und RX-Registern ist.

Abbildung 21-13. Asynchrone FIFO-Operation.

Auf der TX-Seite verwendet die Datenpfad-Zustandsmaschine das

Leer- Flag, um festzustellen, ob Bytes zum Empfangen verfügbar sind. Der Leerwert wird synchron mit der Datapath-Zustandsmaschine festgelegt und aufgrund des Schreibens vom Bus asynchron gelöscht. Nach der Reinigung wird der Status erneut mit der Datapath-Zustandsmaschine synchronisiert.

Auf der RX-Seite verwendet die RX-Zustandsmaschine

Full , um zu bestimmen, ob freier Speicherplatz zum Schreiben in das FIFO vorhanden ist. Der Wert "

Voll" wird synchron mit der Datenpfad-Zustandsmaschine eingestellt und aufgrund des Lesens durch den Bus asynchron gelöscht. Nach der Reinigung wird der Status erneut mit der Datapath-Zustandsmaschine synchronisiert.

Ein FIFO-ASYNCH-Bit wird verwendet, um diese Synchronisationsmethode zu aktivieren. Nach der Aktivierung wird diese Methode auf beide FIFOs angewendet.

Dies gilt nur für den

Blockstatus , da davon ausgegangen wird, dass der

Busstatus natürlich durch den Interrupt-Prozess synchronisiert wird.

Tabelle 21-6.

Blockieren Sie die FIFO-Statussynchronisationsoptionen.

FIFO-Überlauf während des Betriebs

Für die sichere Implementierung interner (Datenpfad) und externer (CPU oder DMA) Lese- und Schreibvorgänge sollten FIFO-Statussignale verwendet werden. Es gibt keinen eingebauten Schutz gegen Entleerung und Überlauf. Wenn der FIFO voll ist und nachfolgende Schreibvorgänge ausgeführt werden (Überlauf), überschreiben die neuen Daten den Anfang des FIFO (die aktuell ausgegebenen Daten sind die nächsten in der Lesewarteschlange). Wenn der FIFO leer ist und nachfolgende Lesevorgänge ausgeführt werden (Entleeren oder Entleeren), ist der Lesewert undefiniert. FIFO-Zeiger bleiben unabhängig von Unterlauf und Überlauf genau.

FIFO Clock Inversion

Jedes FIFO hat ein Steuerbit Fx CK INV, das für die Polarität des Takt-FIFO in Bezug auf die Polarität des Taktdatenpfads verantwortlich ist. Standardmäßig arbeitet FIFO mit der gleichen Polarität wie die Datenpfad-Taktung. Wenn dieses Bit 1 ist, arbeitet der FIFO relativ zum Datenpfad mit umgekehrter Polarität. Dies bietet Protokollunterstützung für den Datenaustausch an beiden Fronten, z. B. SPI.

Dynamische FIFO-Steuerung

Typischerweise werden FIFOs statisch entweder im Eingangspuffermodus oder im Ausgangspuffermodus konfiguriert. Alternativ kann jeder FIFO so konfiguriert werden, dass er in einem Modus arbeitet, in dem die Richtung dynamisch gesteuert wird (unter dem Einfluss externer Signale). Ein Konfigurationsbit pro FIFO (Fx DYN) ist für die Aktivierung dieses Modus verantwortlich. Abbildung 21-14 zeigt die im dynamischen FIFO-Modus verfügbaren Konfigurationen.

Abbildung 21-14. Dynamischer FIFO-Modus.

Im internen Zugriffsmodus kann Datapath in FIFO lesen und schreiben. In dieser Konfiguration müssen die Fx INSEL-Bits auf 1 gesetzt werden, um die Quelle der Schreiboperationen im FIFO auszuwählen. Fx INSEL = 0 (CPU-Busquelle) ist in diesem Modus falsch, es können nur die Werte 1, 2 oder 3 (A0, A1 oder ALU) angenommen werden ) Es ist anzumerken, dass das Lesen nur Zugriff auf die entsprechende Batterie hat, die Richtung der Datenregister in diesem Modus ist nicht verfügbar.

Im externen Zugriffsmodus kann die CPU oder der DMA entweder lesen oder in den FIFO schreiben.

Die Konfiguration wechselt dynamisch zwischen externem und internem Zugriff, indem Signale von Datapath weitergeleitet werden. Hierzu werden die Eingangssignale Datapath d0_load und d1_load verwendet. Es ist anzumerken, dass im dynamischen Steuermodus d0_load und d1_load nicht für ihre normale Verwendung verfügbar sind, wenn die Register D0 / D1 von F0 / F1 geladen werden. Dx_load-Signale können durch jedes Trace-Signal einschließlich Konstanten ausgelöst werden.

Stellen Sie sich ein Beispiel vor, in dem die CPU oder der DMA beginnend mit dem externen Zugriff (dx_load == 1) ein oder mehrere Datenbytes in den FIFO schreiben können. Beim Umschalten auf internen Zugriff (dx_load == 0) kann Datapath dann Operationen an den Daten ausführen. Danach kann die CPU oder der DMA beim Umschalten auf externen Zugriff das Ergebnis der Berechnungen lesen.

Da Fx INSEL immer 01, 10 oder 11 (A0, A1 oder ALU) sein sollte, was im normalen Betrieb dem „Ausgangspuffermodus“ entspricht, haben die FIFO-Statussignale die folgenden Definitionen (abhängig vom Fx LVL-Parameter):

Tabelle 21-7. FIFO-Status.

Da sowohl Datapath als auch die CPU aus FIFOs schreiben und lesen können, werden diese Signale nicht mehr als Block- und Busstatus betrachtet. Das Signal blk_stat wird für den Schreibstatus und das Signal bus_stat für den Lesestatus verwendet

21.3.2.3 FIFO-Status

Es gibt vier FIFO-Statussignale, zwei für jedes FIFO: fifo0_bus_stat, fifo0_blk_stat, fifo1_bus_stat und fifo1_blk_stat. Die Bedeutung dieser Signale hängt von der Richtung des jeweiligen FIFO ab, die durch die statische Konfiguration bestimmt wird. Der FIFO-Status wird ausführlich in Abschnitt

21.3.2.2 Datenpfad-FIFO beschrieben .

Im nächsten Teil werden wir mit der Analyse der Arithmetic Logic Unit (ALU) fortfahren.