Wie beim letzten Mal versprochen, beginnen wir mit einer detaillierten Analyse der Arithmetik- und Logikeinheit (ALU).

Der allgemeine Inhalt des Zyklus „UDB. Was ist das? "

Teil 1. Einführung. Pld.Teil 2. Datenpfad.Teil 3. Datenpfad-FIFO.Teil 4. Datenpfad ALU. (Aktueller Artikel)

Teil 5. Datenpfad. Nützliche Kleinigkeiten.Teil 6. Management- und Statusmodul.Teil 7. Steuermodul für Timing und ResetTeil 8. Adressierung von UDB21.3.2.4 Datenpfad-ALU

Der ALU-Kern besteht aus drei unabhängigen programmierbaren 8-Bit-Funktionen: einem Arithmetik- / Logikblock, einem Schieberegisterblock und einem Maskenüberlagerungsblock.

Arithmetische und logische Operationen

Die mithilfe des Konfigurations-RAM dynamisch ausgewählten ALU-Funktionen sind in der folgenden Tabelle aufgeführt.

Tabelle 21-8. ALU-Funktionen

Tragen Sie in

Carry-In wird in arithmetischen Operationen verwendet. Wie in Tabelle 21-9 gezeigt, gibt es für bestimmte Funktionen Standard-Übertragswerte.

Tabelle 21-9. Funktionen übertragen.

Zusätzlich zu diesen regulären arithmetischen Anwendungen gibt es drei weitere Optionen für die Verwendung der Silbentrennung. Die CI SELA- und CI SELB-Bits legen die Regeln für die Verwendung der Übertragseingabe für jede Messung fest. Der RAM für die dynamische Konfiguration wählt bei jedem Zyklus die Konfiguration A oder B aus. Die Parameter sind in Tabelle 21-10 aufgeführt.

Tabelle 21-10. Zusätzliche Funktionen Carry In.

Wenn ein Übertrag verwendet wird, wird er in einer Reihe von Funktionen verwendet, wie in Tabelle 21-11 gezeigt. Bitte beachten Sie, dass für Dekrementierungs- und Einheitensubtraktionsfunktionen der aktive Übertragungspegel niedrig (invers) ist.

Tabelle 21-11. Verfolgte Carry-In-Funktionen.

Durchführen

Ausführen - optionaler Datenpfadausgang, der auf der Grundlage eines statisch festgelegten hohen Bits gebildet wird. Der Wert kann über die Kette an die Übertragungseingabe an einen älteren Block übergeben werden. Beachten Sie, dass bei Dekrement- und Subtraktionsfunktionen die Ausführung invertiert ist.

Tabelle 21-12. Eigenschaften Ausführen.

Transferstruktur

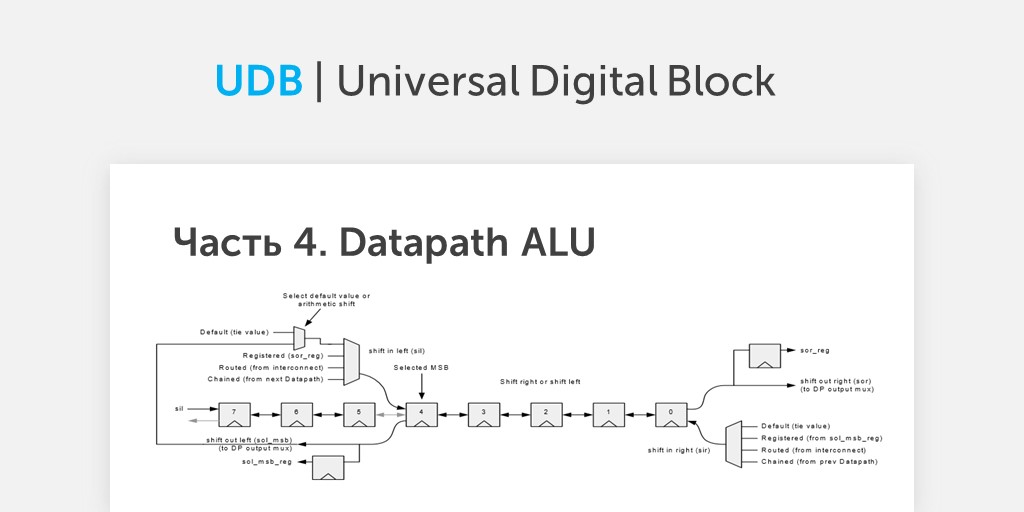

Die Parameter für die Eingabe und Auswahl des höchstwertigen Bits für die Erzeugung

der Ausführung sind in Abbildung 21-15 dargestellt. Die zwischengespeicherten

Übertragswerte können als

Übertrag für nachfolgende arithmetische Operationen verwendet werden. Diese Funktion kann verwendet werden, um Funktionen mit höherer Kapazität mithilfe von Zyklen zu implementieren.

Abbildung 21-15. Übertragungsvorgang.

Abbildung 21-15. Übertragungsvorgang.Schaltbetrieb

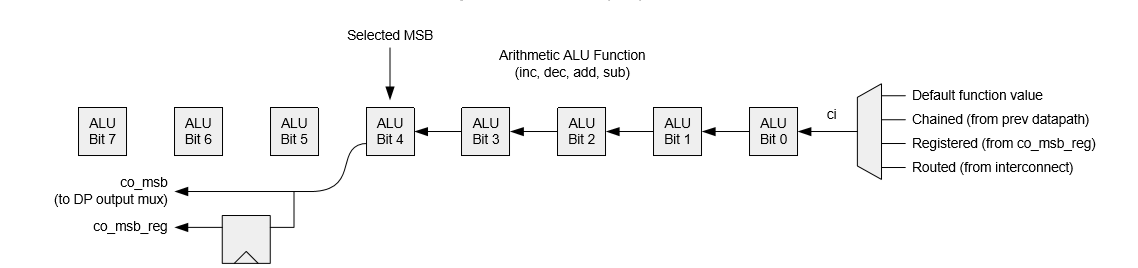

Der Schaltvorgang erfolgt unabhängig vom Betrieb der ALU gemäß Tabelle 21-13.

Tabelle 21-13. Funktionen des Schaltvorgangs.

Der Ausgabewert der Verschiebungsoperation wird mit Datapath ausgegeben. Die Ausgänge zum Verschieben nach rechts (

sor ) und nach links (

sol_msb ) sind mit den gleichen Bits

konfiguriert . Das statische Konfigurationsbit (SHIFT SEL im Register CFG15) bestimmt, welcher Shift-Ausgang als Datenpfad-Ausgang verwendet wird. In Abwesenheit einer Verschiebung werden die Signale

sor und

sol_msb als LSB bzw. MSB der ALU-Funktion definiert.

Die Konfigurationsbits SI SELA und SI SELB bestimmen den Datenversatz für die angegebene Operation. Der dynamische Konfigurations-RAM wählt die Konfiguration A oder B für jeden Taktzyklus aus. Pushed-Daten werden nur beim Verschieben nach links und rechts verwendet. Diese Eingabe wird nicht beim Überspringen und Neuanordnen von Halbbytes verwendet. Die ausgewählten Werte und Anwendungsfälle beziehen sich sowohl auf eine Rechtsverschiebung als auch auf eine Linksverschiebung und sind in Tabelle 21-14 aufgeführt.

Tabelle 21-14. Funktionsverschiebung

Die Ausgabe beim Verschieben nach links wird von dem als hoch angegebenen Bit übernommen. Bei einer Verschiebung nach rechts werden die Eingabedaten von der ausgewählten Senior-Position (MSB) verschoben. Der Ausgang ist selbst beim Verschieben nach links und beim Verschieben nach rechts verriegelt und kann für den nächsten Takt verwendet werden. Diese Funktion kann verwendet werden, um eine Verschiebung größerer Kapazität in mehreren Zyklen zu implementieren.

Abbildung 21-16. Schaltbetrieb.

Abbildung 21-16. Schaltbetrieb.Es ist anzumerken, dass die durch Auswahl von MSB isolierten Bits immer noch verschoben sind. In dem gezeigten Beispiel wird Bit 7 immer noch zu sil verschoben, wenn es nach rechts verschoben wird, und Bit 5 wird zu Bit 4 verschoben, wenn es nach links verschoben wird. Das Ausgangsbit (rechts oder links) einer isolierten Gruppe geht verloren.

ALU-Masken-Overlay-Operation

Das 8-Bit-Maskenregister im statischen Raum der UDB-Konfigurationsregister definiert die Maskierungsoperation. Bei dieser Operation wird dem ALU-Ausgang eine Maske (UND-Operation) mit dem Wert dieses Registers überlagert. Eine typische Verwendung der ALU-Maskierungsoperation ist die Implementierung autonomer Zeitgeber und Zähler mit einer Auflösung, die ein Vielfaches einer Zweierpotenz ist.

21.3.2.5. Datenpfadeingänge und Multiplexing

Wie in Tabelle 21-15 gezeigt, verfügt jeder Datenpfad über 9 Eingänge, einschließlich 6 Eingänge aus der Kanalverfolgung. Dazu gehören die Konfigurationsadressen von RAM, FIFO, Steuersignale zum Laden von Datenregistern sowie das Verschieben und Übertragen von Dateneingaben.

Tabelle 24-15. Datenpfadeingaben

Wie in Abbildung 21-17 dargestellt, verfügt jeder Eingang über einen 6-in-1-Multiplexer. Daher sind alle Eingänge austauschbar. Eingaben werden auf zwei Arten verarbeitet: entweder nach Pegel oder nach Differential. Die Adresse im RAM der dynamischen Konfiguration sowie die Verschiebungs- und Datenwerte sind abhängig vom Pegel. FIFO- und Laderegister-Datensignale reagieren empfindlich auf Unterschiede.

Abbildung 21-17. Datenpfad-Eingangssignale.

Abbildung 21-17. Datenpfad-Eingangssignale.Im nächsten Artikel werden wir uns mit einer Überprüfung nützlicher kleiner Dinge befassen.